# Architecture Fault Modeling and Analysis with the Error Model Annex, Version 2

Peter Feiler John Hudak Julien Delange David P. Gluch

June 2016

SPECIAL REPORT CMU/SEI-2016-TR-009

**Software Solutions Division**

Distribution Statement A: Approved for Public Release; Distribution is Unlimited

http://www.sei.cmu.edu

Copyright 2016 Carnegie Mellon University

This material is based upon work funded and supported by the Department of Defense under Contract No. FA8721-05-C-0003 with Carnegie Mellon University for the operation of the Software Engineering Institute, a federally funded research and development center.

Any opinions, findings and conclusions or recommendations expressed in this material are those of the author(s) and do not necessarily reflect the views of the United States Department of Defense.

This report was prepared for the SEI Administrative Agent AFLCMC/PZM 20 Schilling Circle, Bldg 1305, 3rd floor Hanscom AFB, MA 01731-2125

NO WARRANTY. THIS CARNEGIE MELLON UNIVERSITY AND SOFTWARE ENGINEERING INSTITUTE MATERIAL IS FURNISHED ON AN "AS-IS" BASIS. CARNEGIE MELLON UNIVERSITY MAKES NO WARRANTIES OF ANY KIND, EITHER EXPRESSED OR IMPLIED, AS TO ANY MATTER INCLUDING, BUT NOT LIMITED TO, WARRANTY OF FITNESS FOR PURPOSE OR MERCHANTABILITY, EXCLUSIVITY, OR RESULTS OBTAINED FROM USE OF THE MATERIAL. CARNEGIE MELLON UNIVERSITY DOES NOT MAKE ANY WARRANTY OF ANY KIND WITH RESPECT TO FREEDOM FROM PATENT, TRADEMARK, OR COPYRIGHT INFRINGEMENT.

[Distribution Statement A] This material has been approved for public release and unlimited distribution. Please see Copyright notice for non-US Government use and distribution.

Internal use:\* Permission to reproduce this material and to prepare derivative works from this material for internal use is granted, provided the copyright and "No Warranty" statements are included with all reproductions and derivative works.

External use:\* This material may be reproduced in its entirety, without modification, and freely distributed in written or electronic form without requesting formal permission. Permission is required for any other external and/or commercial use. Requests for permission should be directed to the Software Engineering Institute at permission@sei.cmu.edu.

\* These restrictions do not apply to U.S. government entities.

Carnegie Mellon® is registered in the U.S. Patent and Trademark Office by Carnegie Mellon University.

DM-0003594

# **Table of Contents**

| Exec | utive                                           | Summa   | ary                                                            | viii |

|------|-------------------------------------------------|---------|----------------------------------------------------------------|------|

| Abst | ract                                            |         |                                                                | x    |

| 1    | Intro                                           | duction | 1                                                              | 1    |

|      | 1.1                                             | Backg   | round                                                          | 1    |

|      | 1.2                                             | •       | System Integration and Architecture Fault Modeling             | 2    |

|      | 1.3                                             |         | age Concepts in EMV2                                           | 4    |

|      |                                                 | 1.3.1   | Fault Propagation Across the System                            | 5    |

|      |                                                 | 1.3.2   | Fault and Recovery Behavior of Components                      | 6    |

|      |                                                 |         | Compositional Abstraction of Fault Models                      | 7    |

|      | 1.4                                             |         | and Concepts                                                   | 8    |

|      | 1.5                                             |         | er's Guide                                                     | 11   |

| 2    | Error Model Libraries and Subclause Annotations |         |                                                                |      |

|      | 2.1                                             | Error N | Model Library                                                  | 13   |

|      |                                                 | 2.1.1   | Role of an Error Model Library                                 | 13   |

|      |                                                 | 2.1.2   | Using the Error Model Library                                  | 13   |

|      | 2.2                                             | Error N | Model Subclause                                                | 14   |

|      |                                                 | 2.2.1   | Role of an Error Model Subclause                               | 14   |

|      |                                                 | 2.2.2   | Using the Error Model Subclause                                | 14   |

| 3    | Error Types and Common Type Ontology            |         |                                                                | 16   |

|      | 3.1                                             |         | Гуреs and Type Sets                                            | 16   |

|      |                                                 |         | Role of Error Types and Type Sets                              | 16   |

|      |                                                 |         | Using Error Types and Type Sets                                | 17   |

|      |                                                 |         | Observations                                                   | 18   |

|      | 3.2                                             |         | ble Error Type Libraries and Aliases                           | 19   |

|      |                                                 |         | Role of Error Type Libraries and Aliases                       | 19   |

|      |                                                 | 3.2.2   | 3 , ,,                                                         | 19   |

|      |                                                 | -       | Observations                                                   | 20   |

|      | 3.3                                             |         | Products and Type Hierarchy                                    | 21   |

|      |                                                 |         | Roles of Type Products and Type Hierarchies                    | 21   |

|      |                                                 | 3.3.2   | 3 31                                                           | 21   |

|      |                                                 |         | Observations                                                   | 22   |

|      | 3.4                                             |         | tology of Common Error Propagation Types                       | 22   |

|      |                                                 | 3.4.1   | Role of the Ontology of Error Types                            | 22   |

|      |                                                 | 3.4.2   |                                                                | 23   |

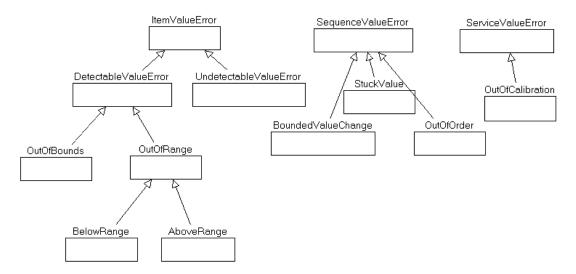

|      |                                                 | 3.4.3   | Value-Related Errors                                           | 24   |

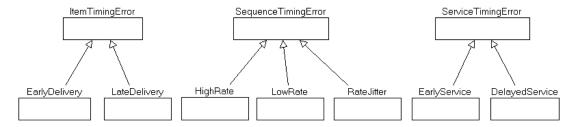

|      |                                                 | 3.4.4   | Timing-Related Errors                                          | 26   |

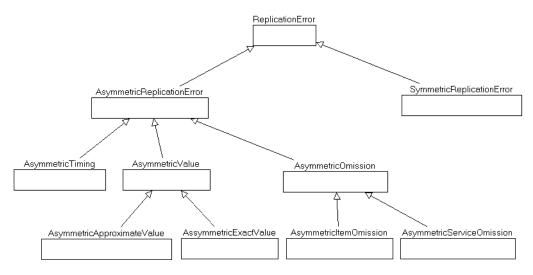

|      |                                                 | 3.4.5   | Replication-Related Errors                                     | 27   |

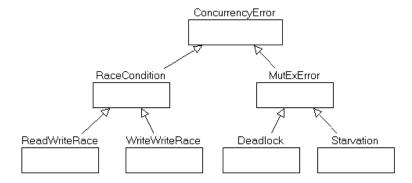

|      |                                                 | 3.4.6   | Concurrency-Related Errors                                     | 28   |

|      |                                                 | 3.4.7   | Authorization- and Authentication-Related Errors               | 28   |

|      |                                                 | 3.4.8   | Using the Ontology as an Error Type Library Named ErrorLibrary | 29   |

| 4    | Error Sources and Their Impact                  |         |                                                                | 30   |

|      | 4.1                                             |         | Propagation Paths                                              | 30   |

|      |                                                 | 4.1.1   | Role of Error Propagation Paths                                | 30   |

|      |                                                 | 4.1.2   | Using Error Propagation Paths                                  | 30   |

|      |                                                 | 4.1.3   | Observations                                                   | 32   |

|      | 4.2                                             | Outgoi  | ing and Incoming Error Propagation Specification               | 32   |

|   |     | 4.2.1<br>4.2.2<br>4.2.3 | Role of Outgoing and Incoming Error Propagation Declarations Using Outgoing and Incoming Error Propagations Observations | 32<br>33<br>34 |

|---|-----|-------------------------|--------------------------------------------------------------------------------------------------------------------------|----------------|

|   | 4.3 | _                       | Sources, Sinks, and Pass-Through                                                                                         | 35             |

|   | 7.0 | 4.3.1                   | Role of Error Source, Error Path, and Error Sink Declarations                                                            | 35             |

|   |     | 4.3.2                   | Using Error Source, Error Path, and Error Sink Declarations                                                              | 35             |

|   |     | 4.3.3                   | Observations                                                                                                             | 37             |

|   | 4.4 |                         | Propagation Contracts and Unhandled Faults                                                                               | 39             |

|   |     | 4.4.1                   | Role of Error Containment Declarations                                                                                   | 39             |

|   |     | 4.4.2                   | Using Error Containment Declarations                                                                                     | 39             |

|   |     | 4.4.3                   | Observations on Propagation Guarantees and Assumptions                                                                   | 40             |

|   | 4.5 |                         | Sources Resulting in Hazards                                                                                             | 41             |

|   | 4.6 |                         | standing the Fault Impact                                                                                                | 43             |

|   | 4.7 |                         | ying Unhandled Faults                                                                                                    | 43             |

| 5 | Con | nonent                  | Error Behavior                                                                                                           | 46             |

|   | 5.1 | •                       | ble Error Behavior State Machines                                                                                        | 46             |

|   | 0.1 | 5.1.1                   | Role of Error Behavior States, Events, and Transitions                                                                   | 46             |

|   |     | 5.1.2                   | ·                                                                                                                        | 47             |

|   |     | _                       | Predefined Set of Error Behavior State Machines                                                                          | 48             |

|   |     | 5.1.4                   | Typed Error Behavior State Machines                                                                                      | 49             |

|   |     | 5.1.5                   | Observations                                                                                                             | 51             |

|   | 5.2 |                         | onent-Specific Error Behavior Specification                                                                              | 51             |

|   | 0   | 5.2.1                   | Role of Component-Specific Error Behavior Specifications                                                                 | 51             |

|   |     | 5.2.2                   | Using Component-Specific Error Behavior Specifications                                                                   | 52             |

|   |     | 5.2.3                   | Observations                                                                                                             | 53             |

|   | 5.3 | -                       | Response and Fault Tolerance                                                                                             | 54             |

|   |     | 5.3.1                   | Role of Error Detection, Transition, and Propagation Conditions and Recovery or Repair Events                            | 54             |

|   |     | 5.3.2                   | Using Error Detection, Transition, and Propagation Conditions and Recovery or Repair Events                              | 55             |

|   |     | 5.3.3                   | Observations                                                                                                             | 56             |

| 6 | Con | position                | nal Abstraction of Error Behavior                                                                                        | 57             |

|   | 6.1 | Compo                   | osite Error Behavior Specification                                                                                       | 57             |

|   |     | 6.1.1                   | Role of Composite Error Behavior Specification                                                                           | 57             |

|   |     | 6.1.2                   | Using Composite Error Behavior Specifications                                                                            | 58             |

|   |     | 6.1.3                   | Observations                                                                                                             | 59             |

| 7 | Use | of Prop                 | erties in Architecture Fault Models                                                                                      | 60             |

|   | 7.1 | Proper                  | rty Associations on Error Model Elements                                                                                 | 60             |

|   | 7.2 | Detern                  | nining a Property Value                                                                                                  | 62             |

|   | 7.3 | User-D                  | Defined Error Model Properties                                                                                           | 63             |

|   | 7.4 | Preded                  | clared EMV2 Properties                                                                                                   | 63             |

|   |     | 7.4.1                   | Occurrence Distribution                                                                                                  | 63             |

|   |     | 7.4.2                   | Exposure Period                                                                                                          | 65             |

|   |     | 7.4.3                   | Propagation Time Delay                                                                                                   | 65             |

|   |     | 7.4.4                   | Duration Distribution                                                                                                    | 65             |

|   |     | 7.4.5                   | Transient Failure Ratio                                                                                                  | 65             |

|   |     | 7.4.6                   | Recovery Failure Ratio                                                                                                   | 65             |

|   |     | 7.4.7                   | State Kind                                                                                                               | 65             |

|   |     | 7.4.8                   | Detection Mechanism                                                                                                      | 66             |

|   |     | 7.4.9                   | Fault Kind                                                                                                               | 66             |

|   |     |                         | Persistence                                                                                                              | 66             |

|   |     | 7 4 11                  | Severity and Likelihood                                                                                                  | 66             |

|      |       | 7.4.12 Hazards                                                          | 67  |

|------|-------|-------------------------------------------------------------------------|-----|

|      |       | 7.4.13 Description                                                      | 69  |

| 8    | Adva  | anced Topics in EMV2                                                    | 70  |

|      | 8.1   | Error Model Subclauses and Inheritance                                  | 70  |

|      | 8.2   | Error Models and Feature Groups                                         | 72  |

|      | 8.3   | User-Defined Propagation Points and Paths                               | 73  |

|      |       | 8.3.1 Role of User-Defined Propagation Points and Propagation Paths     | 73  |

|      |       | 8.3.2 Using User-Defined Propagation Points and Propagation Paths       | 74  |

|      |       | 8.3.3 Observations                                                      | 74  |

|      | 8.4   | Error Type Mappings and Equivalence                                     | 74  |

|      |       | 8.4.1 Role of Type Mapping Sets and Error Type Equivalence              | 75  |

|      |       | 8.4.2 Using Type Mapping Sets and Error Type Equivalence                | 75  |

|      |       | 8.4.3 Observations                                                      | 76  |

|      | 8.5   | Type Transformations and Connection Error Behavior                      | 77  |

|      |       | 8.5.1 Role of Type Transformation Sets and Connection Error Behavior    | 77  |

|      |       | 8.5.2 Using Type Transformation Sets and Connection Error Behavior      | 78  |

|      |       | 8.5.3 Observations                                                      | 79  |

|      | 8.6   | Mapping Between Operational Modes and Failure Modes                     | 80  |

|      |       | 8.6.1 Role of Mapping Between Error Behavior States and Modes           | 80  |

|      |       | 8.6.2 Using the Mapping Between Error Behavior States and Modes         | 81  |

|      |       | 8.6.3 Observations                                                      | 83  |

|      |       | 8.6.4 The Composite GPS Error Model                                     | 84  |

| 9    | Arch  | itecture Fault Model Examples                                           | 86  |

|      | 9.1   | A Dual-Redundant Flight Guidance System with Operational Modes          | 86  |

|      |       | 9.1.1 Error Behavior of FGS Components                                  | 87  |

|      |       | 9.1.2 Composite Error Behavior of the FGS                               | 89  |

|      | 9.2   | Error Propagations Through Networks and Protocols                       | 91  |

|      | 9.3   | An Error Propagation and Mitigation Contract for a Dual-Channel Network | 94  |

|      | 9.4   | A Reconfigurable Triple-Redundant System                                | 96  |

| 10   | EMV   | 2 Syntax Rules                                                          | 102 |

|      | 10.1  | Error Model Library                                                     | 102 |

|      | 10.2  | Error Type Library, Error Type, Type Set, and Alias                     | 102 |

|      | 10.3  | Type Mapping Set and Type Transformation Set                            | 103 |

|      | 10.4  | Error Behavior State Machine                                            | 103 |

|      | 10.5  | Error Model Subclause                                                   | 105 |

|      | 10.6  | Error Propagation Section                                               | 105 |

|      | 10.7  | Component Error Behavior Section                                        | 106 |

|      | 10.8  | Composite Error Behavior Section                                        | 106 |

|      |       | Connection Error Behavior Section                                       | 107 |

|      | 10.10 | User-Defined Propagation Point and Path                                 | 107 |

| Refe | rence | S                                                                       | 108 |

# List of Figures

| Figure 1:  | Virtual Integration and Incremental Verification and Validation                      | 3  |

|------------|--------------------------------------------------------------------------------------|----|

| Figure 2:  | Architecture Fault Model                                                             | 4  |

| Figure 3:  | Error Propagation Between Components                                                 | 6  |

| Figure 4:  | Component Error Behavior                                                             | 7  |

| Figure 5:  | Composite Error Behavior and Its Abstraction                                         | 7  |

| Figure 6:  | Error Model Library                                                                  | 14 |

| Figure 7:  | Example of an Error Model Subclause                                                  | 15 |

| Figure 8:  | User-Defined Error Types                                                             | 17 |

| Figure 9:  | Use of Type Sets in Error Propagations                                               | 18 |

| Figure 10: | Error Type Library                                                                   | 19 |

| Figure 11: | Error Type Library of Aliases Only                                                   | 20 |

| Figure 12: | Use of Type Product                                                                  | 21 |

| Figure 13: | Error Type as a Subtype in a Type Hierarchy                                          | 21 |

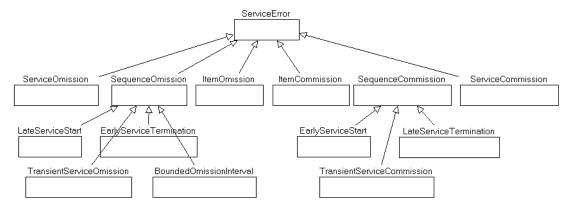

| Figure 14: | Hierarchy of Service-Related Error Types                                             | 24 |

| Figure 15: | Hierarchy of Value-Related Error Types                                               | 25 |

| Figure 16: | Aliases for Value-Related Error Types                                                | 25 |

| Figure 17: | Hierarchy for Timing-Related Error Types                                             | 26 |

| Figure 18: | Aliases for Timing-Related Error Types                                               | 27 |

| Figure 19: | Hierarchy for Replication Error Types                                                | 28 |

| Figure 20: | Aliases for Replication Error Types                                                  | 28 |

| Figure 21: | Hierarchy of Concurrency Error Types                                                 | 28 |

| Figure 22: | Predeclared Error Types in ErrorLibrary                                              | 29 |

| Figure 23: | Examples of Error Propagation Declarations for a Software Component                  | 34 |

| Figure 24: | Examples of Error Propagation Declarations for Hardware Components                   | 34 |

| Figure 25: | A Sensor with an Error Source and an Error Path                                      | 36 |

| Figure 26: | Example of an Error Sink Declaration                                                 | 37 |

| Figure 27: | Example of an Error Source on All Outgoing Propagation Points                        | 37 |

| Figure 28: | Fault Model Specification of a System Interface as Contracts, Assumptions, and Flows | 39 |

| Figure 29: | Example Error Containment Declaration                                                | 40 |

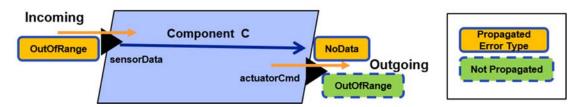

| Figure 30: | Matching Rules for Outgoing and Incoming Error Propagations                          | 40 |

| Figure 31: | Hazard Specification                                                                 | 42 |

| Figure 32: | Sample FHA Report                                                                    | 42 |

| Figure 33: | Example of a Fault Impact Report                                                     | 43 |

| Figure 34: | Error Propagations Between Subsystems                               | 44 |

|------------|---------------------------------------------------------------------|----|

| Figure 35: | Updated Specification of Error Propagations                         | 44 |

| Figure 36: | Mismatch Between Error Propagation Specifications                   | 45 |

| Figure 37: | Reusable Declaration for an Error Behavior State Machine            | 47 |

| Figure 38: | Example Model of an Error Behavior State Machine                    | 49 |

| Figure 39: | Untyped Specification for an Error Behavior Model                   | 50 |

| Figure 40: | Error Behavior State Machine with Error Types                       | 50 |

| Figure 41: | Example of a Component-Specific Error Behavior Declaration          | 53 |

| Figure 42: | Representation of the DegradedRecovery Error Behavior State Machine | 54 |

| Figure 43: | Example with Error Detection and Redundancy Logic Declarations      | 56 |

| Figure 44: | Flight Guidance System Fault Model at Two Levels of Abstraction     | 57 |

| Figure 45: | Composite Error Behavior Specification                              | 58 |

| Figure 46: | Property Associations in an Error Model Library                     | 61 |

| Figure 47: | Property Association to an Error Model Element with an Error Type   | 61 |

| Figure 48: | Subcomponent-Specific Property Association                          | 62 |

| Figure 49: | Definition of an EMV2 Property                                      | 63 |

| Figure 50: | Example Specification of Occurrence Distribution                    | 64 |

| Figure 51: | Example Use of a Likelihood Property Association                    | 67 |

| Figure 52: | Addition of Port and Error Propagation                              | 72 |

| Figure 53: | Override of an Error Propagation Specification                      | 72 |

| Figure 54: | Error Propagations on Feature Group Elements                        | 73 |

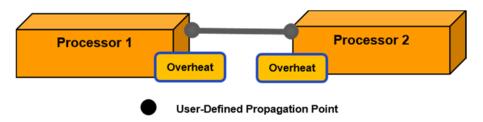

| Figure 55: | User-Defined Propagation Points and Propagation Path                | 73 |

| Figure 56: | User-Defined Propagation Point                                      | 74 |

| Figure 57: | Definition of a Type Mapping Set                                    | 75 |

| Figure 58: | Use of Type Mapping in an Error Path                                | 76 |

| Figure 59: | Example of Equivalence Mappings                                     | 76 |

| Figure 60: | Declaration of Error Type Library Equivalence                       | 76 |

| Figure 61: | Contributing Error Propagation in Connections                       | 78 |

| Figure 62: | Defining a Type Transformation Set                                  | 79 |

| Figure 63: | Connection Error Behavior Specification                             | 79 |

| Figure 64: | Operational Modes and Failure Modes                                 | 80 |

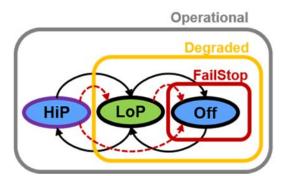

| Figure 65: | Superimposed Error Behavior States                                  | 81 |

| Figure 66: | Example of Mapping Error Behavior States onto Modes                 | 81 |

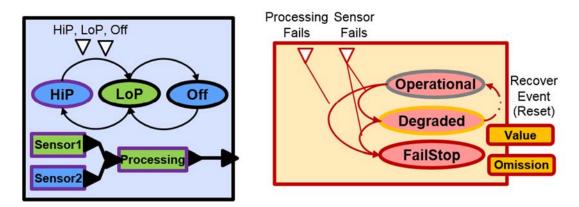

| Figure 67: | GPS Operational Modes and Abstracted Error Model                    | 82 |

| Figure 68: | Composite State Diagram of Operational and Failure Mode             | 83 |

| Figure 69: | Detectable Error Behavior of a Component                            | 84 |

| Figure 70: | GPS Composite Error Model Specification                   | 85  |

|------------|-----------------------------------------------------------|-----|

| Figure 71: | Overview of the FGS                                       | 86  |

| Figure 72: | Reusable Two-State Error Behavior                         | 87  |

| Figure 73: | Two-State Error Behavior of the FG Subsystem              | 87  |

| Figure 74: | Two-State Error Model for FG and AP                       | 88  |

| Figure 75: | Reusable Three-State Error Behavior Model                 | 88  |

| Figure 76: | Three-State Error Model for AC                            | 89  |

| Figure 77: | The GPSErrorModelLibrary Package                          | 90  |

| Figure 78: | Three-State Error Model for FGS                           | 91  |

| Figure 79: | Impact of Electrical Power Loss                           | 91  |

| Figure 80: | Error Propagation in a Multilayered Network               | 92  |

| Figure 81: | Network and Protocol Binding Specification                | 92  |

| Figure 82: | Network Fault Model Specification                         | 93  |

| Figure 83: | Fault Model Specification for the DP                      | 93  |

| Figure 84: | Fault Model Specification for the CRC                     | 93  |

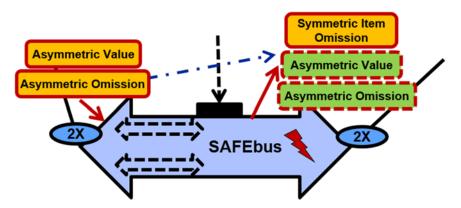

| Figure 85: | Errors Related to the SAFEbus                             | 94  |

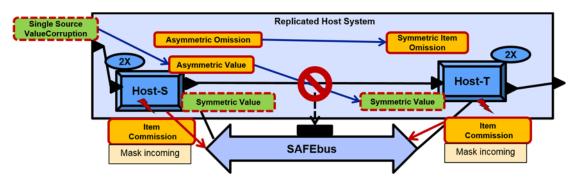

| Figure 86: | Error Propagation Related to Components Using the SAFEbus | 95  |

| Figure 87: | Triple-Redundant Error Behavior State Machine             | 97  |

| Figure 88: | Subsystem Fault Model with Error Paths and Voting Logic   | 98  |

| Figure 89: | Reconfigurable Triple-Redundant System Model              | 100 |

# **List of Tables**

| Table 1: | Propagation Paths Between Software Components | 31 |

|----------|-----------------------------------------------|----|

| Table 2: | Propagation Paths Between Hardware Components | 31 |

| Table 3: | Propagation Paths Based on Bindings           | 31 |

# **Executive Summary**

Safety-critical software-reliant systems must manage component failures and previously unidentified conditions of anomalous interaction among components as hazards that affect a system's safety, reliability, and security so that the potential effects of residual hazards on the system operation are reduced to an acceptable risk. Standards and recommended practices for safety-critical systems—such as DO-178B/C, SAE ARP4754A, and SAE ARP4761 in the aerospace industry—outline methods such as Functional Hazard Assessment, Failure Mode and Effect Analysis, Fault Tree Analysis, and availability and reliability prediction via reliability block diagrams. Security-related practices are typically addressed through separate guidance.

This report provides guidance on the use of the Error Model Annex, Version 2 (EMV2), notation [SAE 2015], a revision of the SAE AS-5506/1 Error Model standard for architecture fault modeling and analysis [SAE 2006]. EMV2 augments architecture models expressed in the Architecture Analysis & Design Language (AADL) with fault information to characterize anomalous conditions. Automated safety, reliability, and security analyses from the same annotated architecture model ensure consistency across analysis results.

The report introduces EMV2 concepts for architecture fault modeling of systems consisting of components in the context of an operational environment in terms of three levels of abstraction:

- focus on fault sources in a system and their impact on other components or the operational environment through propagation

- focus on a system or component fault model to identify faults and their occurrences within a system (component), their manifestation as failure, the effect of incoming propagations, conditions for outgoing propagation, and the ability of the system (component) to recover or be repaired

- focus on relating the fault model of system components to the abstracted fault model of the system

This layered abstraction allows for scalable compositional analysis.

In addition, EMV2 introduces the concept of error types to characterize exceptional conditions and their propagation. EMV2 includes a set of predefined error types as a starting point for systematic identification of different types of fault propagations, providing an error propagation ontology. Users can adapt and extend this ontology to specific domains.

EMV2 allows users to specify which system components are expected to detect, report, and manage anomalous conditions and their propagation and reflect the effects of recovery and repair actions taken by the system on the error behavior state. The implementation of health monitoring and fault management functionality of the system is modeled in the AADL core model. In other words, EMV2 expresses anomalous behavior of systems independent of whether and how it is actually managed by the system.

The report includes a discussion of several example models:

- a Global Positioning System with a focus on the interaction between operational and failure modes

- a dual-redundant flight guidance system to show consistency between an abstracted architecture fault model and its composite model for a fault-tolerant system

- an example of abstractly specifying a fault behavior interface for a network protocol stack

- an example of specifying an abstract fault model for a dual-channel avionics network to ensure correct and consistent use

- a triple-redundant system that has both physical and logical redundancy

# **Abstract**

Safety-critical software-reliant systems must manage component failures and conditions of anomalous interaction among components as hazards that affect a system's safety, reliability, and security so the potential effects of hazards on system operation are reduced to an acceptable risk. Standards and recommended practices for safety-critical systems outline methods for analysis, but security-related practices are typically addressed through separate guidance. This report provides guidance on using the Error Model Annex, Version 2 (EMV2), notation for architecture fault modeling and analysis, which supports automated safety, reliability, and security analyses from the same annotated architecture model to ensure consistency across analysis results. EMV2 augments architecture models expressed in the Architecture Analysis & Design Language with fault information to characterize anomalous conditions. The report introduces concepts for architecture fault modeling of systems in an operational environment at three levels of abstraction. In addition, EMV2 introduces the concept of error types to characterize exceptional conditions and their propagation. Finally, EMV2 allows users to specify which system components are expected to detect, report, and manage anomalous conditions and their propagation and to reflect the effects of recovery and repair actions as error behavior states. The report includes several example models.

## 1 Introduction

This report provides a guide to architecture fault modeling using the SAE International Architecture Analysis & Design Language (AADL) [SAE 2012] and the Error Model Annex, Version 2 (EMV2), standard [SAE 2015]. The resulting models are the basis for various forms of safety and dependability analysis. A separate report discusses how architecture fault models support the ARP4761 safety analysis practice, illustrated with a wheel braking system [Delange 2014].

# 1.1 Background

Development efforts for safety-critical software-reliant systems must manage component failures and previously unidentified conditions of anomalous interaction among components as hazards that affect reliability, safety, and security so that the potential effects of residual hazards on the system operation are reduced to an acceptable risk. Reliability focuses on providing continued operation despite failures. Safety focuses on unsafe conditions due to failures, malfunctions, or unexpected interactions between system components and the environment that result in catastrophic consequences for human life, health, property, or the environment. Security focuses on the protection of systems from accidental or malicious access, use, modification, destruction, or disclosure.

Standards and guidance documents for safety-critical systems—such as DO-178B/C, SAE ARP4754, and SAE ARP4761 in the aerospace industry—outline recommended practices such as Functional Hazard Assessment (FHA), Preliminary System Safety Assessment (PSSA), full System Safety Assessment (SSA), and Common Cause Failure Analysis. Other methods include Failure Modes and Effect Analysis (FMEA) and its variant Failure Mode, Effects, and Criticality Analysis; Fault Tree Analysis (FTA); availability and reliability prediction via reliability block diagrams and stochastic Petri net or Markov models; and architectural designs such as using system partitioning as a protection scheme for fault isolation and containment (DO-178B/C and ARINC-653).

These methods are labor intensive and, therefore, are often applied once in the life of a system. For example, when a development team performs an FHA, they record only hazards that result in catastrophic failure. Later when performing an FMEA, experts explore failure modes and one or two levels of effects. Due to the large effort involved, tradeoffs between alternative designs are often not examined using an FMEA. Consistency between FHA, FMEA, FTA, and other analyses is typically maintained by inspection of documents that capture the results of these analyses, another time-consuming and fallible activity. Alternatively, by generating safety analysis representations, such as fault trees, from AADL models annotated with EMV2, we ensure that architectural changes are consistently propagated and reflected in analysis reports when repeated. This approach maintains consistency across analyses beyond safety to include performance, security, and other objectives.

While these practices typically focus on safety and reliability, the underlying concepts of hazards and their propagation can also be used to identify security concerns that potentially result in intrusion and violation of information confidentiality. Partitioned architecture designs have been promoted as a key to Multiple Independent Levels of Security/Safety (MILS) [Rushby 1981], which is reflected in the Common Criteria for Information Technology Security Evaluation [ISO 2005].

1

As safety-critical systems have become more software reliant, they have also experienced major cost increases. Software systems can make up more than 75% of the system cost, and as much as 70% of that is the cost of rework due to errors introduced in requirements and architecture design but not discovered until system integration [NIST 2002]. Several root causes with system-wide impact have emerged, as evident from the increased fault leakage from requirements and architecture design into system integration and later into the system life cycle [Feiler 2010]. This fault leakage is due to mismatched assumptions in the interfaces among software components, between software components, and between the hardware platform and the physical system, in particular with respect to nonfunctional properties. Root causes of mismatched assumptions among system components include the following:

- base type and abstract data type representations, including inconsistent use of measurement units and value ranges

- real-time processing of time-sensitive data streams and the impact of latency jitter, mismatched streaming rates, and dropped or corrupted data elements on continuous control system behavior and discrete system state interaction

- synchronizing and coordinating redundant processing streams, in particular detection and recovery logic for anomalous system behavior such as Byzantine failure behavior

- interactions between state-based systems with replicated, mirrored, and coordinated state machines representing operational and failure modes (mode confusion)

- impact of state vs. state change communication under faulty transfer conditions, and the use of sampled processing to communicate events, leading to possible loss of events (inconsistent state)

- performance impact of resource management due to mismatched resource demand and capacity and unmanaged shared resource usage

- virtualization of resources, such as partitioned architectures, resulting in potential inconsistency of logical and physical redundancy and affecting reliability and availability

- virtualization of time, resulting in temporal inconsistencies and potential loss of information

# 1.2 Virtual System Integration and Architecture Fault Modeling

The SAE AADL standard provides a notation for specifying the architecture of software-reliant systems [Feiler 2012, SAE 2012]. It introduces component concepts that are specific to the architectures of software systems:

- packages, data components, subprograms, subprogram groups, and system and abstract components to specify a functional or software design architecture

- processes and threads with port connections, remote service calls, and shared data access to specify the runtime architecture of a software system

- processors, virtual processors, memory, buses, virtual buses, and their interconnections via bus access to specify a hardware platform

- devices, buses, and systems with both logical and physical connections to specify interactions with the physical system

Well-defined execution semantics, communication timing semantics, and standardized extensions allow for qualitative and quantitative analyses of multiple quality attributes of a multitier system

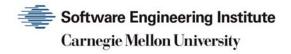

architecture from the same architecture model. Furthermore, they can be analyzed incrementally as the architecture hierarchy is refined and evolved. The aerospace industry's System Architecture Virtual Integration (SAVI) initiative has demonstrated the value of virtual integration and predictive analysis of architecture models for discovering system-level issues early in the development process, thus reducing the cost of major rework [Redman 2010]. These results led to an approach to system quality certification and improvement that combines predictive analysis based on virtual integration with increased formalization of requirements, increased use of static analysis such as model checking, and assurance cases to manage evidence that the system design and implementation have met functional and operational quality requirements [Feiler 2013]. Figure 1 illustrates this approach.

Figure 1: Virtual Integration and Incremental Verification and Validation

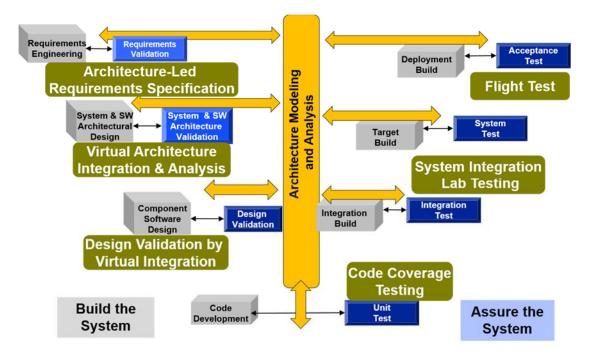

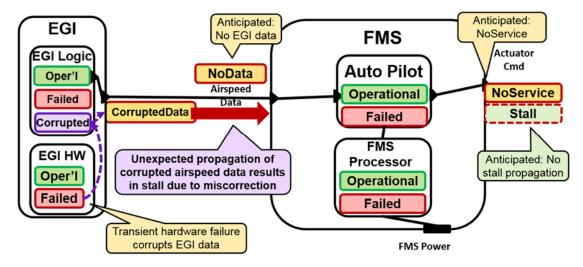

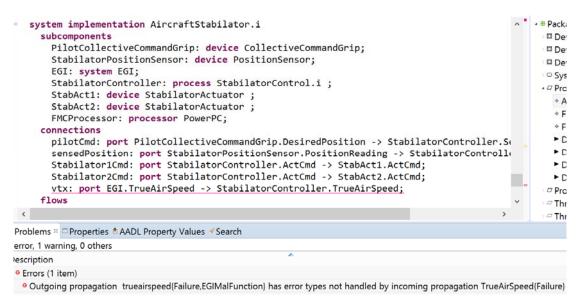

One standardized extension, the AADL Error Model Annex standard [SAE 2006], supports architecture fault modeling by enabling annotation of an architecture model with fault occurrence and resulting failure and fault propagation behavior to address dependability concerns in safety-critical systems. A development team can leverage potential fault propagation paths already represented in AADL models to generate representations for safety analysis (see Figure 2). The results allow engineers to use an automated safety analysis process by supporting qualitative and quantitative analysis of system reliability, availability, safety, security, and survivability. The process can also include determining compliance of the system to the specified fault-tolerance strategies. The effectiveness of this approach has been demonstrated on safety assessments of satellite systems [Hecht 2011]. EMV2 has recently been used to demonstrate the automation of the different safety analysis activities that are part of the SAE ARP4761 standard for conducting safety assessments in civil airborne systems and equipment. This case study is the subject of a separate report [Delange 2014].

Figure 2: Architecture Fault Model

We have revised the Error Model Annex standard based on users' experience with the original annex in industrial pilot projects to improve the set of concepts and intended semantics for modeling the fault occurrence, propagation, and management behavior of a system. EMV2 is the subject of this report [SAE 2015].

# 1.3 Language Concepts in EMV2

We use the word *error* in the names of several EMV2 concepts to distinguish them from similar concepts in the AADL core language and other annexes. For example, within EMV2 an *error event* represents the occurrence of an anomalous condition, while *event* in the AADL core language represents a Boolean signal communicated through event ports. In Section 1.4, we relate the EMV2 concepts to terms and concepts commonly used by the safety, reliability, and dependability communities.

EMV2 supports architecture fault modeling at three levels of abstraction, each of which uses specific language concepts defined later in this section:

- focus on fault propagation across the system: propagation of faults and their impact between

the system and its operational environment and between subsystems within a system. This

level allows for safety analysis in the form of hazard identification and fault impact analysis.

- focus on fault and recovery behavior of components: identification of faults and their occurrences, their manifestation in the component as failure modes, the effect of incoming propagations on failure modes, the propagation of failure modes and incoming propagations as outgoing propagation, and the ability of the component to detect and recover or repair. This level allows for probabilistic reliability and availability analysis.

- focus on compositional abstraction of fault models: relate the fault model of system components to the abstracted fault model of the system. This level allows for scalable compositional fault analysis.

In addition, EMV2 introduces the concept of *error type* to characterize faults, failures, and propagations. EMV2 includes a set of predefined error types as a starting point for systematic identification of different types of fault propagations—providing an error propagation ontology. Users can adapt and extend this ontology to specific domains.

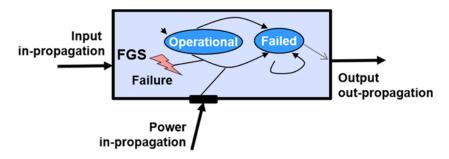

# 1.3.1 Fault Propagation Across the System

The first level of abstraction focuses on fault propagation between subsystems and within the environment. The specification of fault propagation in EMV2 corresponds to the Fault Propagation and Transformation Calculus (FPTC) [Paige 2009]. The following concepts are used to annotate system components:

- Error propagation and containment are associated with interaction points (ports, data and bus access, remote service calls, deployment binding points) to other components and specify the different types of effect, such as bad value or no service, that a component failure or incoming propagation can have on other components. They can also specify that a component is expected not to propagate certain types of effects. Outgoing and incoming propagation and containment specifications act as contracts between interacting components; they are guarantees and assumptions that must be verified.

- *Error types* characterize the different types of errors being propagated (e.g., a value error or timing error) or different types of error events (e.g., a component being overheated, cracked, or stuck).

- *Error sources* identify components as sources of error propagation; that is, they specify when a component's internal failure results in a propagation.

- Error paths and sinks specify how components respond to incoming propagations. They describe whether a particular error propagation is passed on to other components in the same form, propagated to other components as a different error type, or contained by the component.

- Propagation paths are determined by the logical and physical connectivity in the architecture, the deployment of software on hardware, and user-defined propagation paths not recorded in the AADL core model.

- *Probability properties* are associated with the occurrence of error propagations, sources, paths, and sinks.

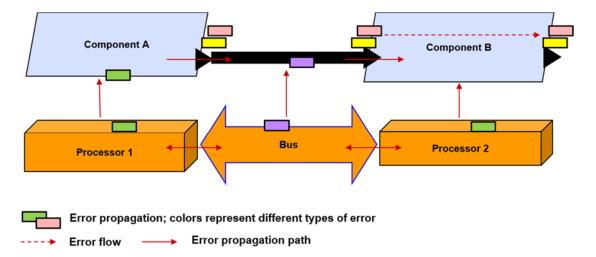

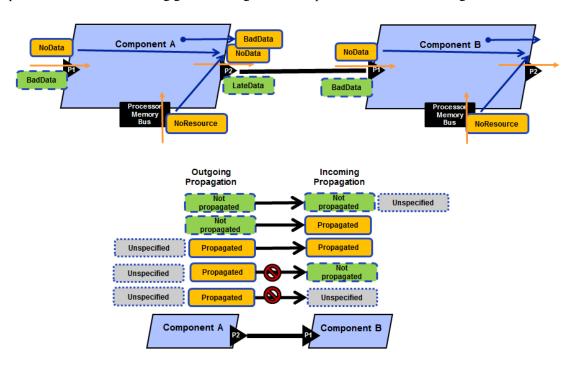

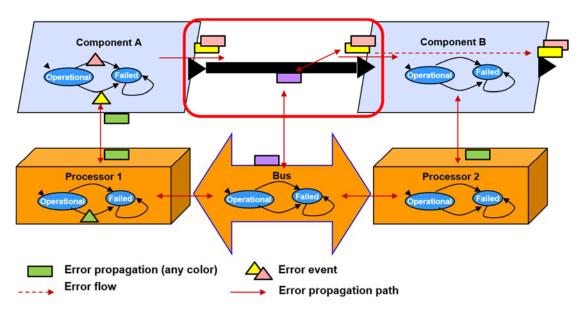

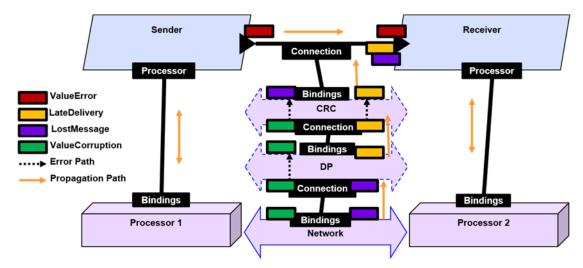

Figure 3 illustrates error types associated with outgoing and incoming ports to indicate error propagations, shown as rectangles of different colors. The propagation path between components follows the port connection between Components A and B. Component A is a source of a specific type of error caused by a specific type of failure in Component A (shown as a colored oval). Component A also passes on incoming errors from its *in* port to its *out* port.

Figure 3: Error Propagation Between Components

## 1.3.2 Fault and Recovery Behavior of Components

The component fault and recovery behavior specification of EMV2 characterizes the possible fault occurrences and resulting failure modes of the component as a whole. A specification for component error behavior describes the occurrence and handling of error events and incoming propagation in different failure modes, handling of redundant input to tolerate failures in external components, and restrictions that failure modes place on operational modes. The following concepts are used to annotate system components:

- three types of *error behavior events:*

- *error event:* represents the occurrence (activation) of a fault within a component

- recover event: reflects actions taken by the system to recover from a failure

- repair event: reflects repair or replacement of the failed component by an external agent

- probability properties associated with the occurrence of these events

- *error behavior state* in an *error behavior state machine:* represents the fact that a component is operational or is in a failure state (failure mode)

- *error behavior transition* with trigger conditions: specifies how error, recover, and repair events of the component as well as incoming error propagations from external components change the error behavior state of the component

- *outgoing propagation condition:* specifies that certain error behavior states, incoming error propagations, or combinations result in a particular outgoing error propagation

- *detection condition:* specifies whether a particular component is expected to detect and handle error behavior states and propagations, represented by an event in the AADL core model

- *mode mapping:* specifies how an error behavior state (failure mode) can restrict a set of operational modes in the AADL core model

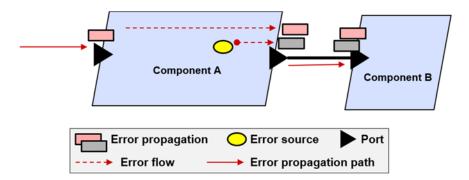

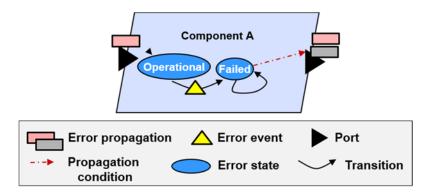

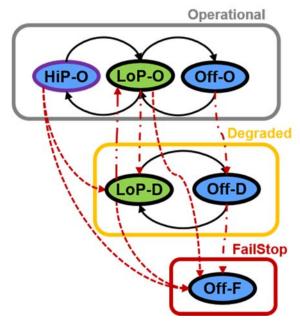

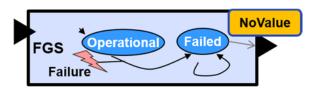

Figure 4 shows a component with an error event representing failures within the component and two error behavior states: *Operational* and *Failed*. The event causes a transition from *Operational* to *Failed*, and the *Failed* state is observable by others in the form of an error propagation.

Figure 4: Component Error Behavior

## 1.3.3 Compositional Abstraction of Fault Models

The compositional abstraction of fault models in EMV2 provides a *composite error behavior state specification* of a system in terms of the error behavior states of its subsystems. This specification defines the conditions under which a component is in a particular error behavior state expressed in terms of the error behavior states of its parts. This specification reflects redundancy in the parts to achieve fault tolerance and corresponds to the logic in fault trees. It must be consistent with the abstract error behavior specifications of the interacting parts.

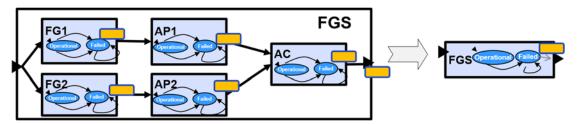

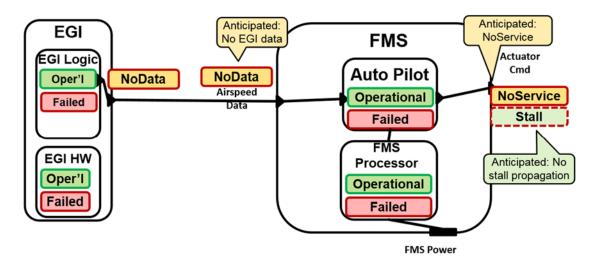

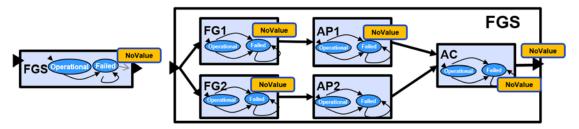

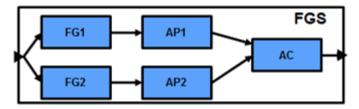

Figure 5 shows a composite flight guidance system (FGS) with its implementation by several sub-components, each with its own specification for component error behavior. The figure also shows the FGS with component error behavior that represents an abstraction of its implementation. A composite state declaration specifies that FGS is in the *Failed* state if a component of either flight guidance–autopilot pair fails or if the actuator fails.

[1 ormore(FG1.Failed or AP1.Failed) and 1 ormore(FG2.Failed or AP2.Failed) or AC.Failed]->Failed

Figure 5: Composite Error Behavior and Its Abstraction

Note: FG = flight guidance component, AP = autopilot component, AC = actuator.

In this report, we discuss an approach to architecture fault modeling that supports safety analysis practices in an architecture-centric manner and does so for both the system architecture and the (embedded) software system architecture. Architecture-centric design and development has value because requirements, including safety requirements, can be specified in an architecture model that describes both the system in its operational context and its composition in terms of subsystems. This approach allows an architecture specification or design to be validated at each level of architectural abstraction for completeness, consistency, and correctness and to be verified against its requirements specification or higher level design specification. The refinement of an architecture specification at each level propagates derived requirements down the architecture hierarchy.

# 1.4 Terms and Concepts

In EMV2 we always use the keyword **error** to characterize concepts, for example, error event, error behavior state, and error propagation. In this section, we relate EMV2 language concepts to terms defined in *Systems and Software Engineering—Vocabulary*, a common vocabulary for all systems and software engineering work established by the International Organization for Standardization, the International Electrotechnical Commission, and the Institute of Electrical and Electronics Engineers [ISO 2010]. This will help the reader understand how to appropriately use the EMV2 language constructs.

#### **Error** is defined as

1. a human action that produces an incorrect result, such as software containing a fault. 2. an incorrect step, process, or data definition. 3. an incorrect result. 4. the difference between a computed, observed, or measured value or condition and the true, specified, or theoretically correct value or condition

cf. failure, defect

EXAMPLE omission or misinterpretation of user requirements in a software specification, incorrect translation, or omission of a requirement in the design specification. [ISO 2010]

The definition of error encompasses mistakes by humans (the effect of a failure by the human), defects in a process that can lead to defects in a design or operational system, the effect of incorrect system behavior, and a characterization of anomalous behavior as an indication of a failure.

In EMV2 we consistently use the term *error* as a keyword to avoid confusion with similar constructs in the AADL core language or other annexes, such as event vs. error behavior event or state vs. error behavior state. See also defects, failures, and effects.

**Defect** is defined as "a generic term that can refer to either a fault (cause) or a failure (effect)" [ISO 2010]. See also fault and failure.

#### Fault is defined as

1. a manifestation of an error in software. 2. an incorrect step, process, or data definition in a computer program. 3. a defect in a hardware device or component. Syn: bug

NOTE: A fault, if encountered, may cause a failure. [ISO 2010]

The definition of fault includes one of the definitions for error. It also is defined in terms of defect, which in turn includes a definition in terms of fault. It also is the effect of human or process errors.

In EMV2 we represent fault types as error types. An EMV2 property lets us distinguish between design faults and operational faults. In a fault propagation specification, the presence of a fault in a component is expressed as an error source with the appropriate error type. In a component fault and recovery behavior specification, it is expressed as an error event with an error type, where an instance of that error event represents the activation of the fault (see failure).

#### Failure is defined as

1. termination of the ability of a product to perform a required function or its inability to perform within previously specified limits; 2. an event in which a system or system component does not perform a required function within specified limits, [ISO 2010]

The definition of failure encompasses the event of a fault activation and the manifestation of the fault activation in the component. The manifestation can be a malfunction, such as loss of service or anomalous behavior. See also failure mode.

In EMV2 we represent failures as error sources in fault propagation specifications and as error events in component fault and recovery behavior specifications. The manifestation of the failure is represented by an error behavior state. A transition specification describes how error behavior events change the error behavior state. See also failure.

**Failure mode** is defined as "the physical or functional manifestation of a failure" [ISO 2010]. According to the definition, a failure mode is associated with a physical or logical component.

In EMV2 we represent failure modes as error behavior states. Error behavior states are specified as part of error behavior state machines. Error behavior states can have error types to characterize different types of failure modes. Different types of faults are mapped to the respective type of failure mode through a transition specification. See also failure.

#### Failure mode and effect analysis (FMEA) is defined as

[Technique] an analytical procedure in which each potential failure mode in every component of a product is analyzed to determine its effect on the reliability of that component and, by itself or in combination with other possible failure modes, on the reliability of the product or system and on the required function of the component; or the examination of a product (at the system and/or lower levels) for all ways that a failure may occur. For each potential failure, an estimate is made of its effect on the total system and of its impact. In addition, a review is undertaken of the action planned to minimize the probability of failure and to minimize its effects. [ISO 2010]

Although the *Vocabulary* refers to "effects," it does not define the term [ISO 2010]. In the context of the FMEA definition, an effect refers to the failure mode. The effect of a failure is its propagation to other components and their responses to this propagation. Failure propagation is also referred to as fault propagation. The outgoing propagation can be due to a component failure or due to an incoming propagation. From the receiver's perspective, there is no difference, but from a diagnostic perspective, it is useful to identify the source.

In EMV2 we represent the propagation of failure modes and incoming effects as outgoing error propagations. Components can be the source of an outgoing propagation, they can be the sink of an incoming propagation, or they can pass on incoming propagations as outgoing propagations of the same or a different type. Conditions for outgoing propagations provide traceability to the cause, such as a failure (an error behavior state) triggered by an error event. An incoming propagation may affect the failure mode, or it may be passed on while the component is not in a failure mode. The probability of occurrence is associated with error behavior events, error sources, error behavior states, and error propagations to support stochastic analysis. The logic conditions also reflect fault tolerance strategies such as redundancy.

#### Hazard is defined as

1. an intrinsic property or condition that has the potential to cause harm or damage. 2. a source of potential harm or a situation with a potential for harm in terms of human injury, damage to health, property, or the environment, or some combination of these. [ISO 2010]

The definition of hazard has its root in safety engineering. It refers to both the effect and the source of a failure. Failures that result in loss of service are hazards that affect reliability. From a safety perspective, even minor failures must be considered hazards because combinations of them can have catastrophic effects [Leveson 2012]. The definition of hazard focuses on effects of failures in terms of injury and damage; that is, failures represent safety hazards. We include security hazards under the concept of hazard.

In EMV2 we represent hazards by a multivalued property that can be associated with the error source, error behavior state, and error propagation to support both definitions of hazard.

**Security** is defined as "the protection of system items from accidental or malicious access, use, modification, destruction, or disclosure" [ISO 2010]. The definition of security includes accidental malicious indication of anomalous behavior either from outside a system or by unauthorized crossing of a system's internal boundaries—typically in a manner that takes advantage of faults. The term *system item* covers information as well as physical components.

#### Threat is defined as

1. a state of the system or system environment which can lead to adverse effect in one or more given risk dimensions. 2. a condition or situation unfavorable to the project, a negative set of circumstances, a negative set of events, a risk that will have a negative impact on a project objective if it occurs, or a possibility for negative changes. [ISO 2010]

The definition of hazard focuses on the effects of failures in terms of injury and damage; that is, failures represent safety hazards. In EMV2, we include security hazards under the concept of hazard, and threats are one class of security hazards.

#### Fault tolerance is defined as

1. the ability of a system or component to continue normal operation despite the presence of hardware or software faults. 2. the number of faults a system or component can withstand before normal operation is impaired. 3. pertaining to the study of errors, faults, and failures, and of methods for enabling systems to continue normal operation in the presence of faults.

The definition of fault tolerance focuses on the presence of hardware and software faults. Fault tolerance includes fault detection, fault isolation, and fault recovery. Fault recovery elements include fault containment, fault masking, fault repair, and fault correction. Fault avoidance focuses on not introducing faults or eliminating them before the system goes into operation.

**Error tolerance** is defined as "the ability of a system or component to continue normal operation despite the presence of erroneous inputs" [ISO 2010]. The definition of error tolerance focuses on propagated errors.

In EMV2 tolerance of both faults and errors is supported by transition and outgoing propagation conditions that refer to error behavior states and incoming propagations. Expectations on fault tolerance through redundancy is expressed through appropriate logic in the transition and outgoing propagation conditions. Expected detection of faults by the system is specified by error detection declarations as well as recover and repair events. These specifications provide traceability into the fault tolerance architecture of the system.

For mechanical components, the error behavior specified by EMV2 can reflect both fault occurrences in the physical components due to operational use and latent design faults that are triggered during operation. For physical systems, long design cycles are assumed to reduce design errors to a minimum over time. For software, however, all fault occurrences result from design and coding errors, and we cannot make zero-defect assumptions for software. EMV2 allows users to characterize error events as representing design errors and operational errors to help them distinguish and respond to each type appropriately.

#### 1.5 Reader's Guide

Section 2 introduces the concepts of error model libraries and error model subclauses. An error model library contains reusable elements, such as error types and type sets, error behavior state machines, type mapping sets, and type transformation sets. An error model subclause contains component-specific error model annotations, such as error propagations and error flows, and component-specific error behavior in terms of error behavior events, error behavior states and transitions, and composite error behavior. The error model subclause models the error behavior of a component in terms of the error behavior of its subcomponents.

Section 3 introduces the concepts of error types and type sets, their organization into error libraries, their extension and adaptation to specific application domains through aliases, and the concepts of type products and type hierarchies to represent interaction between error types. This section also introduces the reader to an ontology of error propagation types that is a good starting point for fault modeling. The section concludes with a discussion of type mappings and the ability to specify type equivalence of independently developed error type libraries.

Section 4 focuses on fault propagation across the system and its impact. It introduces the concepts of error propagation points and outgoing and incoming error propagation specifications. It also introduces the concepts of error sources, error sinks, and error paths, which allow users to abstractly specify how a system component deals with errors. The error propagation path determines what components are affected by an outgoing propagation from a component. Finally, the concept of error containment, combined with error propagation, specifies the fault model assumptions and contracts that a component makes about its interactions with other components.

Section 5 covers specification of component fault behavior. It introduces the concepts of error events, states, and transitions. Reusable error behavior state machines ease the job of defining such behavior. Recover and repair events, as well as outgoing propagation conditions and error detection conditions, support the specification of fault tolerance strategies.

Section 6 focuses on compositional abstraction of error behavior. It explains how to specify the abstracted behavior of a system in terms of the error behavior states of its components.

Section 7 discusses the use of properties with error model elements as well as their definition by users. It also provides a summary of properties that have been predeclared as part of the EMV2 standard.

Section 8 presents advanced topics in EMV2. They include the concept of inheritance of error model specifications between component types and implementations as well as through the component extension hierarchy. This section also covers error model specifications for feature groups, user-defined propagation points and paths, error type mappings and type equivalence, type transformations and their use in specification of connection error behavior, and the mapping between operational modes and failure modes, which are also known as error behavior states.

Section 9 discusses several example models. They include a Global Positioning System (GPS) system with a focus on the interaction between operational and failure modes, a dual-redundant flight guidance system to show the consistency between an abstracted architecture fault model and its composite model for a fault-tolerant system, an abstract specification of a fault behavior interface for a network protocol stack, an abstract specification of a fault model for a dual-channel avionics network to ensure correct and consistent use, and a triple-redundant system that has both physical and logical redundancy.

Section 10 provides the EMV2 syntax rules.

## 2 Error Model Libraries and Subclause Annotations

EMV2 supports architecture fault modeling and analysis through the annotation of architecture models expressed in AADL with

- reusable error model libraries

- component-specific error behavior annotations through error model subclauses

This section explains how to use libraries and subclauses.

# 2.1 Error Model Library

#### 2.1.1 Role of an Error Model Library

The error model library provides reusable collections of error type and type set definitions, as well as mapping and transformation rules between error types. For example, users can map an incoming error propagation type, such as an out-of-range value, into an outgoing error propagation type, such as a missing value. In addition, an error model library can contain reusable specifications for error behavior state machines that consist of error events, states, and transitions. EMV2 includes a library of predefined error types.

#### 2.1.2 Using the Error Model Library

An error model library is defined in an AADL package. An AADL package can contain only one error model library—a restriction of the AADL core language. However, the package can contain other declarations. Within the package, use an AADL annex library clause, which identifies the annex as *EMV2*. Refer to the library using the package name.

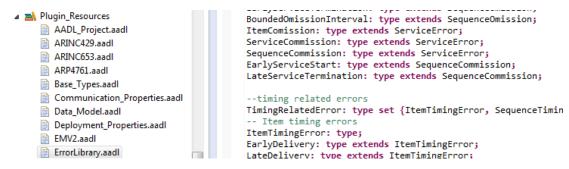

An error model library consists of zero or one error type library (**error types**) declaration, zero or more error behavior state-machine (**error behavior**) declarations, zero or more **type mappings** declarations, and zero or more **type transformations** declarations, in that order. The full syntax rule for error model libraries can be found in Section 10.1.

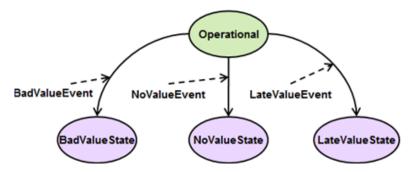

An example error model library specification is illustrated in Figure 6. It shows the definition of several error types, a type set, and an error behavior state machine with one error event (Fail), two states (Operational and Failed), and one transition (from Operational to Failed when the Fail error event occurs).

```

package MyErrorLib

public

annex EMV2 {**

error types

PowerFailure: type;

TransientPowerLoss: type;

PowerErrors: type set { PowerFailure, TransientPowerLoss };

SensorFailure: type;

NoService: type;

BadData: type;

NoData: type;

MissingCmd: type;

end types;

```

```

error behavior TwoState

events

Fail: error event;

states

Operational: initial state;

Failed: state;

transitions

Failure: Operational -[Fail]-> Failed;

end behavior;

**};

end MyErrorLib;

```

Figure 6: Error Model Library

#### 2.2 Error Model Subclause

#### 2.2.1 Role of an Error Model Subclause

An error model subclause provides component-specific fault model specifications by annotating component type, component implementation, and feature group type declarations. These specifications support the three levels of abstraction discussed in Section 1.3. They do so by utilizing error type libraries and error behavior state machines that are defined in error model libraries.

Supporting the error propagation specification, the error model subclause lets us specify incoming and outgoing error propagations and containments, as well as error sources, paths, and sinks.

Supporting the error behavior specification for components, the error model subclause lets us identify the error behavior state machine applicable to the component. It supports the introduction of component-specific error events, error behavior transition conditions in terms of error events, incoming propagations to the component, conditions under which propagations to other components occur, and whether the component will detect a failure represented by an error behavior state or incoming propagation. It also lets us specify how error behavior states affect the operational modes of the component.

Supporting the behavior specification for composite components, the error model subclause lets us specify how each abstract error behavior state of a component relates to the error behavior states of its parts.

Finally, the error model subclause allows us to associate property values with any element defined within the error model subclause. This can be done using properties defined in the EMV2 Annex standard or properties defined by users.

#### 2.2.2 Using the Error Model Subclause

A component-specific error behavior specification is defined by an AADL annex subclause identifying the annex as *EMV2*. The subclause is declared in a component type, component implementation, or feature group type. An error model subclause consists of

- a use types declaration (see Section 3.2)

- a **use type equivalence** declaration (see Section 8.4)

- a **use mappings** declaration (see Section 8.4)

- a use behavior declaration (see Section 5.2)

- an **error propagations** section (see Section 3)

- a component error behavior section (see Section 5)

- a composite error behavior section (see Section 6)

- a connection error section (see Section 8.4)

- a user-defined **propagation paths** section (see Section 8.2)

- a **properties** section (see Section 7)

The subclause elements must be declared in the above order, but all of these elements are optional.

The **use types** declaration lists the error type libraries whose content becomes accessible to the subclause without having to qualify references with the error type library name.

The **use mappings** clause specifies the type mappings to be used in error paths when no target type is specified.

The **use behavior** declaration identifies the error behavior state machine to be used for the component. The subclause has separate sections for error propagations, component error behavior, and composite error behavior. The identified error behavior state machine applies to all of these sections.

An example subclause is shown in Figure 7. The full syntax rule for the error model subclause is shown in Section 10.5.

```

package Devices

public

device PowerSupply

features

PowerOutlet: provides bus access;

annex EMV2 {**

use types MyErrorLib;

use behavior MyErrorLib::TwoState;

error propagations

PowerOutlet: out propagation {PowerFailure};

end propagations;

**};

end PowerSupply;

end Devices;

```

Figure 7: Example of an Error Model Subclause

# 3 Error Types and Common Type Ontology

EMV2 provides the concept of *error type* to characterize the types of errors to be propagated, the type of activated fault represented by an error event, and the type of failure mode represented by an error behavior state.

Error types can be grouped into *type sets*. A reference to the type set represents that collection of types. Type sets can act as constraints regarding types. For example, a type set associated with an incoming error propagation declaration indicates the set of acceptable incoming error types.

Error types and type sets are defined in reusable *error type libraries* that can be imported into an error model subclause. Users can import several type sets into the same error model subclause and use mapping rules to explain the relationship between them.

Error types can be combined into *type products* to indicate that a failure or propagation is characterized by both types at the same time. For example, a sent message may be late and contain an out-of-range value.

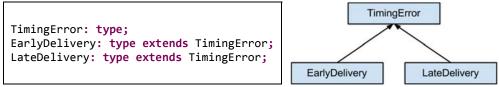

Finally, error types can also be placed into a *type hierarchy*. Error types from the same hierarchy cannot be combined in a type product as they are not expected to occur in combination. For example, a message cannot be late and early at the same time.

We proceed by describing the use of these concepts and introducing a common set of reusable error types as an error propagation ontology.

# 3.1 Error Types and Type Sets

## 3.1.1 Role of Error Types and Type Sets

An error type is a categorical label that is used to characterize the type of error in error propagation, error containment, error flow, error event, and error behavior state declarations. This label is also used to characterize conditions for state transition, outgoing error propagation, and detection declarations. Users do this by specifying a set of error types as part of their declarations.

For an error propagation or containment declaration, the type set indicates the collection of error types that potentially are or are not propagated through an error propagation point, such as a port. An instance of an error propagation is represented by a *type instance*, which is an instance of one of the elements listed in the type set. An error propagation instance of an element in a type set can be thought of as a type token that is propagated through the system.

For error events, an error type set specifies a collection of possible fault occurrences. For example, instead of defining 15 different error events, one for each kind of error that can occur in a component, we can specify a single error event and indicate the various error types as a type set annotation to the error event declaration (see Section 5.1.4). An occurrence of an error event is represented by an instance of one of the type set elements.