**ARL-SR-0370 ● APR 2017**

## **OS Friendly Microprocessor Architecture**

by Patrick Jungwirth and Patrick La Fratta

Approved for public release; distribution is unlimited.

### **NOTICES**

### **Disclaimers**

The findings in this report are not to be construed as an official Department of the Army position unless so designated by other authorized documents.

Citation of manufacturer's or trade names does not constitute an official endorsement or approval of the use thereof.

Destroy this report when it is no longer needed. Do not return it to the originator.

## **OS Friendly Microprocessor Architecture**

by Patrick Jungwirth

Computational and Information Sciences Directorate, ARL

### **Patrick La Fratta**

Aviation and Missile Research, Development, and Engineering Center, Redstone Arsenal, AL

Approved for public release; distribution is unlimited.

| REPORT                                                                                                                                                                                                                                | DOCUMENTATION PAGE                                                                                                                                                                                                       | Form Approved<br>OMB No. 0704-0188                                                                                                                                                                                                                                                                                                                                                 |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| data needed, and completing and reviewing the c<br>burden, to Department of Defense, Washington I                                                                                                                                     | ollection information. Send comments regarding this burden estimate<br>Headquarters Services, Directorate for Information Operations and Rep<br>ag any other provision of law, no person shall be subject to any penalty | ne for reviewing instructions, searching existing data sources, gathering and maintaining the or any other aspect of this collection of information, including suggestions for reducing the ports (0704-0188), 1215 Jefferson Davis Highway, Suite 1204, Arlington, VA 22202-4302, for failing to comply with a collection of information if it does not display a currently valid |  |  |

| 1. REPORT DATE (DD-MM-YYYY) 2. REPORT TYPE                                                                                                                                                                                            |                                                                                                                                                                                                                          | 3. DATES COVERED (From - To)                                                                                                                                                                                                                                                                                                                                                       |  |  |

| April 2017                                                                                                                                                                                                                            | Special Report                                                                                                                                                                                                           | September 2014–August 2016                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 4. TITLE AND SUBTITLE                                                                                                                                                                                                                 |                                                                                                                                                                                                                          | 5a. CONTRACT NUMBER                                                                                                                                                                                                                                                                                                                                                                |  |  |

| OS Friendly Microprocessor Architecture                                                                                                                                                                                               |                                                                                                                                                                                                                          | 5b. GRANT NUMBER                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|                                                                                                                                                                                                                                       |                                                                                                                                                                                                                          | SD. GRANT NOWIDER                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|                                                                                                                                                                                                                                       |                                                                                                                                                                                                                          | 5c. PROGRAM ELEMENT NUMBER                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 6. AUTHOR(S)                                                                                                                                                                                                                          | I. F                                                                                                                                                                                                                     | 5d. PROJECT NUMBER                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| Patrick Jungwirth and Patrick                                                                                                                                                                                                         | La Fratta                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|                                                                                                                                                                                                                                       |                                                                                                                                                                                                                          | 5e. TASK NUMBER                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|                                                                                                                                                                                                                                       |                                                                                                                                                                                                                          | 5f. WORK UNIT NUMBER                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 7. PERFORMING ORGANIZATION NA                                                                                                                                                                                                         | AME(S) AND ADDRESS(ES)                                                                                                                                                                                                   | 8. PERFORMING ORGANIZATION REPORT NUMBER                                                                                                                                                                                                                                                                                                                                           |  |  |

| US Army Research Laborator                                                                                                                                                                                                            | , ,                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| ATTN: RDRL-CIH-S                                                                                                                                                                                                                      | · <i>j</i>                                                                                                                                                                                                               | ARL-SR-0370                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| Aberdeen Proving Ground, M                                                                                                                                                                                                            | ID 21005-5067                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 9. SPONSORING/MONITORING AGE                                                                                                                                                                                                          | NCY NAME(S) AND ADDRESS(ES)                                                                                                                                                                                              | 10. SPONSOR/MONITOR'S ACRONYM(S)                                                                                                                                                                                                                                                                                                                                                   |  |  |

|                                                                                                                                                                                                                                       |                                                                                                                                                                                                                          | 11. SPONSOR/MONITOR'S REPORT NUMBER(S)                                                                                                                                                                                                                                                                                                                                             |  |  |

| 12. DISTRIBUTION/AVAILABILITY ST                                                                                                                                                                                                      |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| Approved for public release;                                                                                                                                                                                                          | distribution is unlimited.                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 13. SUPPLEMENTARY NOTES Patrick La Fratta is now affili                                                                                                                                                                               | ated with Micron Technology, Inc., Boise,                                                                                                                                                                                | Idaho.                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 14. ABSTRACT                                                                                                                                                                                                                          |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| framework to support the hard                                                                                                                                                                                                         | dware-level security features is currently p                                                                                                                                                                             | Microprocessor Architecture (OSFA). The software atent pending. We are interested in information e-level security features and information assurance                                                                                                                                                                                                                               |  |  |

| Conventional microprocessor<br>goal of the OSFA is to provid<br>hardware. By extending Unix<br>provides hardware-level infor<br>application, a table (white list<br>call has a set of object limits.<br>complexities of hardware, sof | le a high-performance microprocessor and<br>file permissions bits down to each cache remation assurance. OS-level access to memor<br>sets limits for all OS library function call                                        | ormance and OS performance at the same time. The OS. Computer security features are implemented in memory bank and memory address, the OSFA nory is divided into access layers. For each software is required by the application. Each library function ture and permission bits provide features to balance the                                                                   |  |  |

| 15. SUBJECT TERMS                                                                                                                                                                                                                     |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| microprocessor, operating sys                                                                                                                                                                                                         | stem, context switch, hardware computer se                                                                                                                                                                               | ecurity, computer security, cache bank pipeline, library                                                                                                                                                                                                                                                                                                                           |  |  |

| 16. SECURITY CLASSIFICATION OF: |              | 17. LIMITATION OF ABSTRACT | 18. NUMBER<br>OF<br>PAGES | 19a. NAME OF RESPONSIBLE PERSON Patrick Jungwirth |                                           |

|---------------------------------|--------------|----------------------------|---------------------------|---------------------------------------------------|-------------------------------------------|

| a. REPORT                       | b. ABSTRACT  | c. THIS PAGE               | ABSTRACT PAGES            |                                                   | 19b. TELEPHONE NUMBER (Include area code) |

| Unclassified                    | Unclassified | Unclassified               | UU                        | 56                                                | 410-278-6174                              |

### **Contents**

| List | of Fig | gures                     |                                                                                 | v        |  |

|------|--------|---------------------------|---------------------------------------------------------------------------------|----------|--|

| List | of Ta  | bles                      |                                                                                 | vi       |  |

| Pre  | face   |                           |                                                                                 | vii      |  |

| Ack  | nowl   | edgmei                    | nt                                                                              | viii     |  |

| 1.   | Intr   | oductic                   | on                                                                              | 1        |  |

|      | 1.1    | OS Frie                   | endly Microprocessor Architecture Permission Bits                               | 2        |  |

|      | 1.2    | Bus Ar                    | chitectures                                                                     | 2        |  |

| 2.   | In-B   | and Sig                   | gnaling, the Open Front Door                                                    | 3        |  |

| 3.   | OS I   | Friendly                  | Microprocessor Architecture                                                     | 4        |  |

|      | 3.1    | DMA/                      | Cache Bank Controller Architecture                                              | 5        |  |

|      | 3.2    | Conte                     | kt Switch                                                                       | 6        |  |

|      | 3.3    | Cache Bank Architecture 8 |                                                                                 |          |  |

|      |        | 3.3.1                     | OS Friendly Microprocessor Architecture Version 1 Cache Bank                    | 8        |  |

|      |        | 3.3.2                     | OS Friendly Microprocessor Architecture Version 2 Pipelin State Cache Bank      | ne<br>10 |  |

|      | 3.4    | OS Frie                   | endly Microprocessor Architecture Performance Modeling                          | 11       |  |

|      |        | 3.4.1                     | Conventional and OS Friendly Microprocessor Architectur Context Switch Modeling | e<br>11  |  |

|      |        | 3.4.2                     | Conventional Architecture Context Switch Modeling                               | 13       |  |

|      |        | 3.4.3                     | OS Friendly Microprocessor Architecture Context Switch Modeling (Version 1)     | 14       |  |

|      |        | 3.4.4                     | OS Friendly Microprocessor Architecture Context Switch Modeling (Version 2)     | 17       |  |

| 4.   | OS I   | Friendly                  | Microprocessor Architecture Hardware Computer                                   |          |  |

|      | Seci   | urity                     |                                                                                 | 17       |  |

|      | 4.1    | Cache                     | Bank and Memory Cell Permission Bits                                            | 18       |  |

|      | 4.2    | Instruc  | tion Permission Bits                                                                     | 18       |

|------|--------|----------|------------------------------------------------------------------------------------------|----------|

|      | 4.3    | Library  | Call Permissions                                                                         | 19       |

| 5.   | OS I   | Friendly | Microprocessor Architecture Access Layers                                                | 20       |

|      | 5.1    | Instruc  | ction, Data, Register, and Pipeline State Memory Partitions                              | 21       |

|      | 5.2    | Permis   | sion Bits: Microkernel, Thick OS, Drivers, and Applications                              | 21       |

|      | 5.3    | I/O Imp  | plementation                                                                             | 22       |

|      | 5.4    | Except   | ion Handling                                                                             | 24       |

|      | 5.5    | Practic  | al Permission Bit Architecture                                                           | 25       |

|      | 5.6    |          | endly Microprocessor Architecture Version 2: Practical Cach<br>Architecture              | ie<br>27 |

|      |        | 5.6.1    | OS Friendly Microprocessor Architecture Version 1 Permission Bit Limitations             | 28       |

|      |        | 5.6.2    | OS Friendly Microprocessor Architecture Version 2 Permission Bit Cache Bank Architecture | 28       |

|      | 5.7    | Microk   | kernel, OS, and Application Cache Banks Organization                                     | 29       |

|      | 5.8    | Proces   | s Level Cache Bank Operations                                                            | 30       |

|      | 5.9    | Cache    | Bank I/O Example                                                                         | 33       |

| 6.   | Con    | nputer S | Security Examples                                                                        | 35       |

|      | 6.1    | Buffer   | Overflow                                                                                 | 35       |

|      | 6.2    | Data Ex  | xecution Exploitation                                                                    | 36       |

|      | 6.3    | "Low-L   | evel Driver" Protection                                                                  | 37       |

|      | 6.4    | Contro   | l Information Protection                                                                 | 40       |

|      | 6.5    | Debug    | ging Traps                                                                               | 40       |

|      | 6.6    | Hardw    | are Features for Hypervisor                                                              | 40       |

|      | 6.7    | Archite  | ecture Issues                                                                            | 41       |

| 7.   | Con    | clusion  |                                                                                          | 42       |

| 8.   | Refe   | erences  |                                                                                          | 43       |

| List | of Sy  | mbols,   | Abbreviations, and Acronyms                                                              | 45       |

| Dist | tribut | ion List |                                                                                          | 46       |

## **List of Figures**

| Fig. 1  | OS friendly microprocessor architecture                                                                                                  | 1  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 2  | von Neumann and Harvard bus architectures                                                                                                | 3  |

| Fig. 3  | Computer memory types and sizes                                                                                                          | 3  |

| Fig. 4  | OS friendly microprocessor architecture                                                                                                  | 5  |

| Fig. 5  | OS friendly DMA controller and cache bank controller pipeline architecture                                                               | 6  |

| Fig. 6  | OS friendly microprocessor architecture context switch timing diagram                                                                    | 7  |

| Fig. 7  | Data, instruction, and register cache controller banks                                                                                   | 9  |

| Fig. 8  | Pipeline state parallel cache controller banks                                                                                           | 10 |

| Fig. 9  | OS friendly microprocessor architecture version 2 pipeline state cache banks                                                             | 11 |

| Fig. 10 | Conventional processor architecture model                                                                                                | 12 |

| Fig. 11 | OS friendly microprocessor architecture model                                                                                            | 13 |

| Fig. 12 | Cache bank and memory cell hardware information assurance                                                                                | 18 |

| Fig. 13 | Library function call table information assurance                                                                                        | 19 |

| Fig. 14 | OS friendly microprocessor architecture cache bank permission bits                                                                       | 20 |

| Fig. 15 | Secure microkernel cache banks and permission bits                                                                                       | 22 |

| Fig. 16 | Thick OS cache banks and permission bits                                                                                                 | 22 |

| Fig. 17 | Application's permission bits                                                                                                            | 22 |

| Fig. 18 | OS friendly microprocessor architecture I/O example                                                                                      | 23 |

| Fig. 19 | Real-world example of OS friendly microprocessor architecture's permission architecture                                                  | 23 |

| Fig. 20 | For the I/O port, the application software knows the register number however, the application cannot access the contents of the register |    |

| Fig. 21 | Permission bits and hardware exception handling                                                                                          | 25 |

| Fig. 22 | Example 4-layer architecture                                                                                                             | 27 |

| Fig. 23 | Practical permission bit and cache bank architecture                                                                                     | 28 |

| Fig. 24 | Cache bank permission bit lookup table                                                                                                   | 29 |

| Fig. 25 | OS friendly microprocessor architecture cache bank organization                                                                          | 30 |

| Fig. 26 | Microkernel cache bank organization                                                                                                      | 31 |

| Fig. 27 | OS and application cache bank organization                                                                                               | 32 |

| Fig. 28   | Application writes a cache bank block of data to USB controller          | 34 |

|-----------|--------------------------------------------------------------------------|----|

| Fig. 29   | Process stack example                                                    | 36 |

| Fig. 30   | Ethernet frame                                                           | 37 |

| Fig. 31   | Cache bank and Ethernet frame example                                    | 39 |

| Fig. 32   | Real-time debugging trap example                                         | 40 |

| Fig. 33   | OS friendly microprocessor architecture: software and hardware hierarchy | 42 |

| List of 1 | ables                                                                    |    |

| Table 1   |                                                                          |    |

| 14010 1   | Conventional architecture context switch steps                           | 14 |

| Table 2   | OS friendly microprocessor architecture version 1 context switch steps   |    |

|           | OS friendly microprocessor architecture version 1 context switch         | 16 |

### **Preface**

The paper "OS Friendly Microprocessor Architecture: Hardware Level Computer Security" was originally published in *Proceedings of SPIE: Cyber Sensing 2016*, 0277-786X, V. 9826 (2016 April 19, Baltimore, MD). This report is a longer version of the published paper and it includes additional material, including 1) a bus architecture introduction, 2) Operating System Friendly Microprocessor Architecture (OSFA) Version 2 pipeline state cache bank, 3) debugging traps, and 4) architecture features for a hypervisor.

### Acknowledgment

The author wishes to thank The US Army Aviation and Missile Research, Development, and Engineering Center and the US Army Research Laboratory for the opportunity to develop and improve the OS Friendly Microprocessor Architecture.

### 1. Introduction

The Operating System (OS) Friendly Microprocessor Architecture's (OSFA's) goals are to provide a high-performance microprocessor and reduce the code complexity of an operating system. We have developed a computer architecture that reduces the high cost of a context switch and provides hardware-based computer security. A context switch can be as fast as 1 central processing unit (CPU) cycle.

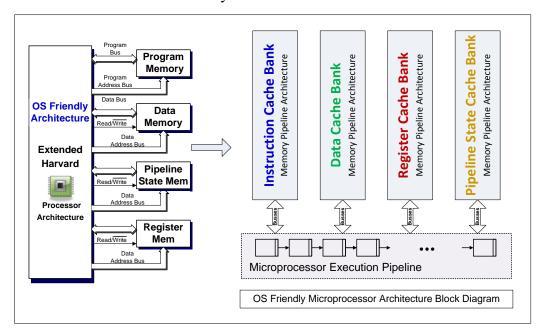

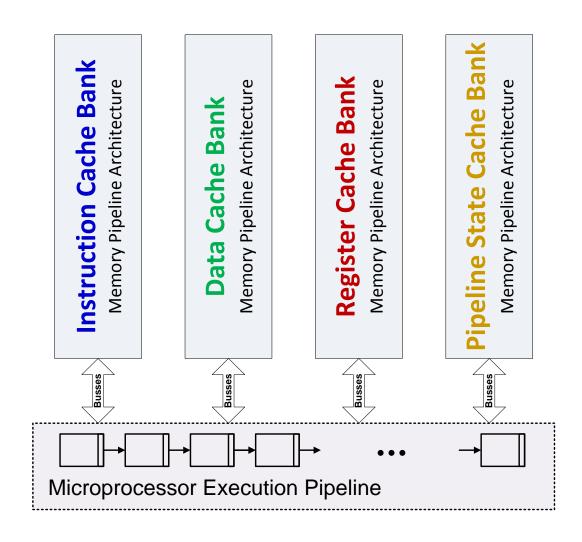

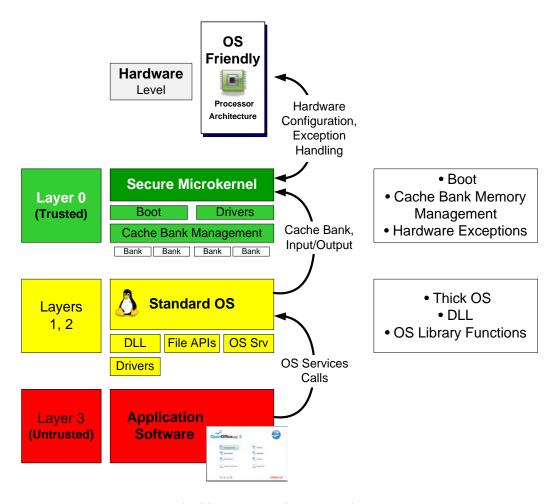

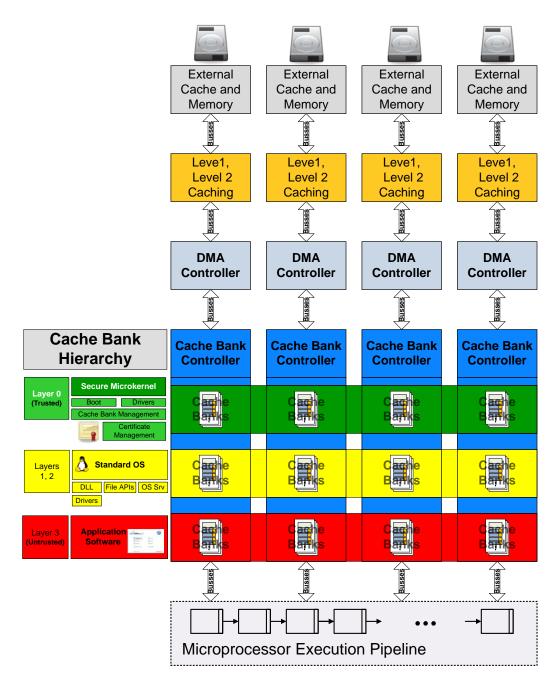

Figure 1 introduces the OSFA.<sup>1–2</sup> The processor memory and bus architecture is an extended Harvard architecture. The OSFA<sup>1</sup> uses pipeline memory controllers to rapidly background switch cache memory pages. The pipeline memory architecture supports hardware-based OS context switches. Context switches for lightweight threads can be as fast as 1 CPU cycle.

Fig. 1 OS friendly microprocessor architecture

OS information assurance is implemented in hardware. By extending the traditional Unix file permissions bits down to each memory cell, each cache line, and each cache memory bank, the OSFA processor provides hardware-based computer security.

### 1.1 OS Friendly Microprocessor Architecture Permission Bits

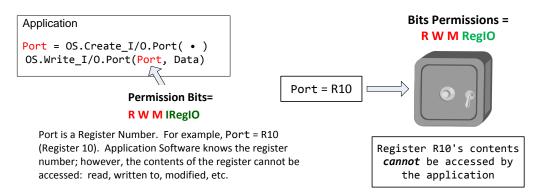

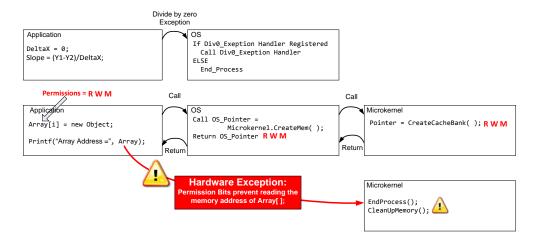

A unique feature of the OSFA is the permission bit Index\_Register\_I/O (IRegIO). IRegIO allows the OS to provide an index register pointing to an input/output (I/O) port or I/O memory address. The IRegIO bit "locks out" the memory address pointer (index register) from being read, written to, or modified. The running process is prevented from accessing the contents of the register; however, the process can use the index register (pointer) to read/write to I/O (registers, ports, or addresses).

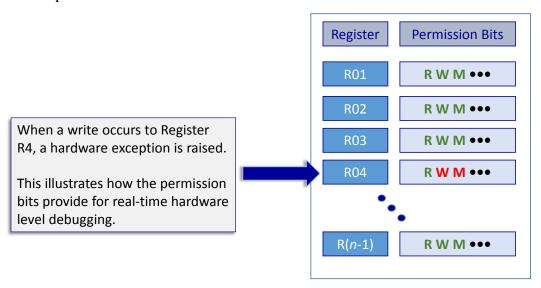

The hardware permission bits can be set to allow real-time software debugging. Program debugging can use the **R** W M permission bits (Read = allowed, Write = not allowed, and Modify = not allowed) to trap all writes made to a memory address or register. This allows for hardware level debugging with zero performance overhead at the software level until a write occurs.

Library function protection is provided by extending the principal of least privilege to library function calls. For each software application, a table sets limits (white list) for all OS function calls required by the application. The library function call table sets limits for typical load, moderate load, and maximum load. Exceeding the limits for typical load, moderate load, and/or maximum load can be set to generate an exception or require higher than user level privileges.

Sections 2 through 5 cover the OSFA. Section 6 covers computer security, information assurance, and permission bits.

### 1.2 Bus Architectures

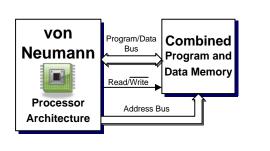

There are 2 commonly used microprocessor bus architectures. The von Neumann architecture consists of a unified instruction (program) and data memory. The combined memory contains both data and instructions. Newer microprocessors incorporate a no-execute bit in cache memory tables to prevent data from being executed. A Harvard bus architecture has separate instruction (program) memory and data memory. A modified Harvard architecture has internal separate caches for instructions (program) and data with a combined (unified) external memory. Figure 2 compares von Neumann and Harvard bus architectures. Note, the Harvard architecture allows for parallel memory operations over the 2 busses and memories.

Fig. 2 von Neumann and Harvard bus architectures

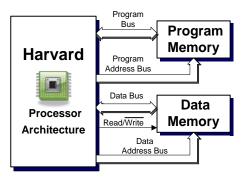

Figure 3 compares computer memory types and approximate memory sizes for 2013. Register memory is the fastest memory inside a computer. Register memory typically is small. Level 1 (L1) and level 2 (L2) memory caching are contained on-chip inside the microprocessor. Level 3 (L3) memory caching can be on or off chip. Main memory is present on the main or system computer board. Hard drives and tape backups represent mass storage memory. The memory types from register to mass storage span a range of approximately  $10^{11}$  or more.

Fig. 3 Computer memory types and sizes

### 2. In-Band Signaling, the Open Front Door

In-band signaling is an open front door. There is no user authentication for control information. A black hat or prankster only needs the tools to provide the in-band control signals to the network system.

Telephone in-band signaling combines voice (data) and control information on a telephone line. The papers by Weaver and Newell<sup>3</sup> and Breen and Dahlbom<sup>4</sup> provided the technical details for controlling the telephone network. In-band signaling provides the open front door to send control information over the phone line. Back in the 1970s, before the telephone companies switched to out-of-band

signaling, a blue box generated the control tones (codes) to control the telephone network. A "blue box" built by Steve Wozniak is on display at the Computer History Museum. The average electronics hobbyist could easily build a blue box. Blue box phone calls were free. It did not take long for "free" blue box phone calls to become illegal.

The classic buffer overflow error, unfortunately all too common in modern programming, presents an opportunity for a black hat to place control information inside and gain control of a computer. The control information could be a line of code to jump to a computer virus or other malware application.

Caller ID does not have any authentication. A prank caller can easily spoof Caller ID. Caller ID uses a 1200 Hz frequency shift keying, Bell 202 modem<sup>7</sup> to send caller ID information. An "orange box" generates the spoofed Caller ID string<sup>8</sup> for the telephone network. In-band signaling is an open front door for controlling, spoofing, and/or hacking a system.

The OSFA's information assurance goal is to completely separate control and data at the hardware level. The objective is to raise the difficulty level to hack a computer system. Keep in mind that claiming a system is unhackable is like creating an unsinkable ship. Current computer security best practices are based on a risk analysis and cost/benefit analysis.

### 3. OS Friendly Microprocessor Architecture

This section describes the OSFA's cache bank architecture. Section 5 covers the cache bank and memory cell hardware permission bits.

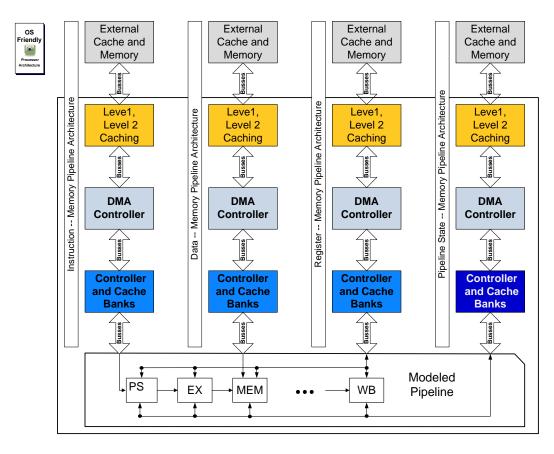

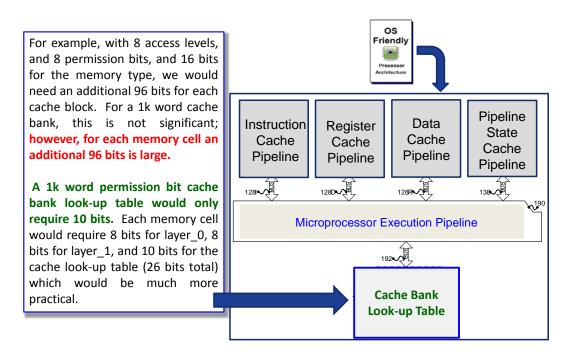

The OSFA uses an extended Harvard architecture as illustrated in Fig. 4. In a Harvard architecture (see Fig. 2), there are separate busses and memories for instructions (programs) and data. The OSFA uses 4 separate busses and memories for high-speed context switching and hardware-level information assurance. A modified extended Harvard architecture has a unified external memory with separate internal caches. A context switch only requires cache banks to be connected and disconnected to the execution pipeline. Cache bank contents are background copied to and from L1 caching while the execution pipeline is running another process or thread.

Fig. 4 OS friendly microprocessor architecture

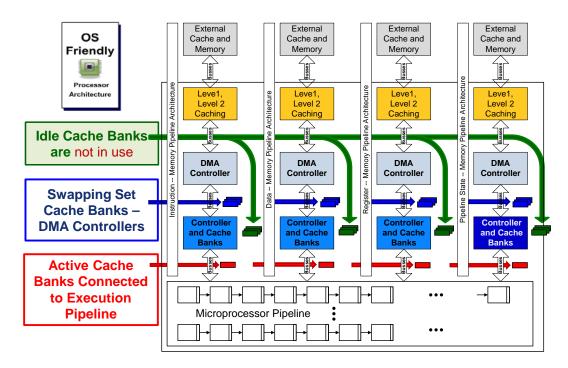

### 3.1 DMA/Cache Bank Controller Architecture

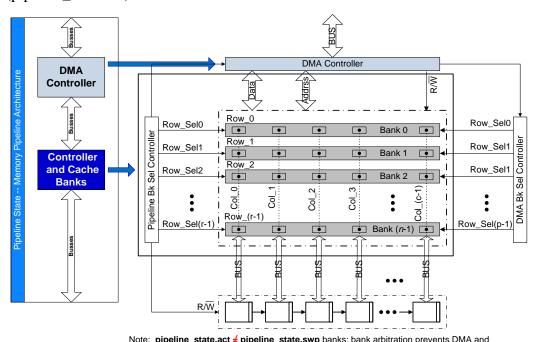

The OSFA in Fig. 5 consists of 4 DMA/cache controller banks (Instruction, Data, Register, and Pipeline State), connected to a microprocessor execution pipeline. The OSFA is a set of memory blocks (stages) in a pipeline configuration. The DMA/cache controller banks (instruction, data, register, and pipeline state) connect to internal level 1/level 2, and such, caching through busses. Internal caches connect to external caches and external memories. The OSFA can also use a unified external memory architecture similar to a modified Harvard architecture (internal separate caches for instructions and data, and a unified external memory).

Fig. 5 OS friendly DMA controller and cache bank controller pipeline architecture

The instruction, data, and register cache bank controllers are configured to only write one block at a time from/to the processor pipeline. There is a tradeoff between cache bank size and writing data in parallel. The DMA/cache bank controllers use a parallel bus to copy to (L1 and L2 caches, internal/external L3 caches, and main memory) memory. The pipeline caching structure also allows the execution pipeline to run at full speed while hardware controllers provide background cache to memory (L1 and L2 caches, internal/external L3 caches, and main memory) copy operations in parallel.

In version 1 of the OSFA,<sup>1</sup> the pipeline state controller and cache bank is fully parallel. For instruction, data, and register DMA/cache controller banks, cache memory size is more important than a fully parallel memory copy. Version 2 of the OSFA <sup>2</sup> merges the pipeline state cache banks with the execution pipeline. A parallel memory copy is not required in Version 2 <sup>2</sup> since the cache banks are already stored in the execution pipeline stages.

#### 3.2 Context Switch

A typical process is allowed to run for milliseconds before context switching to the next process. As long as the instruction, data, register, and pipeline state DMA controller/cache memory banks in Fig. 5 can complete background copy operations on the order of milliseconds, the processor does not "see" any of the background operations. Since instruction, data, register, and pipeline state memory for L1, L2,

L3 caching, and external main memory can now run at a lower clock frequency, significant power savings results without decreasing processor performance.

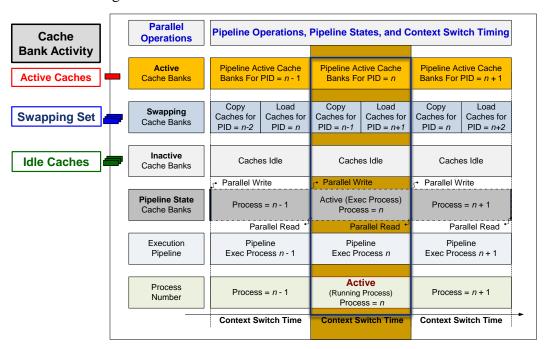

Figure 6 illustrates the OSFA Version 1<sup>1</sup> write (copy) and read (load) cache bank operations for processes n-1, n, and n+1. OSFA Version  $2^2$  removes the parallel memory copy (see Section 4.3.2). We use sequential numbers to simplify Fig. 6. In an actual system, the process identification (PID) numbers would be arbitrary. The load (read) and write (copy) cycles for each cache bank (instruction, data, register, and pipeline state) are shown. This is a worst-case example showing cache writes and loads for each context switch. Data locality would limit the number of writes and loads resulting in more time to copy memory, allowing for more power savings. Fully parallel memory copy operations, for the pipeline state cache bank, are shown (OSFA Version 1). The "Bank(m)" notation refers to cache bank number (m) or a set of bank numbers (m)'s. The instruction, data, register, and pipeline state cache controller banks consist of cache banks in 1) active use by the execution pipeline: instruction.act, data.act, register.act, and pipeline\_state.act; 2) swapping set cache banks (instruction.swp, data.swp, register.swp, pipeline\_state.swp) in use by instruction, data, register, and pipeline state DMA controllers as illustrated in Figs. 5 and 6; and 3) inactive cache banks: instruction.ina, data.ina register.ina, and pipeline state.ina not in use by execution pipeline and not in use by DMA controllers in Fig. 5.

Fig. 6 OS friendly microprocessor architecture context switch timing diagram

At process n's start, the active pipeline state cache bank (pipeline\_state.act) is copied in parallel (OSFA Version 1) into the execution pipeline latches. At the end of context for process n, the pipeline state latches (OSFA Version 1) are copied in parallel to the active pipeline state cache bank (pipeline\_state.act). During context time for process n, the inactive cache banks instruction.ina, data.ina, register.ina, and pipeline state.ina are idle. For process n-1, the swapping set cache banks instruction.swp, data.swp, register.swp, and pipeline\_state.swp are copied to L1 level caching as shown in Figs. 5 and 6. The swapping set cache banks currently in L1 cache memory, instruction, data, register, and pipeline state, for process n+1into cache banks instruction.swp(n + 1), data.swp(n + 1), register.swp(n + 1), and pipeline\_state.swp(n + 1), to prepare to execute process n + 1 during the next context time.

At end of context for process n, the active process n cache banks are set to swapping set cache banks: instruction.swp(n) = instruction.act, data.swp(n) = data.act, register.swp(n) = register.act, and pipeline\_state.swp(n) = pipeline\_state.act. After context switching from process n to process n + 1, the swapping set cache banks for process n + 1 are set to active: instruction.act = instruction.swp(n + 1), data.act = data.swp(n + 1), register.act = register.swp(n + 1), pipeline\_state.act = pipeline\_state.swp(n + 1). The cache banks instruction.act, data.act, register.act, and pipeline\_state.act and now in use by execution pipeline. Figures 5 and 6 illustrate how the instruction, data, register, and pipeline\_state DMA controllers run in parallel with the execution pipeline.

### 3.3 Cache Bank Architecture

The instruction, data, and register cache bank controllers and cache banks only need to write one word (*n* bits) at a time. Conventional microprocessors have a small number of registers: on the order of 16–128. The OSFA envisions a much larger number of registers. We envision instruction and data cache banks on the order of 128,000 or larger and register cache banks on the order of 1000 or larger. The pipeline state cache bank is on the order of 128–1000. Figure 3 compares the sizes of memories and caches for conventional architectures.

### 3.3.1 OS Friendly Microprocessor Architecture Version 1 Cache Bank

For OSFA Version 1, the pipeline state cache controller and cache banks need to be able to read or write to all of the pipeline stage latches in parallel. Figure 6 illustrates, the parallel load (read) and write operations for the pipeline state cache controller and cache banks. OSFA Version 2, in Section 4.3.2, removes the parallel read/write required for Version 1.

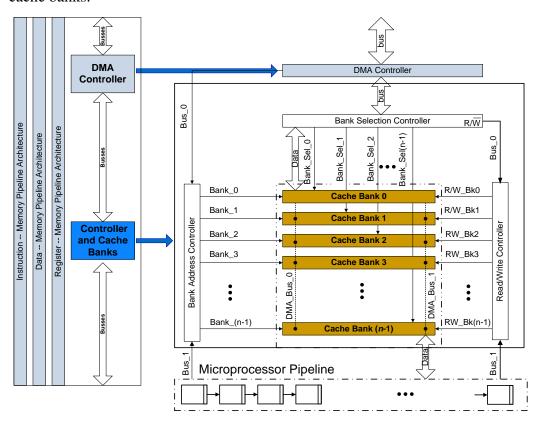

Figure 7 shows the cache controller and cache bank architecture for the instruction, data, and register banks for OSFA Versions 1 and 2. The bank selection controller provides arbitration to prevent the DMA controller and microprocessor execution pipeline from accessing the same cache bank at the same time. This separation allows the DMA to transfer cache memory pages to L1 caching in the background while the microprocessor pipeline is executing instructions. The bank address controller sets the cache bank memory addresses for the swapping set cache banks (instruction.swp, data.swp, and register.swp) and the active cache banks (instruction.act, data.act, register.act and pipeline\_state.act). The read/write controllers set the data direction for the swapping set cache banks and the active cache banks.

Fig. 7 Data, instruction, and register cache controller banks

Figure 8 shows the pipeline state cache controller and cache banks for OSFA Version 1. The pipeline state cache bank controller and DMA cache bank controller provide arbitration preventing the DMA controller and pipeline state (pipeline stage latches) from using the same cache bank at the same time. This separation allows the DMA to transfer a pipeline state cache memory bank to L1 caching in the background while the microprocessor pipeline is executing instructions. At the start of a context, as shown in Fig. 6, the active pipeline state cache bank

(pipeline\_state.act) is copied into the pipeline state (pipeline stage latches) in parallel in a single CPU clock cycle. At the end of a context, the pipeline state is copied in parallel in a single CPU clock cycle to the active pipeline state cache bank (pipeline\_state.act).

Fig. 8 Pipeline state parallel cache controller banks

execution pipeline from writing to or reading from the same cache bank at the same time.

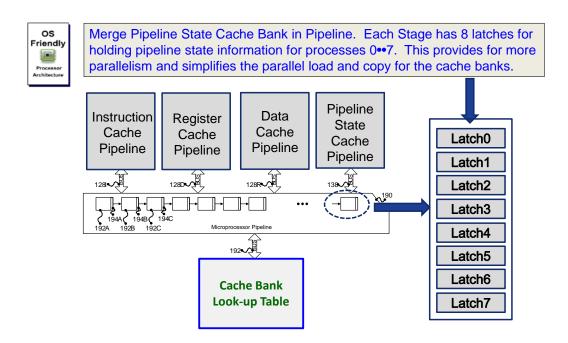

## 3.3.2 OS Friendly Microprocessor Architecture Version 2 Pipeline State Cache Bank

For the OSFA Version 2, the 8 memory latches are included in each pipeline stage as shown in Fig. 9. For example, for process n, Latch4 is currently in use. To switch to process n+1, Latch4 is disconnected from the pipeline stage, and another latch, for example Latch2, is connected. The latches used by process n may now be background copied to L1 cache sequentially from stage 0 through stage (m-1) (all of the pipeline latches) during context n+1. The Version 2 pipeline state DMA/cache controller pipeline offers the same processor performance as Version 1 while requiring less power.

Fig. 9 OS friendly microprocessor architecture version 2 pipeline state cache banks

# 3.4 OS Friendly Microprocessor Architecture Performance Modeling

The OSFA<sup>1</sup> offers new opportunities for increased performance and decreased power consumption by providing hardware features to reduce the OSs cost for managing resources. Sections 4.4.1–4.4.3 develop a first-order approximation of the potential improvements in OS Friendly Microprocessor Architecture's context switch performance. Conventional microprocessor performance models are based on the research from Vangal et. al.<sup>9</sup> and Mudge.<sup>10</sup>

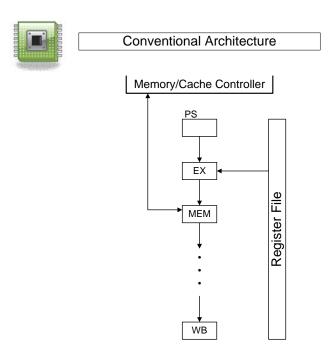

# 3.4.1 Conventional and OS Friendly Microprocessor Architecture Context Switch Modeling

Sections 4.4.2 and 4.4.3 estimate the context switch time required for a conventional architecture and the new OSFA. The OSFA significantly improves the context switch time and uses less power. The high-level representations for conventional and improved OSFA architectures are shown in Figs. 10 and 11. These figures assume the following architectural characteristics. First, the internal designs of the execution pipelines in the 2 architectures are the same. The model for the OSFA execution pipeline in Fig. 11 uses the same execution pipeline as the conventional architecture in Fig. 10. The labels inside the pipeline stages (labeled "PS") refer to the stages to which the following sections reference (EX: Execution Stage, MEM: Memory Access Stage, and WB: Writeback Stage). Next, it is assumed that the pipelines in both architectures, OSFA and conventional, operate

at a fixed voltage  $V_{P,H}$  with clock period  $t_S$ . The Register File Set (RFS), active register cache bank (**register.act**), and the active pipeline state cache bank (pipeline\_state.act) normally operate at voltage  $V_{R,H}$  with clock period  $t_S$ . For power improvements, the OSFA can dynamically scale down both the voltages and clock rates of the inactive and swapping cache controllers and cache banks. The voltage of inactive and swapping cache controllers and cache banks can be reduced to some value  $V_L$ , while the clock frequency (clock period) of these components can be reduced (clock period increased) to some value, clock frequency  $f_L$ , or clock period  $t_L$ .

Fig. 10 Conventional processor architecture model

Fig. 11 OS friendly microprocessor architecture model

### 3.4.2 Conventional Architecture Context Switch Modeling

This section presents the steps taken by conventional processor architecture in Fig. 10 to perform a context switch. Each step requires a certain period of time, which is determined by the amount of work required by the step, the clock rate of the components involved, and the parallelism exploited by these components. All components of the conventional architecture operate with the short clock period  $t_s$ . The steps involved in a context switch for the conventional processor are shown in Table 1.

Table 1 Conventional architecture context switch steps

| Step   | Description                                                                     |

|--------|---------------------------------------------------------------------------------|

| Step 1 | Flush the pipeline state out to the register file.                              |

| Step 2 | Write out each register value to memory.                                        |

| Step 3 | Bring the OS register state back into the register file.                        |

| Step 4 | Refill the pipeline with the OSs pipeline state.                                |

| Step 5 | Execute the standard OS operations.                                             |

| Step 6 | Flush the OS pipeline state to the register file.                               |

| Step 7 | Write out each register value to memory.                                        |

| Step 8 | Bring the register state of another process, $p$ , back into the register file. |

| Step 9 | Refill the pipeline with <i>p</i> 's state.                                     |

Assuming the conventional pipeline in Fig. 10 has s stages, step 1 will require s clock ticks, and hence  $s \cdot t_S$  time. Step 2, writing each register file out to memory, requires reading each register value into the EX stage, moving it into the MEM stage, and then flushing it out to memory. There are 3 clock ticks for each register value, but since the operations can be performed in a pipelined fashion, we approximate this as  $r \cdot t_S$  time total for all r registers. Step 3 requires filling up the pipeline to retrieve register values from memory, requiring s ticks, then writing each value back to the register file in the writeback stage for a total of  $(s + r) \cdot t_S$  time. Step 4 is filling the pipeline back up with values from the register file, but this can be pipelined with the register file refill and hence is already accounted for. Step 5 takes some unknown amount of time,  $t_{OS\_NORMAL}$ , that is dependent on the OS design. Steps 6 and 7 are similar to steps 1 and 2, which again require  $s \cdot t_S$  time and  $r \cdot t_S$  time, respectively. Step 8 is like step 3, which requires  $(s + r) \cdot t_S$  time, and step 9 is like step 4, which is accounted for in this time. Hence, an expression that approximates this entire process is given by Eq. 1 and simplified in Eq. 2.

$$t_{CS_{CONV}} = st_S + rt_S + (s+r)t_S + t_{OS_{NORMAL}} + st_S + rt_S + (s+r)t_S.$$

(1)

$$t_{CS_{CONV}} = 4t_S(r+s) + t_{OS_{NORMAL}}$$

(Conventional Architecture's Context Switch Time) (2)

# 3.4.3 OS Friendly Microprocessor Architecture Context Switch Modeling (Version 1)

Figure 6 presents a worst-case timing diagram for the OSFA Version 1 assuming swapping set cache banks (**instruction.swp**, **data.swp**, **register.swp**, and **pipeline\_state.swp**) must be loaded and written for every context switch. Data locality will significantly reduce the number of cache bank memory copy operations. The model for OSFA's execution pipeline in Fig. 11 is same as the

conventional architecture described in Section 4.4.2 and Fig. 10. A more optimized pipeline would provide higher performance.

The OSFA pipeline model also operates with clock period  $t_S$ . In the determination of the clock frequency of the OSFA's other components, the cache banks are divided into 3 sets: **act**ive, **ina**ctive, and **swap**ping set. One of the register cache banks, register.**act**, is active and one of the pipeline state caches, pipeline\_state.**act**, is active. These active cache banks are those that are in use by the OSFA pipeline in Fig. 4 and the modeled pipeline in Fig. 11. There is then a set of the other cache banks, **instruction.bank**(m)'s, **data.bank**(m)'s, **register.bank**(m)'s and **pipeline\_state.bank**(m)'s, that are either flushing state out to the DMA controllers (instruction DMA, data DMA, register DMA, pipeline state DMA) or bring state back from the DMA controllers (instruction DMA, data DMA, register DMA, pipeline state DMA). These sets are designated as the swapping sets where

instruction.swp = set of instruction.bank(m)'s cache memory banks,

data.swp = set of data.bank(m)'s cache memory banks,

register.swp = set of register.bank(m)'s cache memory banks, and

pipeline\_state.swp = set of pipeline\_state.bank(m)'s cache memory banks.

The cache banks not in use by the execution pipeline or DMA controllers are **ina**ctive or idle.

The active components instruction.act, data.act, register.act and pipeline\_state.act operate with clock period  $t_S$ , the swapping components instruction.swp, data.swp, register.swp and pipeline\_state.swp operate with the longer clock period  $t_L$ , and the inactive components instruction.ina, data.ina, register.ina and pipeline\_state.ina are idle (for static memory, clock frequency could be set to 0 Hz).

The modeled OSFA Version 1 in Fig. 11 performs the following steps in Table 2 during a context switch. The key feature of the OSFA is that parallelism takes place at various levels to reduce execution time. In step 1, all pipeline stages flush state to the active pipeline state cache simultaneously (see Figs. 5, 6, and 11), and hence this requires only one tick at the high clock rate for a time of  $t_s$ .

Table 2 OS friendly microprocessor architecture version 1 context switch steps

| Step   | Description                                                                                                                                                                                                                                                  |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Step 1 | Flush the pipeline state (pipeline stage latches) out to the active pipeline state cache.                                                                                                                                                                    |

| Step 2 | Switch the active cache banks to the OS state                                                                                                                                                                                                                |

| Step 3 | If necessary (if free slots in the pipeline_state cache bank and register cache bank are needed), flush the contents of the previous process' state cache banks for the previous process ID (PID) as described in Figure 6.                                  |

| Step 4 | Bring the OSs pipeline state back into the pipeline from the pipeline state cache.                                                                                                                                                                           |

| Step 5 | Execute the standard OS operations.                                                                                                                                                                                                                          |

| Step 6 | Flush the pipeline state out to the active pipeline state cache <b>pipeline_stage.act</b> .                                                                                                                                                                  |

| Step 7 | If necessary, fetch the state of the next process for execution from memory into the next process' cache banks.                                                                                                                                              |

| Step 8 | Switch the active cache banks to the caches containing new (next) process (for example, next PID): pipeline_state.act = pipeline_state(next PID), register.act = register(next PID), instruction.act = instruction(next PID), and data.act = data(next PID). |

| Step 9 | Parallel copy the contents of the active pipeline state cache back into the pipeline stage latches. Section 4.4.3 describes the parallel copy for pipeline state cache controller and pipeline state cache banks.                                            |

Step 2 also takes a single tick to switch to the set of active cache banks for the next PID: instruction.act = instruction(next PID), register.act = register(next PID), data.act = data(next PID), and pipeline\_state.act = pipeline\_state (next PID).

Step 3 takes s ticks for the pipeline state cache and r ticks for the register file. However, these steps can be completed at the same time as steps 4–6, so as long as they are completed in at most the time for those steps, the pipeline will not see them. It is reasonable to assume that step 3 can be completed in less time (if, for the time being, we ignore cache misses and contention), as the pipeline state and register file are relatively small, while the OS must generally perform several system operations before switching back to a user-level process.

Step 4 is the reverse of step 1, so it requires only a single tick.

Step 5 still takes  $t_{OS\_NORMAL}$  as with the conventional architecture, and step 6 takes a single tick like step 1. Step 7 is the reverse of step 3 and requires the same amount of time. Again, these steps can be performed in parallel with those of steps 4–6.

Step 8 is the same as step 2, and step 9 is the same as step 4. Each of these takes one tick. Hence, the total time for the OSFA context switch,  $t_{CS\_OSFA}$ , is found in Eq. 3 and simplified in Eq. 4.

$$t_{CS\ OSFA} = t_S + t_S + t_S + t_{OS\ NORMAL} + t_S + t_S + t_S. \tag{3}$$

$$t_{CS\ OSFA} = 6t_S + t_{OS\ NORMAL}. (4)$$

We will ignore the  $t_{OS\_NORMAL}$  term by assuming it is the same for conventional and OSFA. The speedup offered by the OSFA for context switching is estimated to be  $CT\_Speedup_{OSFA}$  in Eq. 5. For example, for a 5-stage pipeline, s = 5, and 32 general-purpose registers, r = 32, this translates to an estimated theoretical speedup of 25 found in Eq. 5 for OSFA. This is a significant order of magnitude speedup improvement for the OSFA compared with the conventional processor architecture.

$$CT\_Speedup_{OSFA} \approx \frac{4st_S + 4rt_S}{6t_S} \approx \frac{2}{3}(s+r) = \frac{2}{3}(5+32) = 25$$

For OSFA Context Switch. (5)

In Eq. 6 for a large number of registers,  $r \gg s$ , and for  $t_{OS\_NORMAL} \gg 6t_S$ , with  $t_S \lesssim \frac{1}{100 \, \text{MHz}}$ , the speedup is order the number of registers,  $\mathcal{O}(r)$ .

$$CT\_Speedup_{OSFA} = \frac{_{4st_S + 4rt_S + t_{OS\_NORMAL}}}{_{6t_S + t_{OS\_NORMAL}}} \approx \frac{_{4st_S + 4rt_S + t_{OS\_NORMAL}}}{_{t_{OS\_NORMAL}}} \approx \frac{_{4r}}{_{t_{OS\_NORMAL}}} \approx \mathcal{O}(r). \tag{6}$$

# 3.4.4 OS Friendly Microprocessor Architecture Context Switch Modeling (Version 2)

OSFA Version 2 pipeline state cache bank in Fig. 9 has the same context switch speedup found in Eq. 5. The parallel memory copy for version 1 was replaced by a background serial memory copy as described in Section 4.3.2. The serial memory copy only requires a low-speed clock. Power requirements for the serial memory copy are less than the full parallel memory copy used in version 1 described in Section 4.4.3.

# 4. OS Friendly Microprocessor Architecture Hardware Computer Security

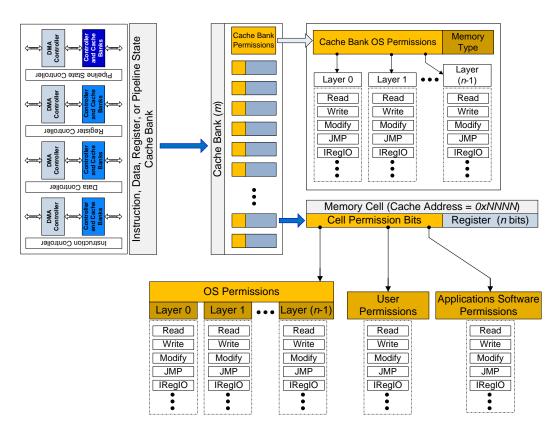

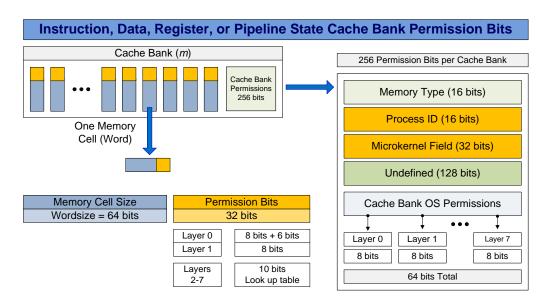

OS information assurance for "data" (instruction cache banks, data cache banks, register cache banks, pipeline state cache banks, and memory cells) is implemented in hardware. By extending the traditional Unix file permissions bits<sup>11–13</sup> down to each memory cell, memory cache line, and cache memory bank, the OSFA provides hardware-level information assurance. Figure 12 illustrates hardware-level information assurance hierarchy and permission bits.<sup>1</sup>

Fig. 12 Cache bank and memory cell hardware information assurance

### 4.1 Cache Bank and Memory Cell Permission Bits

The instruction, data, register, and pipeline state cache banks have a set of OS level permission bits. The cache bank memory type field is used to define data types (e.g., data space, stack space, heap space, integer, floating point). Only the OS has permission to access and modify cache banks' permission bits. OS level access to cache controller banks is divided into access layers (layer\_0, layer\_1, layer\_2, etc.). Example permission bits are shown in Fig. 12. Each cache memory bank has permission bits for each memory cell. Each cache bank memory cell has permission bits for the OS layers and software (user level, and applications, etc.). The OS permission bits are further divided in OS layers (layer\_0, layer\_1, etc.). Additional permission bits can easily be added to Fig. 12.

#### 4.2 Instruction Permission Bits

The OSFA also includes permission bits for additional OS level control over instructions and hardware. In Fig. 12, permission bit **JMP** provides OS level control of jump or branch on index register instructions. Permission bit **IRegIO** allows OS to provide an index register pointing to an I/O port or I/O memory address. The **IRegIO** bit locks out the index register (pointer). The running process is prevented

from accessing the contents of the register/cache bank; however, the process can use the index register (pointer) to read/write to I/O (registers, ports, or addresses). Registers can be used to define data types using 2 registers for minimum value and maximum value. For example, the type IOMemAddressType could be defined as minimum = 0, and maximum = 15. If a register of type IOMemAddressType is outside the minimum/maximum range, then the processor will generate an out-of-range exception.

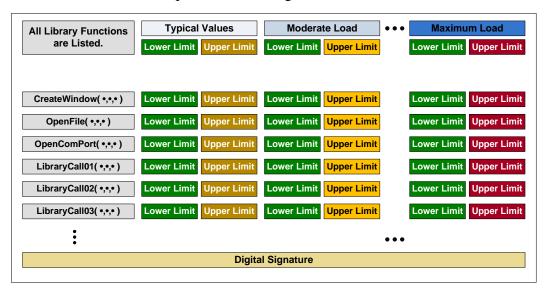

### 4.3 Library Call Permissions

The library function call table in Fig. 13 extends the principal of least privilege to the library function call level. A table listing all possible library function calls a software program may use is created. Each possible library function call is listed with typical moderate load and maximum load lower and upper limits. More limits could be used for finer grain control as in the example of the OpenFile(•) library function call privilege limits. If the minimum number of open files is 0, the lower limits for cases typical, moderate, and maximum is 0. If the typically user will only have 5 files open at a time, the upper limit for typical is 5. Maximum load upper limit specifies the maximum number of files that may be open at a time. Exceeding the upper limits can be set to 1) require higher than user level privileges or to 2) generate an exception. The digital signature provides authentication of the library function call table and its permission settings.

Fig. 13 Library function call table information assurance

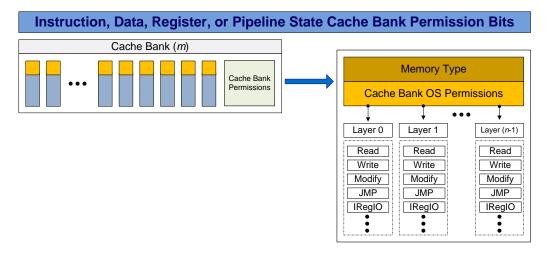

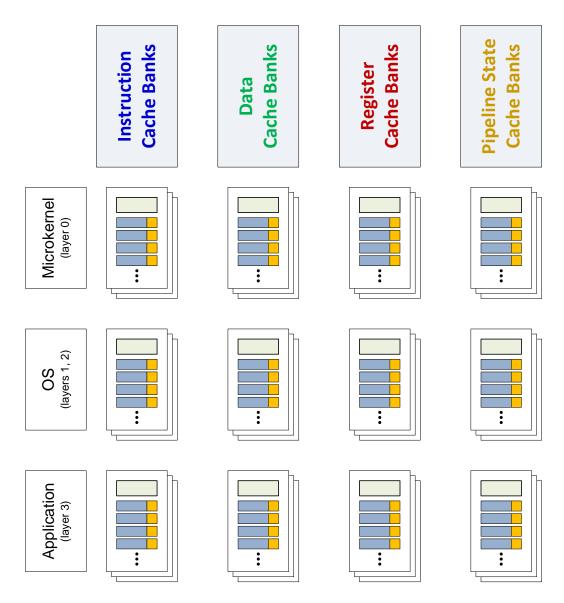

### 5. OS Friendly Microprocessor Architecture Access Layers

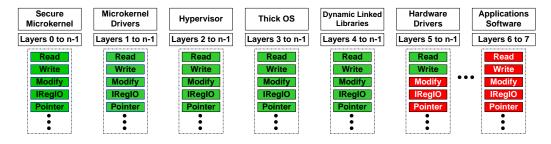

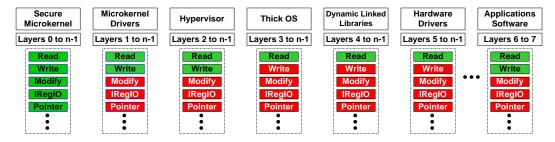

Figure 12 introduces the cache bank permission bits for the OSFA. The instruction, data, register, and pipeline state cache banks all use the same block of permission bits. Figure 14 focuses on the cache bank permission bits. Each cache bank contains a memory type field. The memory type field can be used to define stack space, heap space, user memory, shared memory and the like. Each cache bank contains a list of permission bits for the OS rings or OS layers. One possible hierarchy for the OS Layers is found in Table 3. The secure microkernel and microkernel drivers control all permission bits and manage I/O and memory allocation.

Fig. 14 OS friendly microprocessor architecture cache bank permission bits

Table 3 Example OS friendly microprocessor architecture layer hierarchy

| Layer Number | Trust Level | OS Access Level        |  |  |

|--------------|-------------|------------------------|--|--|

| Layer_0      | Complete    | Secure Microkernel     |  |  |

| Layer_1      |             | Microkernel Drivers    |  |  |

| Layer_2      |             | Hypervisor             |  |  |

| Layer_3      |             | Thick OS               |  |  |

| Layer_4      |             | Dynamic Link Libraries |  |  |

| Layer_5      |             | OS Drivers             |  |  |

| Layer_6      |             | •••                    |  |  |

| Layer_7      | Untrusted   | Applications Software  |  |  |

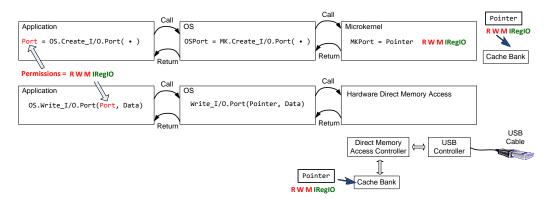

As illustrated in Fig. 5, all memory, and I/O is managed as direct memory access. For example, an application writes a block of data to a hard drive. The application executes file.create(•). The OS level file operation calls the secure microkernel for an I/O port. The secure microkernel passes a pointer to an I/O port. The pointer to the port address is marked R W M IRegIO (read, write, and modify

are not allowed, IRegIO specifies pointer to I/O port). We will use the notation R W M for read, write, and modify are allowed. The OS cannot read, write, or modify the value of the pointer. The application then calls file.write(•) using the pointer. The OS can only use the file pointer for I/O for the file.write(•) OS library function call. Microkernel can manage (run) multiple OSs and programs at the same time.

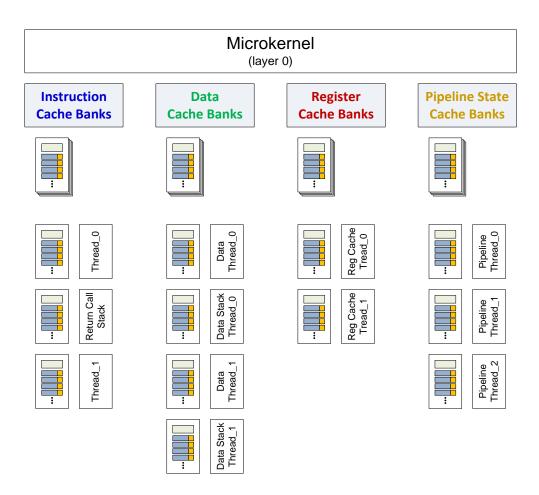

## 5.1 Instruction, Data, Register, and Pipeline State Memory Partitions

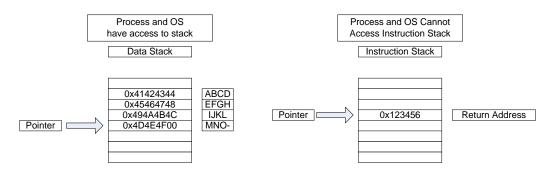

The instruction, data, register, and pipeline state cache banks all use the same permission bits. The memory type field in Fig. 14 restricts the information that can be placed in the cache bank. For example, if the cache bank type is set to application data, the running task or thread cannot use the cache bank as stack space. For a cache bank to be used for stack space, the stack space permission bit must be set. For a push or pull stack operation to read or write to a stack cache bank, an index pointer must have stack permission bit set. Stack registers will also be marked as R W M (read, write, modify are not allowed), so the running task cannot modify the contents of the stack pointer (register).

Instructions and data have their own stack space (cache banks). For example, an array of data is placed on the stack to call an OS library function. The return address is not data and is placed on a separate stack contained in the instruction cache bank. The stack spaces are not unified. The data stack does not contain any return addresses. The instruction stack is managed by the microkernel, so the OS and application do not have any direct access to the return address pointer. The return address pointer can also be set to R W M (read, write, modify are not allowed).

The next section looks at permission bits for different OS access levels covered in Table 3.

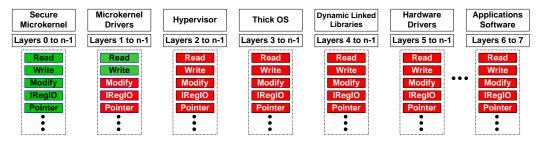

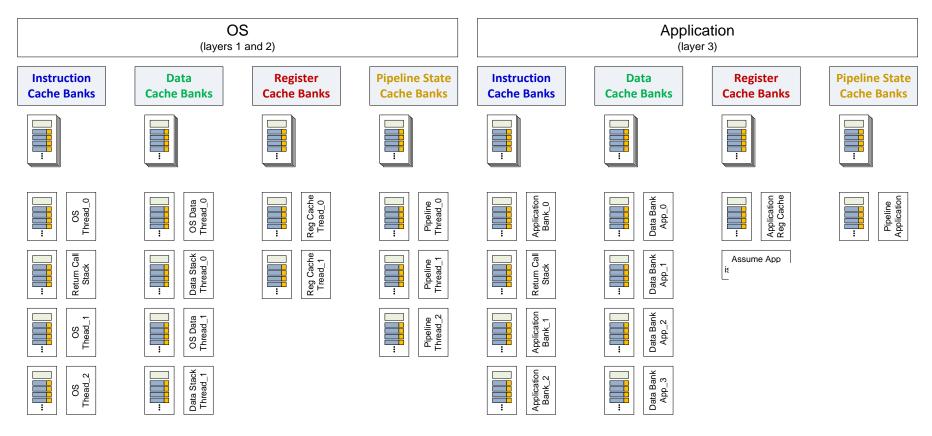

# 5.2 Permission Bits: Microkernel, Thick OS, Drivers, and Applications

Figures 15–17 provide example permission bit settings. Figure 15 shows permission bit settings for the secure microkernel, the most secure layer. The microkernel has complete access. Microkernel drivers have read and write access. In Fig. 16, the full feature OS and dynamic link libraries are set to access layers 3 (OS) or 4 (DLL) through n-1. OS hardware drivers are set to read and write access only. The application's permission bits are shown in Fig. 17. The multiple levels of permission bits allow for restricting the OS from writing to applications' areas of memory. Keep in mind that each cache bank memory can have different permission

bit settings. The OS could have full control over one application's cache memory bank and have no control or visibility to a second application's cache memory bank. The large number of permission bits allows for fine grain memory access control. We could set the permission bits to allow a trusted application to run under an untrusted OS. The permission bits allow for hardware sandbox execution of unknown, untrusted code. The hardware permission bits require that we at least completely trust the secure microkernel. A formal proof of correctness or a very high assurance level microkernel is recommended.

Fig. 15 Secure microkernel cache banks and permission bits

Fig. 16 Thick OS cache banks and permission bits

Fig. 17 Application's permission bits

### 5.3 I/O Implementation

The OSFA uses cache banks and direct memory access controllers for I/O. The cache bank architecture allows all I/O to have a uniform structure. In a high-level programming language, we use file operations like file.open(•), file.write(•), and file.read(•). The file function calls provide a uniform

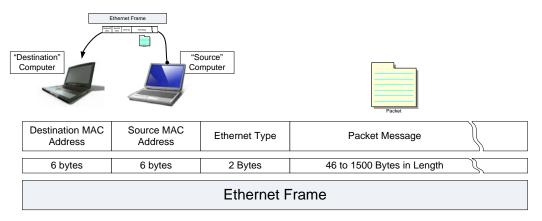

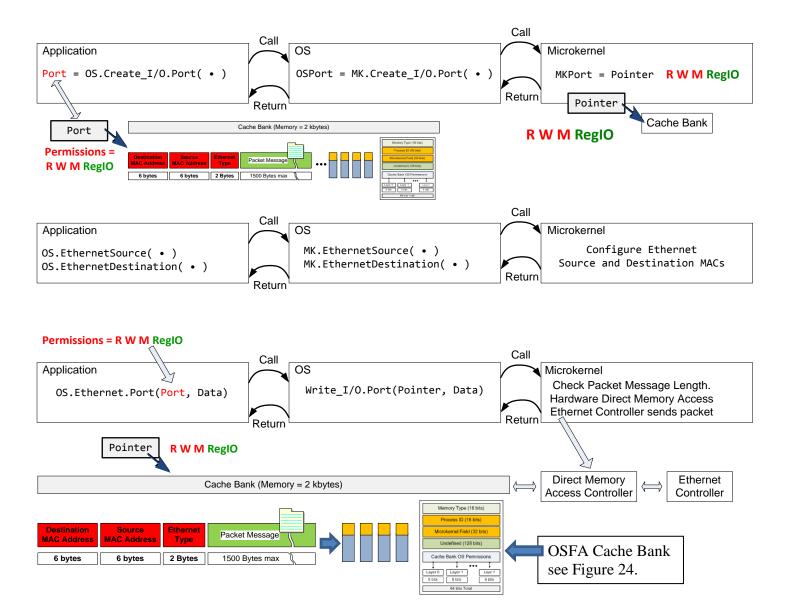

structure abstracting the low-level details away from the programmer. By using cache banks and direct memory access for all input and output, all I/O operations at the hardware level are the same. As illustrated in Fig. 18, a USB controller interfaces to a direct memory access controller. This allows cache banks to be the basic block for all input and output operations. We could replace the USB controller with a disk drive controller or a video graphics card. The cache bank and direct memory access controller provide a universal interface between the OSFA and other devices.

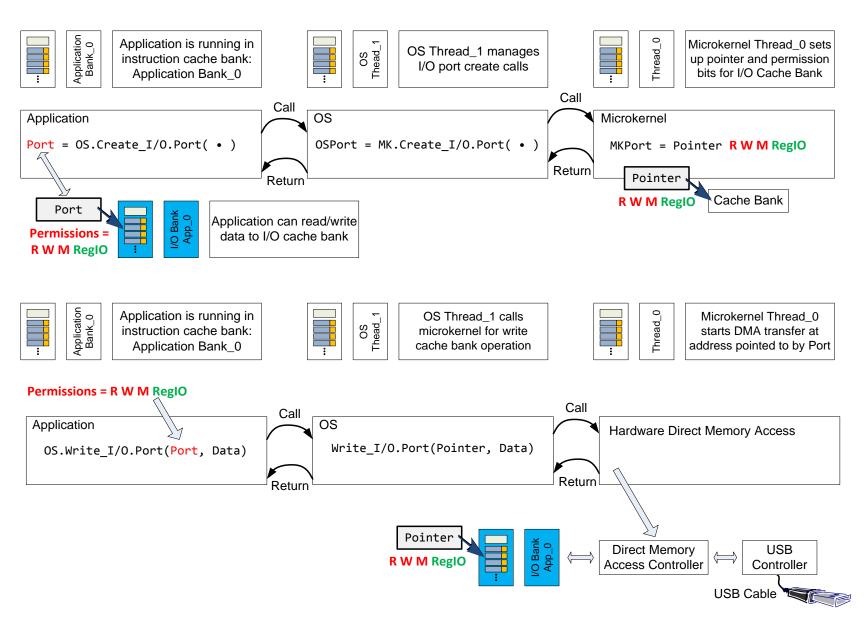

Fig. 18 OS friendly microprocessor architecture I/O example

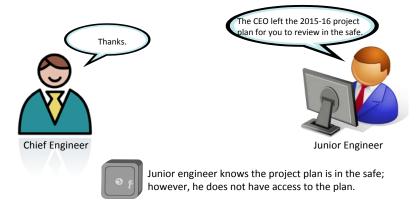

In Fig. 18, the software applications calls the library function OS OS.Create.I/O Port(•). The OS calls the microkernel function MK.Create.I/O\_Port(•) to create a pointer to a cache bank. The pointer has permission bits set to R W M **IReg10**. The OS and applications software cannot read, write, modify, or access the contents of the index register (pointer). All the OS and application know is that the index register, for example register 10 (R10), contains a pointer to the I/O port. Figure 19 gives a real-world example for comparison. The junior engineer knows the project plan is contained in the safe; however, he does not have access to the project plan.

Fig. 19 Real-world example of OS friendly microprocessor architecture's permission architecture