# RECONFIGURABLE ELECTRONICS AND NON-VOLATILE MEMORY RESEARCH

Kristy A. Campbell

Boise State University Department of Electrical & Computer Engineering 1910 University Drive Boise, ID 83725-2075

10 Nov 2015

**Final Report**

APPROVED FOR PUBLIC RELEASE; DISTRIBUTION IS UNLIMITED.

AIR FORCE RESEARCH LABORATORY

Space Vehicles Directorate

3550 Aberdeen Ave SE

AIR FORCE MATERIEL COMMAND

KIRTLAND AIR FORCE BASE, NM 87117-5776

# DTIC COPY NOTICE AND SIGNATURE PAGE

Using Government drawings, specifications, or other data included in this document for any purpose other than Government procurement does not in any way obligate the U.S. Government. The fact that the Government formulated or supplied the drawings, specifications, or other data does not license the holder or any other person or corporation; or convey any rights or permission to manufacture, use, or sell any patented invention that may relate to them.

This report is the result of contracted fundamental research deemed exempt from public affairs security and policy review in accordance with SAF/AQR memorandum dated 10 Dec 08 and AFRL/CA policy clarification memorandum dated 16 Jan 09. This report is available to the general public, including foreign nationals. Copies may be obtained from the Defense Technical Information Center (DTIC) (http://www.dtic.mil).

AFRL-RV-PS-TR-2015-0151 HAS BEEN REVIEWED AND IS APPROVED FOR PUBLICATION IN ACCORDANCE WITH ASSIGNED DISTRIBUTION STATEMENT.

//SIGNED// ARTHUR EDWARDS Program Manager //SIGNED//

JAMES LYKE

Tech Advisor, Space Electronics Protection Branch

//SIGNED//

JOHN BEAUCHEMIN

Chief Engineer, Spacecraft Technology Division

Space Vehicles Directorate

This report is published in the interest of scientific and technical information exchange, and its publication does not constitute the Government's approval or disapproval of its ideas or findings.

# REPORT DOCUMENTATION PAGE

Form Approved OMB No. 0704-0188

Public reporting burden for this collection of information is estimated to average 1 hour per response, including the time for reviewing instructions, searching data sources, gathering and maintaining the data needed, and completing and reviewing the collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden to Washington Headquarters Service, Directorate for Information Operations and Reports, 1215 Jefferson Davis Highway, Suite 1204, Arlington, VA 22202-4302, and to the Office of Management and Budget, Paperwork Reduction Project (0704-0188) Washington, DC 20503.

PLEASE DO NOT RETURN YOUR FORM TO THE ABOVE ADDRESS.

| 1. REPORT DATE                                                            | 2. REPORT TYPE                                           | 3. DATES COVERED                                                       |

|---------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------------------|

| 10-11-2015                                                                | Final Report                                             | 04 Sep 2008 – 30 Oct 2015                                              |

| 4. TITLE AND SUBTITLE                                                     |                                                          | 5a. CONTRACT NUMBER                                                    |

| Reconfigurable Electron                                                   | nics and Non-Volatile Memory Research                    | FA9453-08-2-0252                                                       |

|                                                                           |                                                          | 5b. GRANT NUMBER                                                       |

|                                                                           |                                                          | 5c. PROGRAM ELEMENT NUMBER<br>62601F                                   |

| 6. AUTHOR(S)<br>Kristy A. Campbell                                        |                                                          | 5d. PROJECT NUMBER<br>4846                                             |

|                                                                           |                                                          | 5e. TASK NUMBER<br>PPM00004127                                         |

|                                                                           |                                                          | 5f. WORK UNIT NUMBER<br>EF002546                                       |

| Boise State University                                                    | ATION NAME(S) AND ADDRESS(ES)  Il & Computer Engineering | 8. PERFORMING ORGANIZATION REPORT NUMBER                               |

| 9. SPONSORING/MONITOR<br>Air Force Research Lab<br>Space Vehicles Directo |                                                          | 10. SPONSOR/MONITOR'S ACRONYM(S) AFRL/RVSE                             |

| 3550 Aberdeen Ave SE<br>Kirtland AFB, NM 8711                             |                                                          | 11. SPONSORING/MONITORING AGENCY REPORT NUMBER AFRL-RV-PS-TR-2015-0151 |

| 12. DISTRIBUTION AVAILA                                                   | BILITY STATEMENT                                         | -                                                                      |

Approved for public release; distribution is unlimited.

#### 13. SUPPLEMENTARY NOTES

#### 14. ABSTRACT

The purpose of this research was to investigate reconfigurable electronics and non-volatile memory materials and devices. The primary focus of this work was on device types such as ion-conducting resistive, zero-field splitting memory theory (atomic or molecular memory devices that operate based on a specific quantum mechanical property referred to as zero-field splitting of the atoms/molecules held within a material matrix), as well as multi-state chalcogenide devices based on a layered chalcogenide material structure. Devices were fabricated as single elements or as arrays of devices in order to test their performance. Materials characterization was used to aid in an understanding of device operation and to ultimately improve device performance through better material selection.

#### 15. SUBJECT TERMS

Electronics, memory, nonvolatile, phase change, space

| 16. SECURITY CLASSIFICATION OF: |              |              | 18. NUMBER<br>OF PAGES | 19a. NAME OF RESPONSIBLE PERSON<br>Arthur Edwards |                                          |

|---------------------------------|--------------|--------------|------------------------|---------------------------------------------------|------------------------------------------|

| a. REPORT                       | b. ABSTRACT  | c. THIS PAGE |                        |                                                   | 19b. TELEPONE NUMBER (Include area code) |

| Unclassified                    | Unclassified | Unclassified | Unlimited              | 100                                               |                                          |

# TABLE OF CONTENTS

| Secti | ion        |                                                                     | Page     |

|-------|------------|---------------------------------------------------------------------|----------|

| List  | of Figures |                                                                     | iii      |

| List  | of Tables  |                                                                     | viii     |

| 1     | SUMMAR     | Y                                                                   | 1        |

| 2     | INTRODU    | CTION                                                               | 3        |

| 2.    | 1 Ion-Co   | nducting, Resistance Variable Memory Devices (Memristors)           | 3        |

| 2.2   | 2 Atomic   | or Molecular Memory Based on ZFS                                    | 5        |

| 2.3   | 3 Phase-   | Change Multi-State Memory                                           | 8        |

| 3     | METHODS    | S, ASSUMPTIONS, AND PROCEDURES                                      | 10       |

| 3.    | 1 Genera   | l Experimental Methods                                              | 10       |

|       | 3.1.1 Fa   | brication                                                           | 10       |

|       | 3.1.2 M    | ask Layouts                                                         | 12       |

|       | 3.1.2.1    | In-via layout                                                       | 12       |

|       | 3.1.2.2    | 10 x 10 and 150 x 150 array layouts                                 | 12       |

|       | 3.1.2.3    | ZFS mask layout.                                                    | 13       |

|       | 3.1.3 M    | aterial Characterization and Fabrication Process Step Qualification | 14       |

|       | 3.1.3.1    | Raman spectroscopy.                                                 | 14       |

|       | 3.1.3.2    | n&k tool.                                                           | 15       |

|       | 3.1.3.3    | UV-Vis                                                              | 15       |

|       | 3.1.3.4    | SEM imaging.                                                        | 15       |

|       | 3.1.3.5    | EPR spectroscopy.                                                   | 15       |

|       | 3.1.4 El   | ectrical                                                            | 16       |

|       | 3.1.4.1    | Single device measurements                                          | 16       |

|       | 3.1.4.2    | 10 x 10 and 150 x 150 crossbar array measurements                   | 18       |

|       | 3.1.4.3    | ZFS device measurements                                             | 20       |

| 3.2   | 2 Approa   | ach to Ion-Conducting, Resistance Variable Memory Devices (Memris   | tors) 21 |

| 3.3   | 3 Approa   | ach to Atomic or Molecular Memory Based on ZFS                      | 24       |

| 3.4   | 4 Approa   | ach to Phase-Change Multi-State Memory                              | 26       |

| 4     | RESULTS    | AND DISCUSSION                                                      | 27       |

| 4.    | 1 Ion-Co   | nducting, Resistance Variable Memory Devices (Memristors)           | 27       |

|      | 4.1.1   | Metal Cosputtered Films and Devices                                | 30 |

|------|---------|--------------------------------------------------------------------|----|

|      | 4.1.1   | .1 Raman                                                           | 31 |

|      | 4.1.1   | 2 UV-Vis                                                           | 32 |

|      | 4.1.1   | .3 EPR of Thin Films and Bulk                                      | 35 |

|      | 4.1.1   | .4 Electrical Characterization                                     | 36 |

|      | 4.1.2   | Cu vs Ag Devices                                                   | 41 |

|      | 4.1.3   | S vs Se Devices                                                    | 46 |

|      | 4.1.4   | Differential Negative Resistance Testing                           | 54 |

|      | 4.1.5   | Constant Current Source Testing                                    | 54 |

|      | 4.1.6   | Spike-Timing-Dependent-Plasticity Testing                          | 55 |

|      | 4.1.7   | High Frequency Electrical Testing as a Function of Temperature     | 55 |

|      | 4.1.8   | PECVD Deposition of Ti-doped Ge <sub>x</sub> Se <sub>y</sub> Films | 61 |

|      | 4.1.9   | Device Fabrication on 300 mm Wafers                                | 65 |

|      | 4.1.10  | BEOL Development for ASU IC Test Chip                              | 66 |

|      | 4.1.11  | Theoretical Calculations                                           | 71 |

| 4.   | 2 Ato   | mic or Molecular Memory Based on ZFS                               | 72 |

| 4.   | 3 Pha   | se-Change Multi-State Memory                                       | 74 |

|      | 4.3.1   | RIT Collaboration                                                  | 74 |

|      | 4.3.2   | EXAFS Collaboration                                                | 74 |

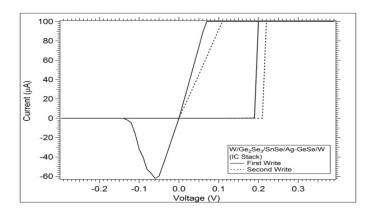

|      | 4.3.3   | Electrical characterization of layered devices                     | 75 |

|      | 4.3.4   | Micron Technology 300 mm Wafer Tests                               | 75 |

| 5    | CONCI   | LUSION                                                             | 78 |

| REF  | ERENC   | ES                                                                 | 80 |

| 1 15 | T OF SY | MROLS ABBREVIATIONS AND ACRONYMNS                                  | 84 |

# LIST OF FIGURES

| Figure Page                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1. (left) Cross-section illustration of an example device structure. (right) Optical top-down image of a fabricated device. The device is located in the center       |

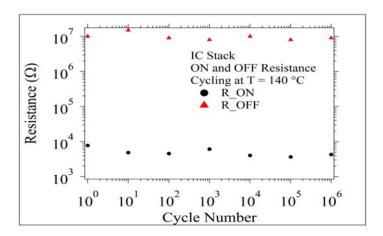

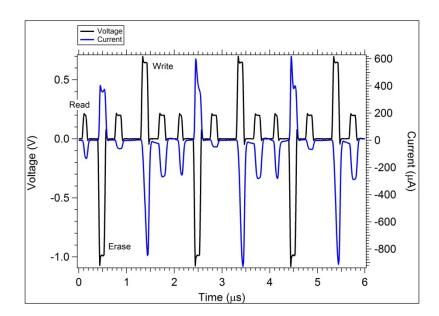

| Figure 2. IC stack device cycling response at $T = 140 ^{\circ}\text{C}$ .                                                                                                   |

| Figure 3. Electron spin energy level diagram of Mn³+ in the protein Manganese Superoxide Dismutase                                                                           |

| Figure 4. Microwave absorption at zero magnetic field from a sample of $Na_2O$ -CaO-MgO-SiO <sub>2</sub> glass doped with 0.1 wt. %MnO <sub>2</sub> . Data collected at 77K  |

| Figure 5. Electron paramagnetic resonance of bulk GeSe-Mn glasses at 4.2 K. A zero-field splitting signature was observed in the $(Ge_{40}Se_{60})_{97}Mn_3$ sample, circled |

| Figure 6. Current-voltage curve for a typical phase-change memory material                                                                                                   |

| Figure 7. Cross sectional drawing of a stacked layer phase-change memory device. Ch denotes either S, Se, or Te                                                              |

| Figure 8. Common bottom electrode process flow                                                                                                                               |

| Figure 9. Isolated bottom electrode process flow                                                                                                                             |

| Figure 10. Isolated bottom electrode in-via layout. Top electrode is on the right (varying length lines) and bottom electrode is the square on the left                      |

| Figure 11. Optical image of a completed 10 x 10 array and portion of 150 x 150 array. The wafer image of the 150 x 150 array is in the center and contains 12 die            |

| Figure 12. Front panel of the 150 x 150 testing program showing the layout of electrical contacts to the array                                                               |

| Figure 13. One and Two Port device layouts                                                                                                                                   |

| Figure 14. Test structures on ZFS layout. Not shown is the short test structure                                                                                              |

| Figure 15. Raman spectra of Ge <sub>2</sub> Se <sub>3</sub> films collected under different processing conditions 15                                                         |

| Figure 16. SEM image of evaporated SnSe film above a layer of W                                                                                                              |

| Figure 17. Continuous-wave device measurement circuit schematic for the pulse generator and scope measurement technique                                                      |

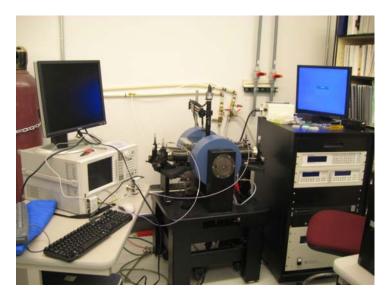

| Figure 18. Test set up for the CW measurement using the test set up in Figure 17, showing an IV curve measured for a memristor device                                        |

| Figure 19. Probe station for pulsed measurements showing the WGFMUs (right and left, rear) 17                                                                                |

| Figure 20. Cold temperature probe station                                                                                                                                    |

| Figure 21. From left to right: Completed array test station; custom decoder board, 300 pin wafer probe card; 10 x 10 probe card; PXI matrix interface board                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 22. The completed PXI memristor test system showing the PXI based drive electronics (right) and the measurement fixtures (left) configured for package-based testing                     |

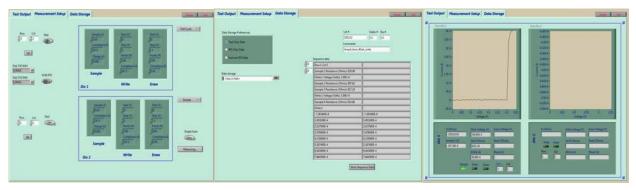

| Figure 23. Data collection software user interfaces for the memristor test platform                                                                                                             |

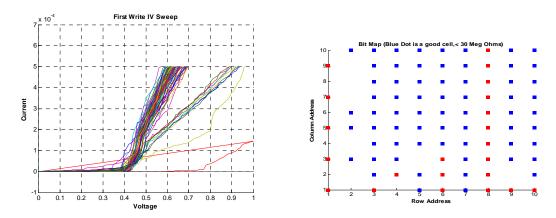

| Figure 24. (left) Matlab generated IV plots from 10 x 10 array test data produced by the automated PXI test system. (right) red indicates failed bit; blue good bit                             |

| Figure 25. ZFS layout device high frequency test station equipped with a LakeShore EMPX-HF magnetic probe station and an Agilent N5224A PNA Microwave Network Analyzer                          |

| Figure 26. Multi-state memory cell concept for ZFS. With three transition metal ions in the cell, there are potentially three separate ZFS energies                                             |

| Figure 27. Bit reading scheme for ZFS array row                                                                                                                                                 |

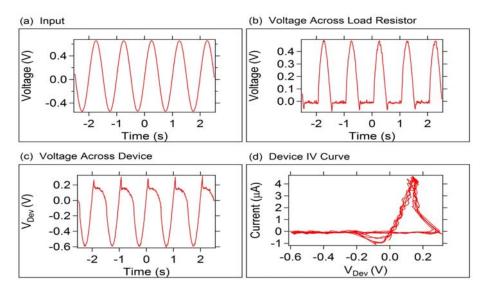

| Figure 28. DC voltage sweep of IC stack                                                                                                                                                         |

| Figure 29. IC stack CW response. 28                                                                                                                                                             |

| Figure 30. Resistance for the ON and OFF states as a function of cycle number for a device operating continuously at $T = 140  ^{\circ}C$                                                       |

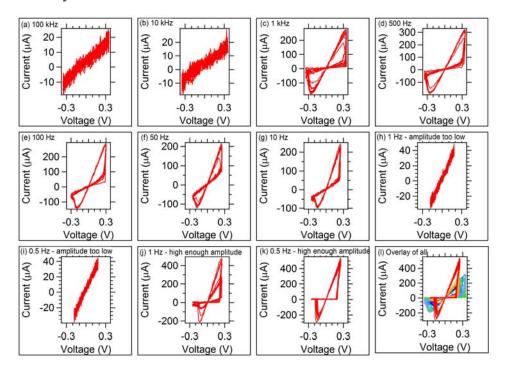

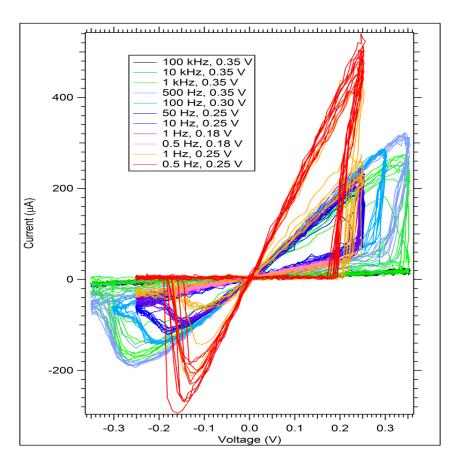

| Figure 31. IV curve for IC stack memristor per sinusoidal input frequency and peak amplitude in order tested (a)-(k). An overlay of all of the frequency response IV curves is given in (l) 29  |

| Figure 32. The overlay plot from the previous figure of the IV curves taken as a function of sinusoidal signal excitation for an IC stack memristor                                             |

| Figure 33. Example ICP-MS analysis for Ti-cosputtered films. The power for the Ti target was varied from 0 to 25 W; the corresponding increase in Ti concentration was measured                 |

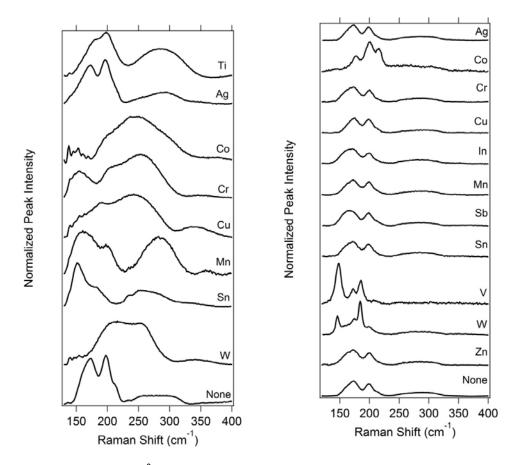

| Figure 34. 300 Å thin film (left) and bulk Raman spectra for metal doped (3 at% in bulk; 5-9% in film) Ge <sub>2</sub> Se <sub>3</sub>                                                          |

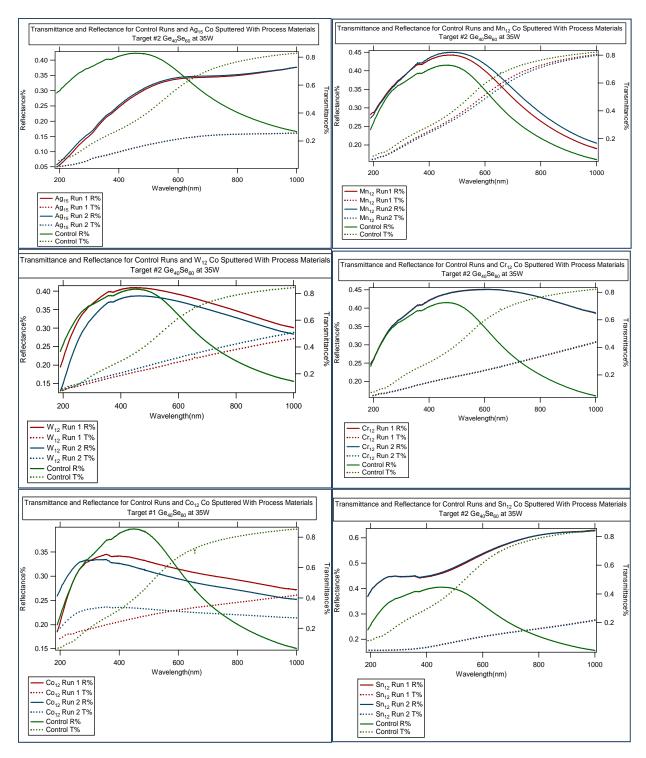

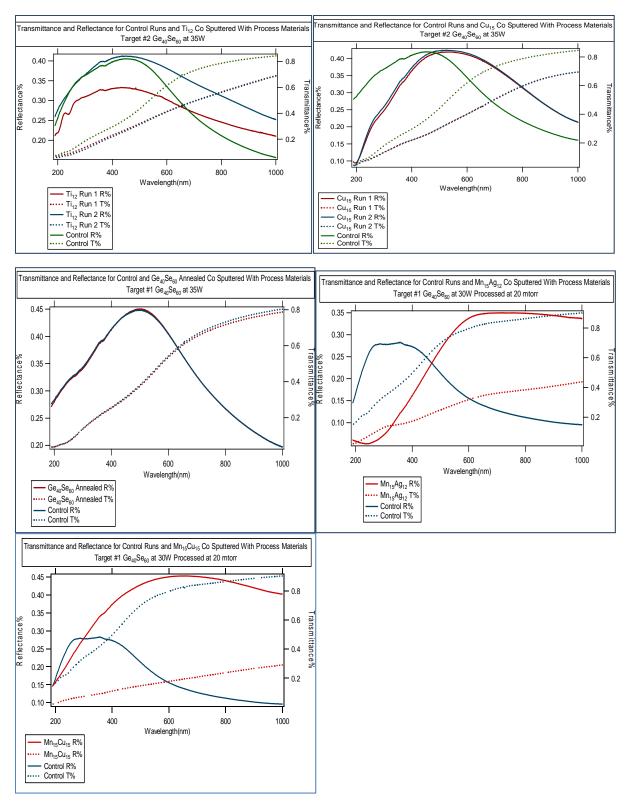

| Figure 35. UV-Vis reflection and transmission spectra for cosputtered metal-Ge <sub>2</sub> Se <sub>3</sub> films, 300 Å thick. Note the metal subscript corresponds to deposition target power |

| Figure 36. UV-Vis reflection and transmission spectra for cosputtered metal-Ge <sub>2</sub> Se <sub>3</sub> films. Note the metal subscript corresponds to deposition target power              |

| Figure 37. Mylar strips with thin films deposited on them. These strips are then stacked and placed in an EPR tube                                                                              |

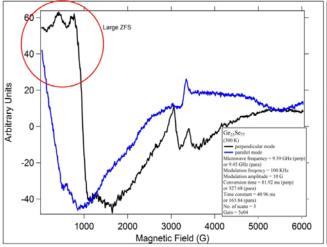

| Figure 38. EPR spectra of $Ge_{23}Se_{77}$ bulk glass at $T=300$ under parallel and perpendicular mode magnetic field within the microwave cavity                                               |

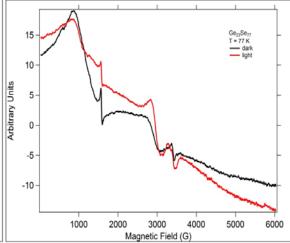

| Figure 39. EPR spectra of Ge <sub>23</sub> Se <sub>77</sub> at 77 K (illuminated and dark); perpendicular mode 36                                                                               |

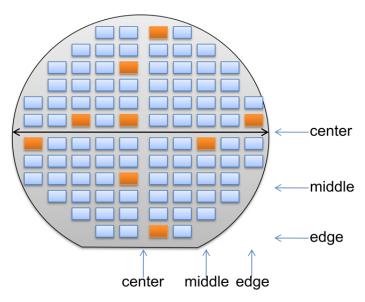

| Figure 40. Wafer map for typical electrical characterization. Die in orange were tested with E sweeps                                                        |           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

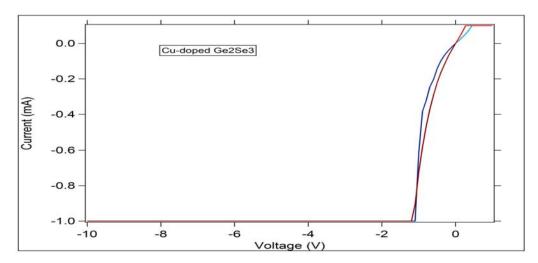

| Figure 41. IV curve of Cu-cosputtered device. Note that the device did not switch resistance.                                                                | 38        |

| Figure 42. IV curve for a device with a Ti-cosputtered Ge <sub>2</sub> Se <sub>3</sub>                                                                       | 39        |

| Figure 43. IV curve of a device containing a Ti-cosputtered Ge <sub>2</sub> Se <sub>3</sub> active layer in an IC stack configuration without the SnSe layer |           |

| Figure 44. IV curve of a Cr-cosputtered Ge <sub>2</sub> Se <sub>3</sub> device                                                                               | 40        |

| Figure 45. IV curve of a Sn-cosputtered Ge <sub>2</sub> Se <sub>3</sub> device that appears operational                                                      | 40        |

| Figure 46. IV curve of Sn-cosputtered Ge <sub>2</sub> Se <sub>3</sub> device that is non-functional                                                          | 41        |

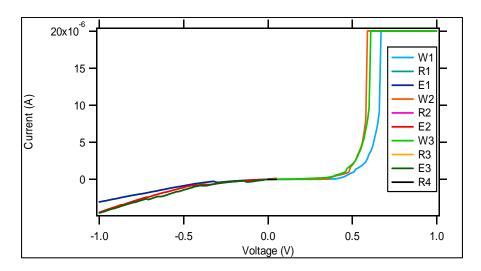

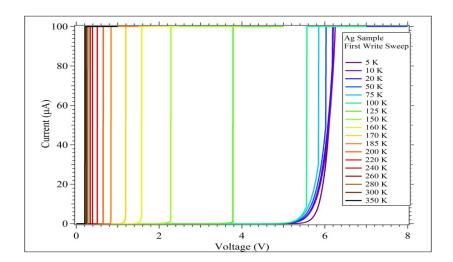

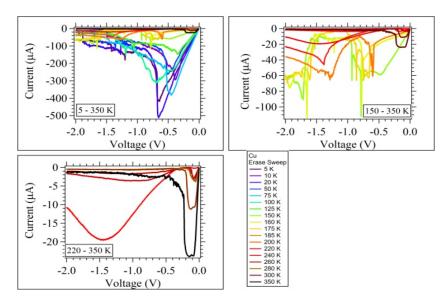

| Figure 47. First write sweep as a function of temperature for Ag-based IC stack devices                                                                      | 42        |

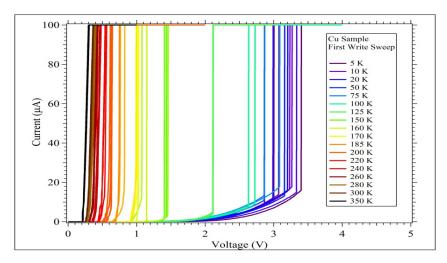

| Figure 48. First write sweep as a function of temperature for Cu-based IC stack devices                                                                      | 42        |

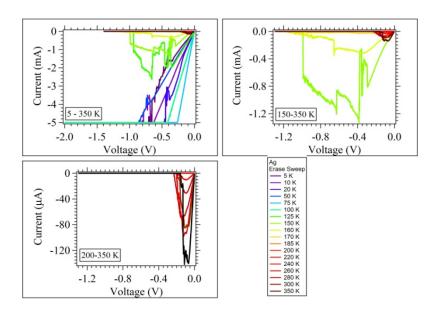

| Figure 49. IV erase sweeps for Ag-based IC stack devices per temperature. Clockwise from upper left: all temperatures; 150 to 350 K; and 200 to 350 K        | 43        |

| Figure 50. IV erase sweeps for Cu-based IC stack devices per temperature. Clockwise from upper left: all temperatures; 150 to 350 K; and 200 to 350 K        | 43        |

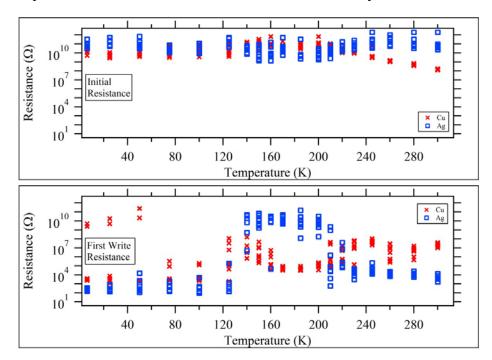

| Figure 51. Initial and first write resistances for the Ag- and Cu-based IC stack devices as a function of temperature                                        | 44        |

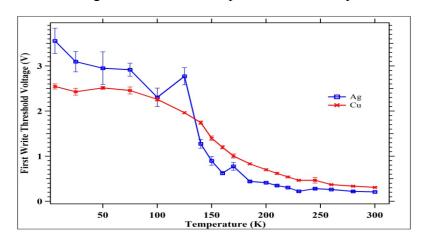

| Figure 52. First write threshold voltages as a function of temperature for the Ag- and Cu-base IC stack devices                                              | d<br>. 44 |

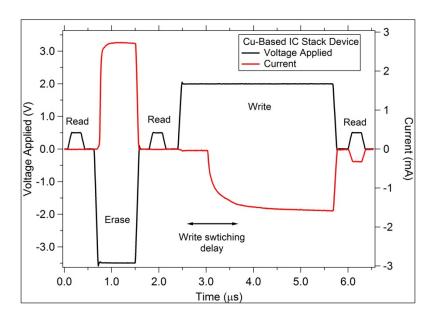

| Figure 53. Pulsed programming response of a typical Cu-based IC stack device at room temperature                                                             | 45        |

| Figure 54. Pulsed programming response of a typical Ag-based IC stack device at room temperature.                                                            | 46        |

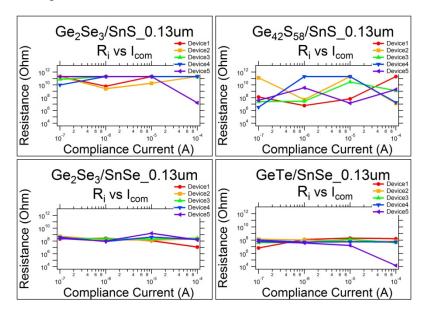

| Figure 55. Initial resistance (Ri) for the 0.13 um Se vs S device DC Sweeps                                                                                  | 47        |

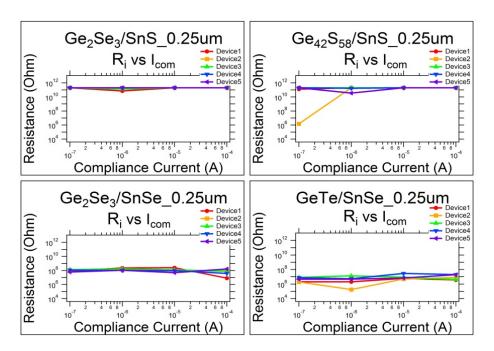

| Figure 56. Initial resistance (Ri) for the 0.25 um Se vs S device DC Sweeps                                                                                  | 48        |

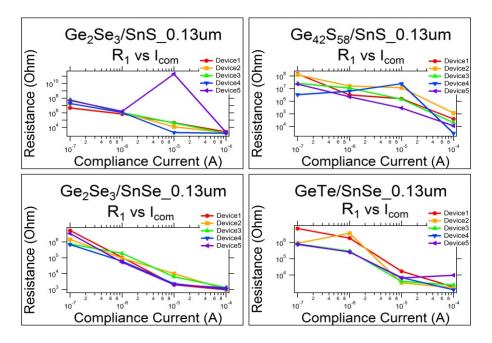

| Figure 57. First write resistance (R1) for the 0.13 um Se vs S device DC Sweeps                                                                              | 48        |

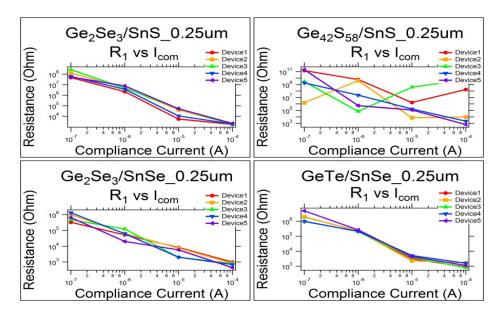

| Figure 58. First write resistance (R1) for the 0.25 um Se vs S device DC Sweeps                                                                              | 49        |

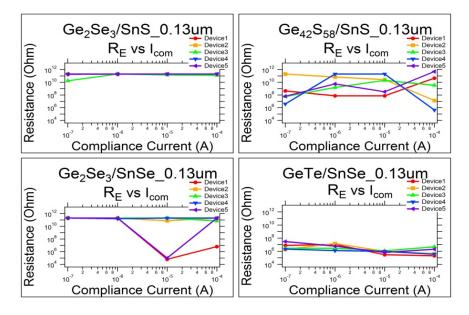

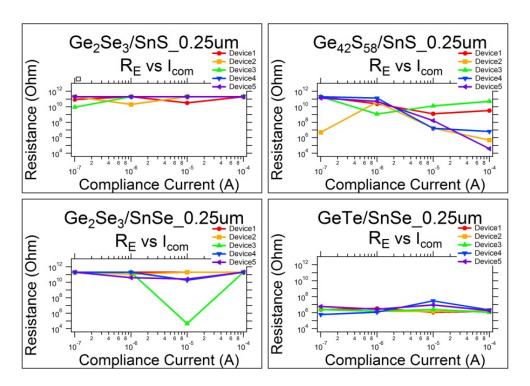

| Figure 59. Erase resistance (RE) for the 0.13 um Se vs S device DC Sweeps                                                                                    | 49        |

| Figure 60. Erase resistance (RE) for the 0.25 um Se vs S device DC Sweeps                                                                                    | 50        |

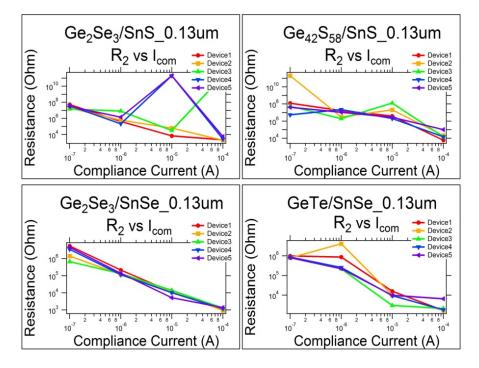

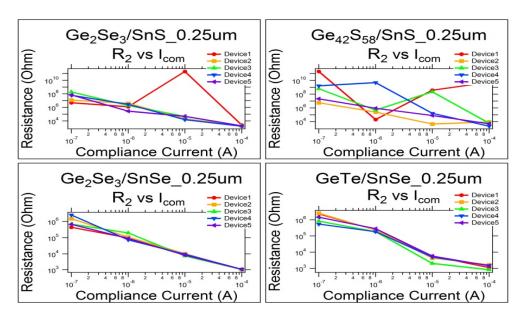

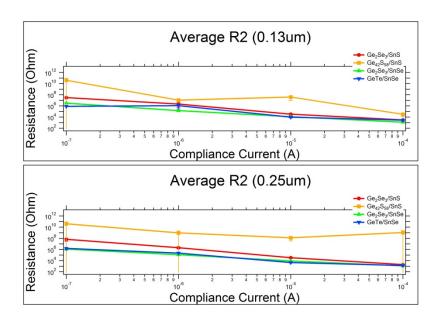

| Figure 61. Second write resistance (R2) for the 0.13 um Se vs S device DC Sweeps                                                                             | 50        |

| Figure 62. Second write resistance (R2) for the 0.25 um Se vs S device DC Sweeps                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

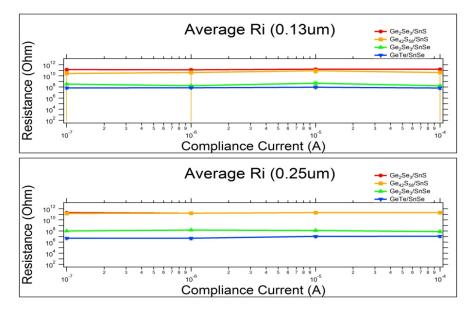

| Figure 63. Average initial resistance for each device type and size. Error bars represent one standard deviation                                                                 |

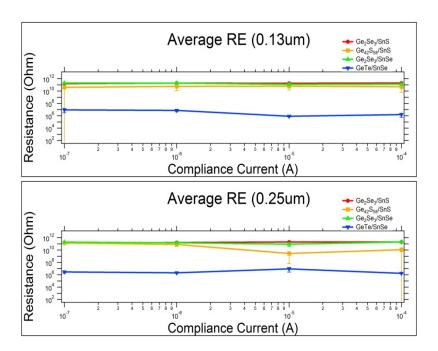

| Figure 64. Average erased resistance for each device type and size. Error bars represent one standard deviation                                                                  |

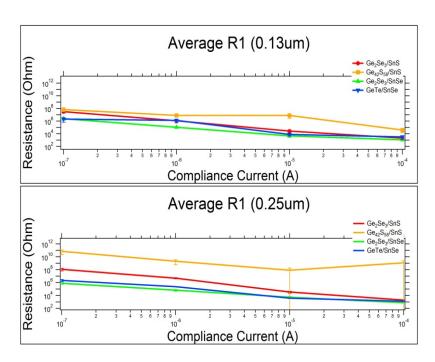

| Figure 65. Average first write resistance for each device type and size. Error bars represent one standard deviation                                                             |

| Figure 66. Average second write resistance for each device type and size. Error bars represent one standard deviation                                                            |

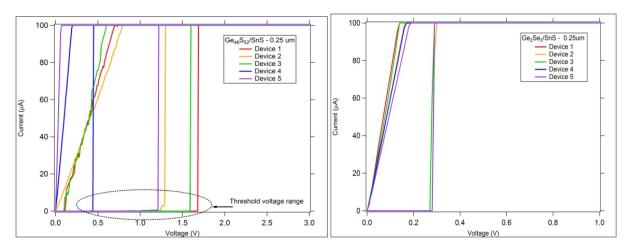

| Figure 67. IV curve for the first write sweep of devices with the Ge <sub>48</sub> S <sub>52</sub> /SnS stack (left) and the Ge <sub>2</sub> Se <sub>3</sub> /SnS stack (right). |

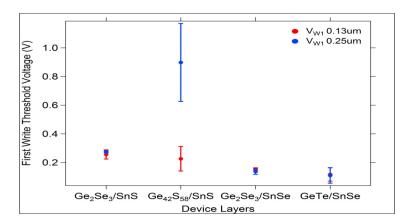

| Figure 68. Average first write threshold voltage for each device type and size. Error bars represent one standard deviation                                                      |

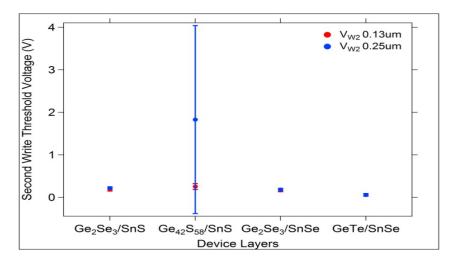

| Figure 69. Average second write threshold voltage for each device type and size. Error bars represent one standard deviation                                                     |

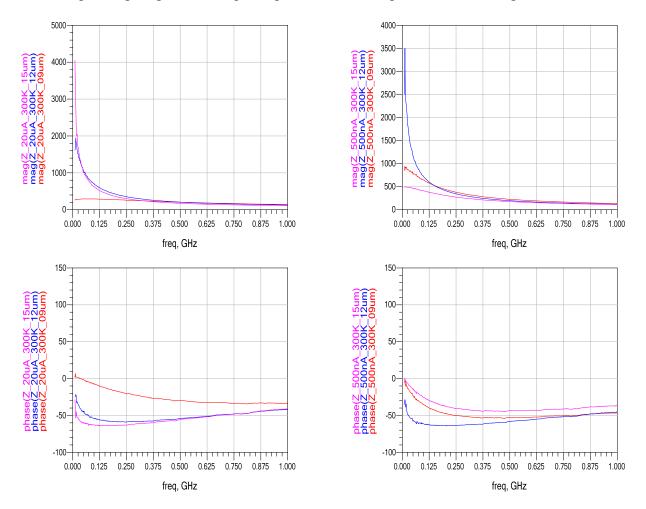

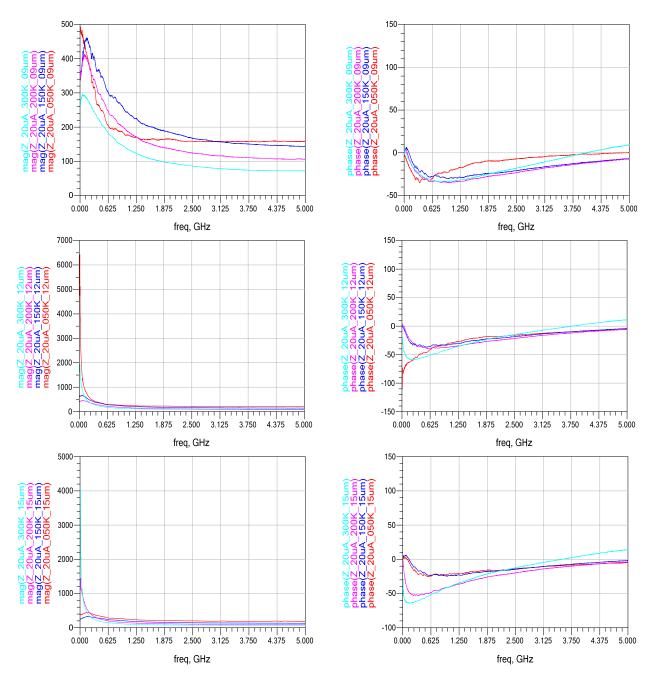

| Figure 70. The magnitude (top) and phase (bottom) plots for each device size. (left column) 20 uA compliance current; (right) 500 nA compliance. T=300 K                         |

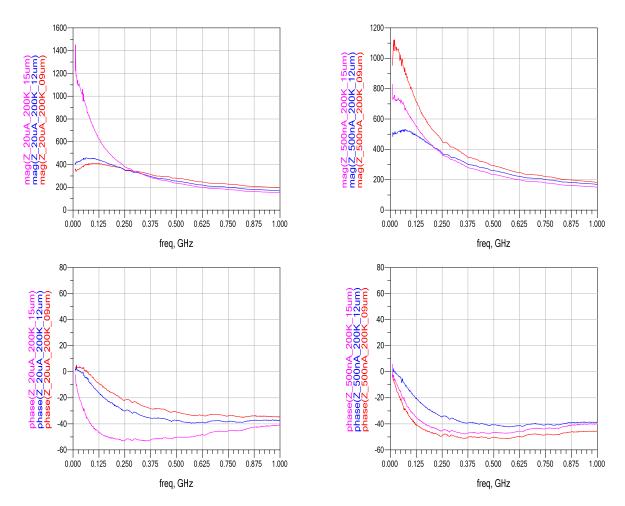

| Figure 71. The magnitude (top) and phase (bottom) plots for each device size. (left column) 20 uA compliance current; (right) 500 nA compliance. T=200 K                         |

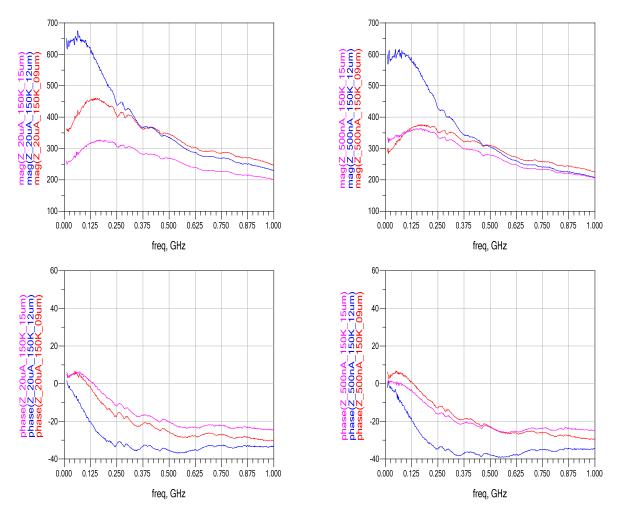

| Figure 72. The magnitude (top) and phase (bottom) plots for each device size. (left column) 20 uA compliance current; (right) 500 nA compliance. T=150 K                         |

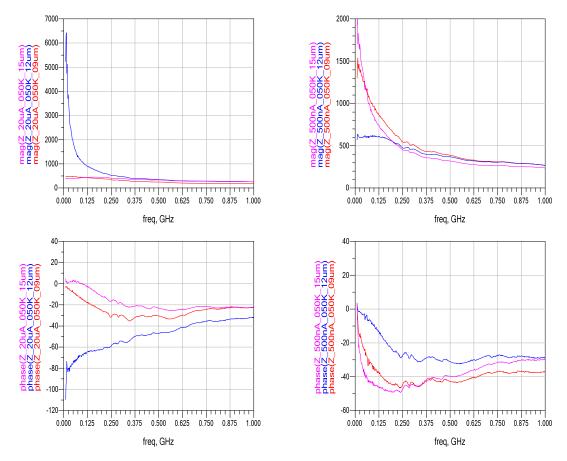

| Figure 73. The magnitude (top) and phase (bottom) plots for each device size. (left column) 20 uA compliance current; (right) 500 nA compliance. T=50 K                          |

| Figure 74. A comparison of all 20 uA programmed magnitude and phase device data, at each temperature. (top) 9 um device; (mid) 12 um; (bottom) 15 um                             |

| Figure 75. A comparison of all 500 nA programmed magnitude and phase device data, at each temperature. (top) 9 um device; (mid) 12 um; (bottom) 15 um                            |

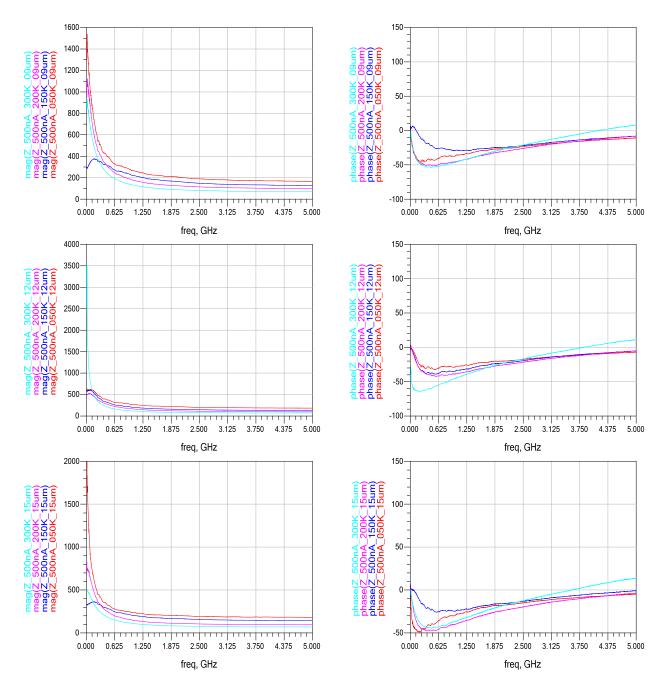

| Figure 76. The device structure used for the PECVD film tests (top) and an optical image of a completed wafer                                                                    |

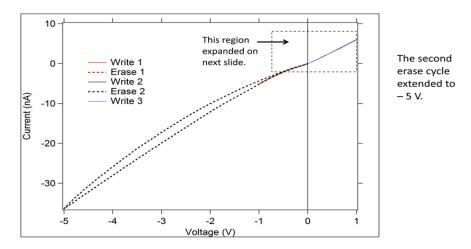

| Figure 77. IV curve of Ge <sub>2</sub> Se <sub>3</sub> /Ag. No Ti doping                                                                                                         |

| Figure 78. The expanded region of the IV curve in the Figure 77                                                                                                                  |

| Figure 79. IV curve of a device with PECVD Ti-Ge <sub>2</sub> Se <sub>3</sub>                                                                                                    |

| Figure 80. IV curve of the required negative potential conditioning sweep used to 'form' the device                                                               |          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Figure 81. IV curve of Ti-doped PECVD device pre and post conditioning to form the char<br>Before channel formation, the device was volatile                      |          |

| Figure 82. 300 mm wafers processed at Micron with visible damage                                                                                                  | 66       |

| Figure 83. Incoming die layout. The BEOL masks must align to this existing die                                                                                    | 67       |

| Figure 84. Incoming die top most metal layer. This is the memristor bottom electrode                                                                              | 67       |

| Figure 85. Incoming die passivation openings and alignment marks                                                                                                  | 67       |

| Figure 86. BEOL mask 1, opens metal and device vias                                                                                                               | 68       |

| Figure 87. BEOL mask 2, bottom electrode bond pad definition                                                                                                      | 68       |

| Figure 88. BEOL overlay of mask 1 and 2                                                                                                                           | 68       |

| Figure 89. BEOL mask 3 opening bottom electrode contact and via                                                                                                   | 69       |

| Figure 90. BEOL mask 4, top electrode definition                                                                                                                  | 69       |

| Figure 91. Overlay of all four BEOL mask layers                                                                                                                   | 69       |

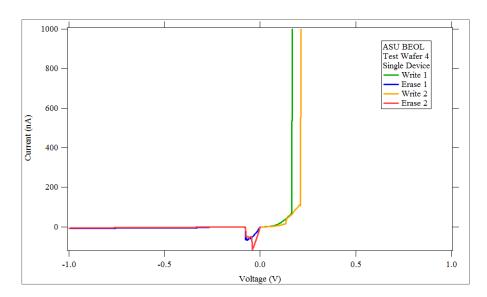

| Figure 92. IV curve of control wafer processed with the BEOL mask design for ASU's test. The memristor fabrication process using the BEOL mask set was successful |          |

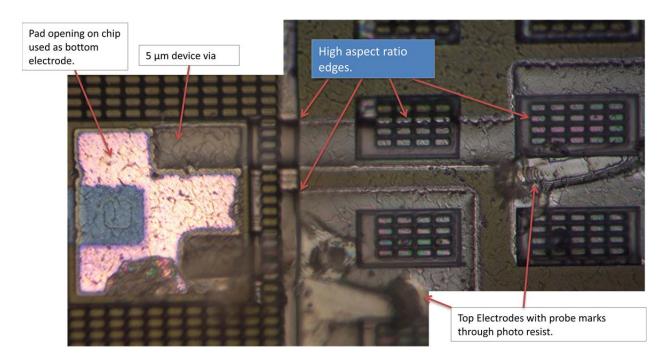

| Figure 93. Image of a die post BEOL processing.                                                                                                                   | 71       |

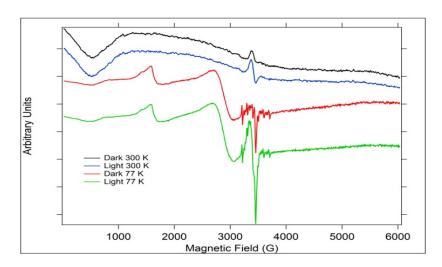

| Figure 94. Ge <sub>2</sub> Se <sub>3</sub> EPR spectra at 300 and 77 K under dark and light conditions                                                            | 72       |

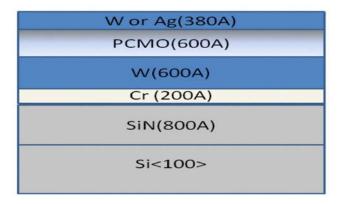

| Figure 95. PCMO device testing material stack. Films for some analysis (such as SEM) place PCMO on nitride directly                                               |          |

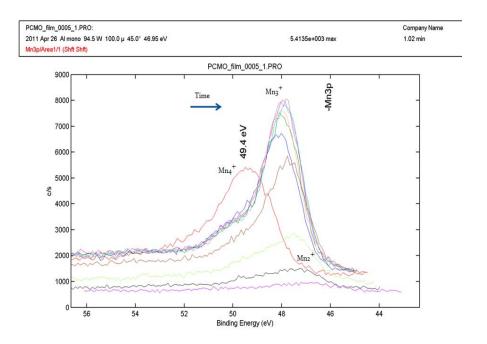

| Figure 96. XPS spectra binding energy of Mn in PCMO film                                                                                                          | 73       |

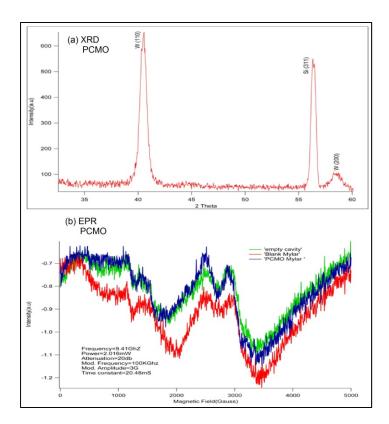

| Figure 97. XRD (a) and EPR (b) of PCMO thin films. The EPR spectra was collected in the parallel mode because of the predominant Mn <sup>3+</sup> species in PCMO | 1e<br>74 |

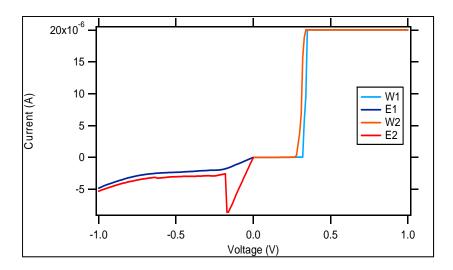

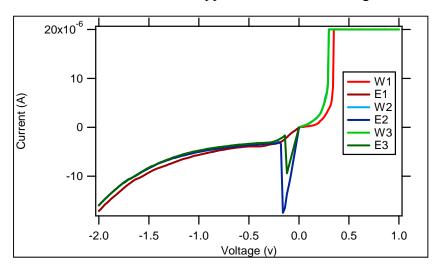

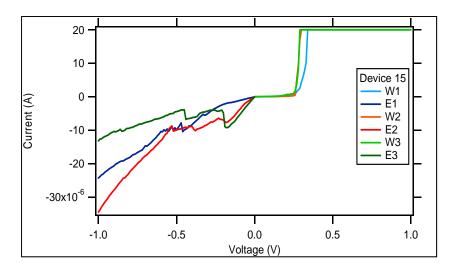

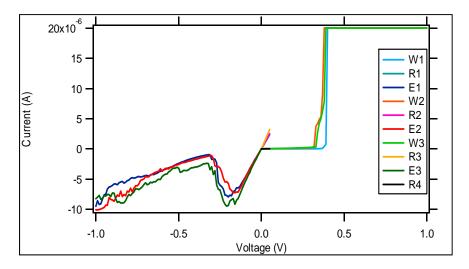

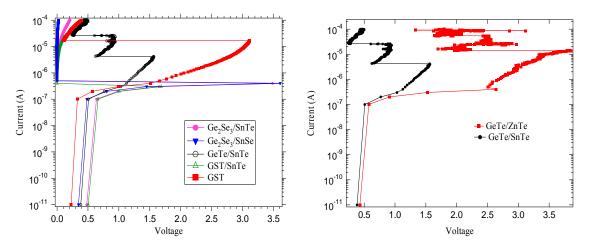

| Figure 98. IV curves for phase-change memory stack structures                                                                                                     | 75       |

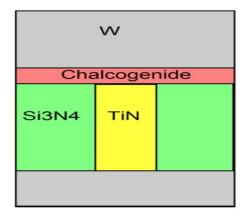

| Figure 99. Planar structure. Bottom electrode contact (TiN) is 40 nm in diameter                                                                                  | 76       |

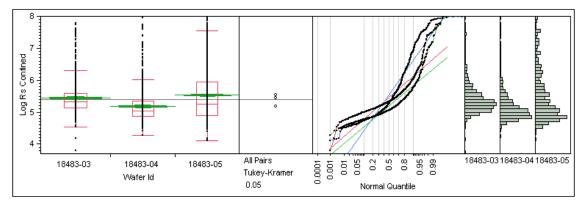

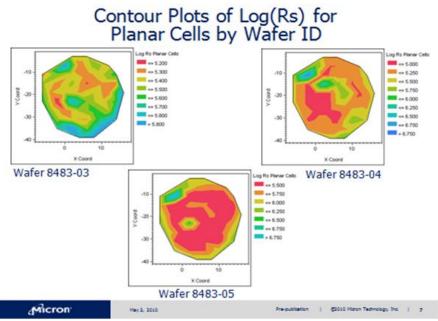

| Figure 100. Inline probe data for planar cell structure devices with 40 nm diameter                                                                               | 76       |

| Figure 101. Wafer maps showing resistance for each wafer of planar structure devices                                                                              | 77       |

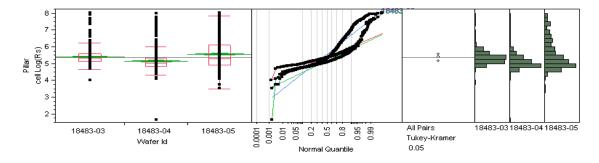

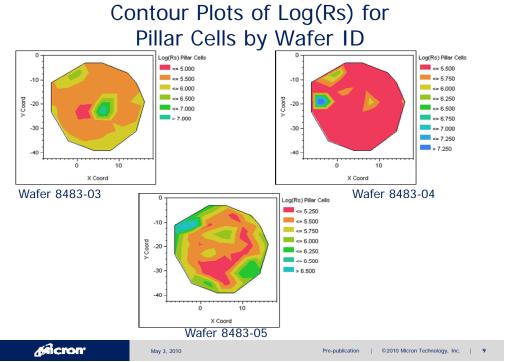

| Figure 102. Micron inline testing data for the pillar cell structure devices                                                                                      | 77       |

| Figure 103. Wafer maps showing resistance for each wafer of pillar structure devices                                                                              | 78       |

# LIST OF TABLES

| Table                                                                                                | Page |

|------------------------------------------------------------------------------------------------------|------|

| Table 1. Ion-Conducting Experiments                                                                  | 23   |

| Table 2. Samples investigated for ZFS                                                                | 24   |

| Table 3. Devices fabricated and tested with co-sputtered metal-Ge <sub>2</sub> Se <sub>3</sub> films | 37   |

| Table 4. Programmed device resistance for IC stack device frequency tests                            | 55   |

| Table 5. Summary of wafers and die (ASU Chips) processed                                             | 70   |

| Table 6. Statistical analysis for the 300 mm wafer planar structure data                             | 77   |

| Table 7. Statistical analysis for the 300 mm wafer pillar cell structure data                        | 78   |

## **ACKNOWLEDGMENTS**

This material is based on research sponsored by air force research laboratory under agreement number FA9453-08-2-0252. The U.S. government is authorized to reproduce and distribute reprints for governmental purposes notwithstanding any copyright notation thereon.

# **DISCLAIMER**

The views and conclusions contained herein are those of the authors and should not be interpreted as necessarily representing the official policies or endorsements, either expressed or implied, of Air Force Research Laboratory or the U.S. government.

(This page intentionally left blank)

#### 1 SUMMARY

The purpose of this research was to investigate non-volatile memory device technologies that could be applied to reconfigurable electronics applications and provide power reduction, radiation tolerance, smaller size, and improved reliability over the existing non-volatile memory devices. The research described in this report encompasses: 1) the materials and device design, and 2) the fabrication and testing of the devices. The initial efforts on this work were partially collaborative with another reconfigurable electronics grant through the Air Force Office of Scientific Research (AFOSR) under grant number FA9550-07-1-0546. The types of memory devices that were investigated are divided into three categories:

1) Ion-Conducting, Resistance Variable Memory Devices (also referred to as memristors). These are devices that change resistance via the movement of metal ions (Cu and Ag ions) through an active device layer, upon proper application of an electric signal. Devices were designed that showed high speed, low voltage/current operation, variable resistance programmability (through spike-timing-dependent-plasticity tests over timing windows of ns to ms), cycling greater than 1 million cycles, and operating temperatures of at least 150 °C without degradation. Many of these materials were tested in two-terminal devices, integrated with CMOS circuits, and in small cross-point arrays during this work.

**Recommendation:** Based on the factors of device electrical response and ease of fabrication, the ion-conducting resistance variable memory device has the highest potential for successful application to the area of reconfigurable electronics and non-volatile memory. Based on the materials researched during this work, this type of device also has the most flexibility in altering the device electrical characteristics to fit specific applications. Devices can exhibit bidirectional resistance tuning using low voltage, small pulse width signals. The technology can be integrated into a CMOS back-end-of-line process with no consequence to an existing CMOS fabrication facility.

2) Atomic or Molecular Memory Based on Zero-Field Splitting (ZFS). This category comprises devices that define the memory state by the interaction energy of the spin-spin and spin-orbit angular moment of the electrons around an atom and the angular momentum (spin-spin and spin-orbit) of the nucleus. The theoretical operation of this type of device is based on the energy splitting produced by this interaction (in the absence of an externally applied magnetic field), referred to as zero-field splitting. Materials were investigated in order to try find a suitable material that exhibited this property at room temperature with enough electron spin density in one of the energy states for a detectable microwave signal absorption upon transition of an electron between energy states. Materials were investigated in the bulk form, with some showing promise for this application, as observed via electron paramagnetic resonance spectroscopy. However, deposited thin films of these materials did not show high enough signal absorption to indicate that they would be viable for detection at the nanoscale in a memory device. Preliminary device fabrication with these materials also failed to yield a functional ZFS device. This could be due to the electron density being too small in a given state in a device to achieve a high enough signal to noise ratio to detect.

**Recommendation:** The ZFS device concept is still high risk and theoretical. It seems that one of the best approaches for exploring the viability of this theory for further study would be to investigate organic molecules as potential candidates since organic molecules frequently

exhibit large spin polarization at room temperature. This increase in signal intensity due to the spin polarization could give rise to a detectable signal within the small size of a bit.

3) Phase-Change Memory. The work in this category included devices consisting of stacked chalcogenide (S-, Se- or Te-containing material) thin films and phase-change alloys that are potentially capable of producing multiple memory states.

Devices fabricated at Boise State University were large compared to the current technology node (1 um diameter vs < 20 nm). This has significant consequences for device operation due to device volume dependence (for melting and quenching the volume of material to change phase). In addition to the larger two-terminal devices fabricated at Boise State, devices were tested that had been fabricated (in collaboration with another project funded by NASA through the Idaho Space Grant Consortium) on integrated circuit die which had been fabricated through the MOSIS consortium, with feature sizes at 0.5 um. Boise State also had the opportunity to collaborate with Micron Technology to test the phase-change stack materials on smaller feature sized devices (40 nm) using Micron's 300 mm wafer test process flow.

**Recommendation:** It is difficult to change the resistance of a phase-change device consistently and between multiple values. The operation of this type of device depends significantly on the device structure and on the materials and fabrication processes. The energy required to change the resistance of a device is significantly higher than the ion-conducting memory device due to the need to heat the volume of material past the melting temperature. The device structures and fabrication processes needed in order to have lower energy switching and consistent device operation are much more complex, which translates into being more prone to processing errors. However, devices constructed which operate with both the phase-change and an ion-conducting mechanisms within the same device material are viable.

#### 2 INTRODUCTION

The work done in each of the three areas will be described in this report. In this section, background information for each type of memory studied will be presented. The audience for this report is expected to have basic understanding of the non-volatile memory types, electrical characterization techniques, basic properties of materials knowledge, and basic knowledge of semiconductor device fabrication processing.

# 2.1 Ion-Conducting, Resistance Variable Memory Devices (Memristors)

Background: Variable resistance devices, or memristors [1], have been studied for their potential use in applications such as non-volatile memory [2], neuromorphic and bio-inspired computing [3-9], and threshold logic applications [10]. In general, ion-conducting devices are a type of memristive device that changes resistance through a mechanism involving the generation of mobile metal ions upon application of a potential across the device [11]. The mobile metal ion is generated from an easily oxidized metal, such as an Ag or Cu layer, when a positive potential greater than the oxidation potential of the metal is placed on the electrode nearest the metal layer. A mobile metal cation generated in this process moves via the applied electric field towards the more negative electrode. In the case of a chalcogenide-based device, the mobile metal ions migrate into and through an amorphous material, such as As<sub>x</sub>S<sub>y</sub> [12], AgInSbTe [13], Ge<sub>x</sub>Se<sub>y</sub>, or Ge<sub>x</sub>S<sub>y</sub> [14,15], to eventually form a conductive pathway between the two electrodes in contact with the amorphous material [2,11,12-18], thus lowering the device resistance. Reversing voltage polarities between the electrodes causes the conductive pathway to disperse via generation of metal ions that migrate back towards the metal layer, thus increasing the resistance.

Problems/Challenges: Chalcogenide-based ion-conducting devices comprised of (Ge<sub>x</sub>Se<sub>1-x</sub>)<sub>v</sub>Ag<sub>1-</sub>  $_{v}$  or  $(Ge_{x}S_{1-x})_{v}Ag_{1-v}$  are typically fabricated by either depositing a ternary material (e.g. Ge-S-Ag) to a desired stoichiometry [17], or by photodoping and/or thermally annealing the Ag or Cu metal into the active amorphous material matrix [14,18]. These fabrication methods offer deposition challenges since precise control of the amount of metal included in the chalcogenide and the stoichiometry of the chalcogenide material are both difficult to achieve and are critical to the consistent operation of the device [19,20]. In addition, these fabrication methods limit the maximum temperature allowed in subsequent processing steps due to the reduced glass transition temperatures of Ag or Cu doped chalcogenide glasses, thus limiting even simple processes such as a photolithography photoresist bake step (which is often above 100 °C). For example, many of the Ge<sub>x</sub>Se<sub>y</sub>, or Ge<sub>x</sub>S<sub>y</sub> glasses that can be photodoped with Ag or Cu have glass transition temperatures that are less than 200 °C [21] prior to doping. These glass transition temperatures drop precipitously when Ag or Cu is added to the material, thus rendering these materials even more sensitive to processing temperatures [19-21]. Therefore, the back-end-of-line (BEOL) processing temperatures as well as device operating temperatures must remain quite low for these processing methods, sometimes lower than 80 °C, to ensure that crystallization is avoided since the devices do not function consistently when the glass crystallizes. Furthermore, devices incorporating Ag or Cu directly into the chalcogenide film are prone to over saturation with the metal during repeated cycling or as the device is heated (either through Joule or ambient heating), thus eventually limiting and degrading device operation. Lastly, devices which incorporate Ag or Cu directly into the chalcogenide layer are prone to significant electrical

inconsistencies from device-to-device and within the same device. This lack of consistency makes their use in reconfigurable electronics difficult to implement.

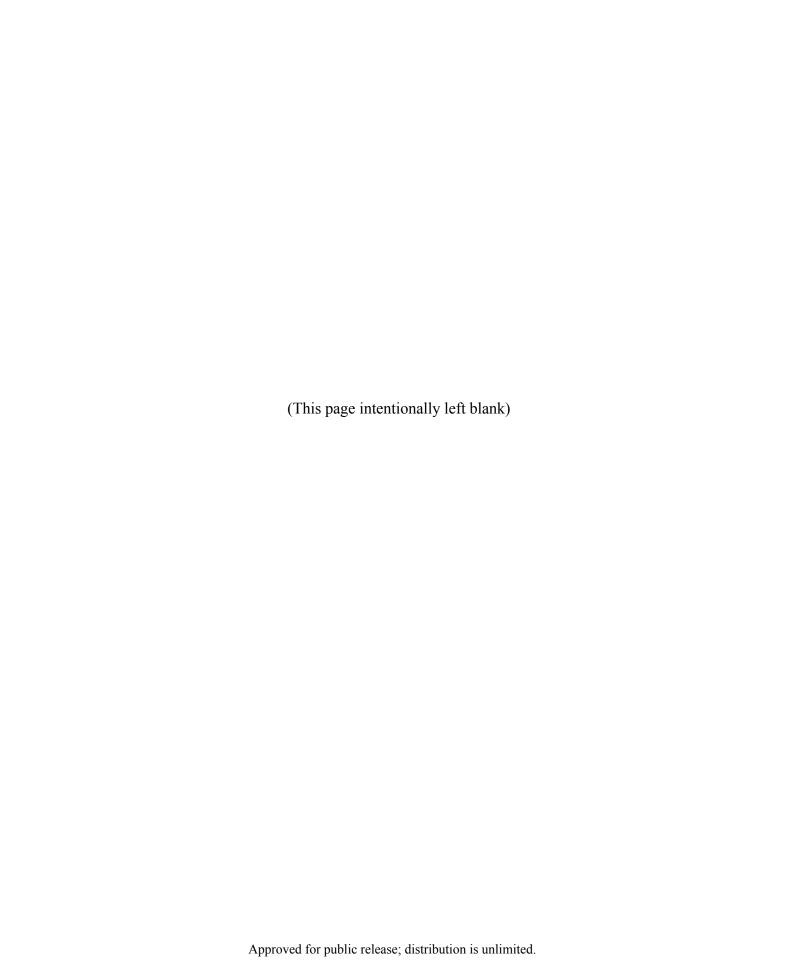

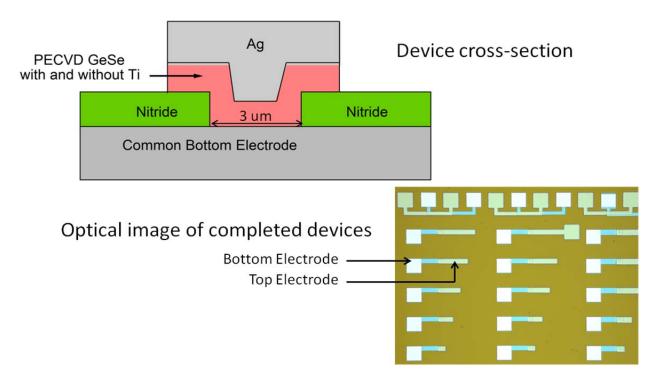

Methods of addressing the challenges: Devices with the structure shown in Figure 1, consisting of a Ge<sub>2</sub>Se<sub>3</sub> layer adjacent to an M-Se layer material (M-Se = SnSe, Sb<sub>2</sub>Se<sub>3</sub>, Ag<sub>2</sub>Se, PbSe, or In<sub>2</sub>Se<sub>3</sub>) have previously been fabricated and characterized for high temperature operation (150 °C), cycling endurance, and switching consistency (under grant AFOSR FA9550-07-1-0546). The Ge<sub>2</sub>Se<sub>3</sub> layer is the 'active' switching layer with a high glass transition temperature (~ 350 °C), and contains homopolar Ge-Ge bonds. Homopolar bonds were a requirement for material selection in this work since they have previously been empirically shown to produce the most consistent ion-conducting resistance switching in an M-Se device structure [28]. These devices have no Ag-doping requirement; the separate Ag layer provides the source of ions during operation without the need to photodope or thermally drive Ag into the Ge<sub>2</sub>Se<sub>3</sub> layer. Since there is no addition of Ag to the Ge<sub>2</sub>Se<sub>3</sub> active layer during fabrication, the glass transition temperature remains high throughout processing, thus allowing higher back-end-of-line processing temperatures.

Figure 1. (left) Cross-section illustration of an example device structure. (right) Optical top-down image of a fabricated device. The device is located in the center

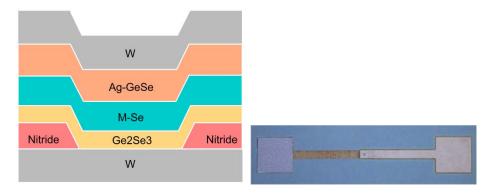

The M-Se materials were selected in order to investigate the influence of metal ion oxidation state, size, redox potential, and preferred bonding environment [30] on the device electrical characteristics, with the expectation that the metal from the M-Se layer could migrate into the  $Ge_2Se_3$  layer and perturb a Ge-Ge bonding site, thus altering the device switching properties. Devices with an M-Se layer of either  $Ag_2Se$  or SnSe have previously been shown to exhibit memristive behavior [25-28]. It was also previously shown that a  $Ge_2Se_3/SnSe$  device with no Ag layer operates with a phase-change mechanism and that Sn migrates into the  $Ge_2Se_3$  layer during operation [29]. In addition, the previous AFOSR study determined that the device structure with an SnSe layer produced an easy to fabricate device with low switching voltages and high temperature (> 140 °C) continuous operation with good cycling endurance (> 1 million cycles), Figure 2. Based on these results, the IC stack in Figure 1 with M-Se = SnSe was selected as the baseline for comparison in device materials studies in this work.

Figure 2. IC stack device cycling response at T = 140 °C.

In order to explore reconfigurability of a device as determined by the ability to tune a device's resistance, the materials and layers were investigated and their influence on device electrical characteristics measured. With every change in material there is likely a corresponding change in the operational parameters, such as cycling lifetime, resistance range, ability to achieve variable resistance, temperature tolerance, energy requirements, etc. A good understanding of the physics of device operation is needed to address how a chemical modification in an ion-conducting device will affect the operation. Theoretical calculations on metal movement into Ge<sub>2</sub>Se<sub>3</sub> (both Ag and Sn ions)

were initiated in this work. However, due to the time-consuming nature of theoretical calculations, devices were fabricated and tested simultaneously with the ongoing theoretical calculation effort. Without a good understanding of the physics of how the device operates, functionality of devices was addressed through chemical modification of material layers during device fabrication.

Since electrical conduction in amorphous materials is quite different than in crystalline semiconductors, temperature dependence measurements were performed on certain device types in order to help elucidate the conduction mechanisms of the devices. The temperatures studied included the range from 5 K to 350 K, thus covering the full range of possible conduction mechanisms from extended states conduction ( $\sim 270-350$  K), through variable range and nearest neighbor hopping and tunneling (lower temperature ranges) [30].

In addition, pulsed testing (i.e., application of electrical pulses with shape, variable amplitude and width) was performed on devices with Ag or Cu mobile metal ions in order to investigate differences in speed introduced by the different metal ion and the complexity of the ion movement through the active glass layer. The mobility of the metal ion could also influence the programmable resistance range, and provide information on the influence of the metal ion (size, charge, polarizability) on movement in the device and data retention.

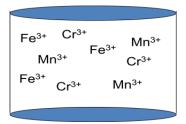

## 2.2 Atomic or Molecular Memory Based on ZFS

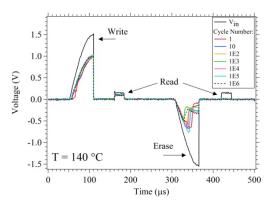

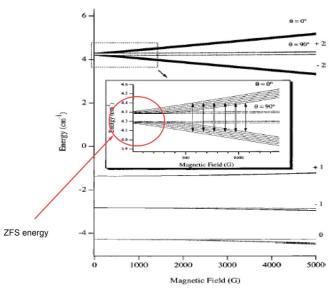

Background: When a paramagnetic transition metal atom or paramagnetic molecule is contained in a matrix material (e.g. glass, protein, liquid) and placed in a magnetic field, the electron spin energy levels split apart as the magnetic field is increased (referred to as Zeeman splitting) as shown in Figure 3 [31-34] for the specific case of the paramagnetic  $Mn^{3+}$  ion in the biological enzyme Mn Superoxide Dismutase [34]. The amount of energy splitting can be determined by application of an electrical signal with a frequency that corresponds to the energy separation (splitting) between spin levels; if the signal is absorbed, the frequency of the absorbed signal corresponds to the energy difference between spin states since the absorption is due to the excitation of electrons from one spin level to the other (with consideration to the transition probability). In some transition metals, particularly those with a total electron spin which is an integer value (such as  $Mn^{3+}$  which has a total electron spin, S=2) splitting between the electron

spin energy levels can occur in the absence of an applied magnetic field. This is referred to as zero-field splitting (ZFS), an example of which is shown in the inset of Figure 3, circled. This ZFS splitting means that no externally applied magnetic field is required to split energy levels, thus allowing for an electron transition between spin states even in the absence of a magnetic field.

The ZFS absorption energy can be predicted from the electron spin Hamiltonian [31]:

$$H = \beta e \vec{B}_O \cdot \tilde{g}_e \cdot \hat{S} + D \left[ \hat{S}_z^2 - \frac{1}{3} S(S+1) \right] + E \left( \hat{S}_x^2 - \hat{S}_y^2 \right) + \hat{S} \cdot \tilde{A} \cdot \hat{I}$$

(1)

This Hamiltonian was applied to the  $\mathrm{Mn}^{3+}$  metal ions in Mn Superoxide Dismutase to calculate the electron spin energy levels, Figure 3. The calculated energy levels show that there is an energy separation between the  $\mathrm{Ms} = +/-2$  spin levels when the applied magnetic field is zero. This is the ZFS energy. The absorption of an applied electrical signal with a frequency corresponding to this energy would indicate that the material was in this particular spin configuration. Modification of the energy levels

particular spin configuration.

Modification of the energy levels

(for example, through modification of the Mn oxidation state or the ligand environment around the metal ion) would change the absorption frequency, thus indicating a different 'ZFS state'.

Figure 4. Microwave absorption at zero magnetic field from a sample of Na<sub>2</sub>O-CaO-MgO-SiO<sub>2</sub> glass doped with 0.1 wt. %MnO<sub>2</sub>. Data collected at 77K [35]

Magnetic field

Figure 3. Electron spin energy level diagram of Mn<sup>3+</sup> in the protein Manganese Superoxide Dismutase (from [34])

If a device could be fabricated with a material that exhibited a reversible ZFS state, it could potentially be used as a non-volatile memory. It should be stressed that the ZFS concept is not similar to magnetic random access memory (MRAM) as there is no applied magnetic field needed, and there is no transfer of spins between material layers.

Another example of signal absorption (resonance) at zero magnetic field is given by Rakhimov who observed a microwave resonance at zero-magnetic field in SiO<sub>2</sub> glass containing Mn<sup>2+</sup> ions [35] at a temperature of 77 K, Figure 4. These data show that zero-field absorption from transition metals (in this

case Mn<sup>2+</sup>) can be observed in very simple glass matrices which are promising for ZFS memory.

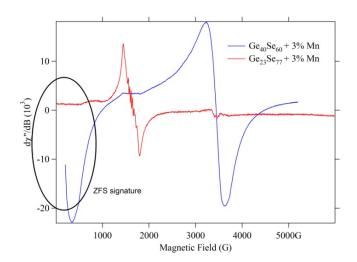

In addition, initial work under AFOSR grant FA9550-07-1-0546 explored the  $(Ge_{40}Se_{60})_{97}Mn_3$  and  $(Ge_{23}Se_{77})_{97}Mn_3$  materials as potential candidates for ZFS memory since one shows a zero-field absorption and the other does not, Figure 5.

Figure 5. Electron paramagnetic resonance of bulk GeSe-Mn glasses at 4.2 K. A zero-field splitting signature was observed in the  $(Ge_{40}Se_{60})_{97}Mn_3$  sample, circled

These systems needed to be explored at higher temperatures to obtain the energy level diagrams and elucidate the differences in the Mn ion environment in the two glass matrices. It was anticipated that understanding the underlying mechanism for the zero-field absorption in the (Ge<sub>40</sub>Se<sub>60</sub>)<sub>97</sub>Mn<sub>3</sub> glass would allow design of new materials with potential room temperature zero-field splitting absorption.

Of interest in this work is a material that exhibits ZFS at room temperature. There are some recent examples of molecules that have this property. For example, researchers at Oxford University have developed a modified fullerene molecule which exhibits zero-field splitting at room temperature [36].

<u>Problems/Challenges:</u> There are three major challenges to this type of memory. The first is the issue of spin concentration in a small device size. The second is finding a material that exhibits higher temperature (near room temperature or slightly below) electron spin transfer with a high enough signal to noise ratio to detect signal absorption. The challenge of spin concentration ties in directly with the challenge of finding a material that can flip enough electron spins at non-cryogenic temperatures. Since the electrons distribute among all of the energy levels according to a Boltzmann distribution, the higher the temperature, the lower the concentration of electrons in any one given spin state. This has the effect of lowering the detectable signal absorption due to a lower number of electrons in the spin state that exhibits ZFS. The spin concentration needs to be high enough in the appropriate energy levels that the signal to noise ratio of the loss of the input signal due to absorption within the material is large enough to detect whether the exciting signal was absorbed.

The third challenge is finding a method of reversibly perturbing the spin states so that the memory device can change states.

Methods of addressing the challenges: The first two challenges can be addressed by initially performing room temperature EPR measurements on various candidate (integer spin) materials in the bulk state and identifying those with likely ZFS states. Second, cold temperature EPR measurements can be used to map out the electron spin energy levels if an EPR spectrum can be observed and monitored as a function of temperature. Once these two issues are addressed, the

subset of materials selected for further investigation (from the EPR measurements) is filtered for viable candidates for thin film deposition. From the resultant thin film investigation, likely material candidates and methods of perturbing their spin states can be investigated. These include electric field induced changes, reversible chemical changes, or optically induced spin state changes. Thin films as well as devices of some candidate materials were then tested at room temperature as a function of frequency and magnetic field to investigate potential absorption frequencies.

# 2.3 Phase-Change Multi-State Memory

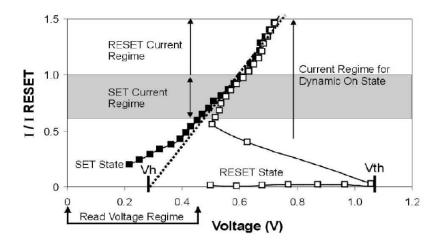

<u>Background:</u> Phase-change memory includes chalcogenide materials that undergo a phase-change from a crystalline to an amorphous state upon application of a current through the material, Figure 6, thus creating a device that changes resistance between low and high values [37]. The memory state is held in the resistance value of the device.

Figure 6. Current-voltage curve for a typical phase-change memory material

In the past several years, an increasingly large research effort within many memory manufacturing companies has gone into the development of a commercially viable phase-change electronic memory. BAE Systems was the first to offer a phase change memory array for sale in the mid 2000's. Later, engineering samples of phase-change memory arrays from Samsung were offered to the public in February 2007. Micron Technology offered a phase-change memory chip to the public for a short time in (beginning in 2012/2013). However, an ideal phase-change material for reconfigurable electronics, that can reliably switch between more than two resistance states to give a multi-state memory, has not been developed.

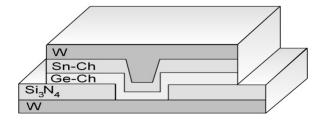

Previous work showed phase-change memory operation in devices fabricated with layers of chalcogenide materials rather than a single layer of an alloy (such as GST) [29]. The chalcogenide layers tested consisted of a Ge-chalcogenide glass layer and a metal-chalcogenide layer, Figure 7, and showed promise in terms of good cycling endurance.

Figure 7. Cross sectional drawing of a stacked layer phase-change memory device. Ch denotes either S, Se, or Te

This previous work showed that phase-change operation was facilitated by the migration of the metal from the metal-chalcogenide layer into the glass layer when a voltage of an appropriate polarity with respect to the metal-chalcogenide layer was applied across the device [29]. Devices with this structure offer advantages over the traditionally studied single layer systems, such as:

- Lower current required for switching, and thus lower power required for operation

- Improved adhesion of the chalcogenide material to the electrodes, thus improving endurance

- Simpler material deposition processes since the phase-change material can be easily sputtered, depending upon the material selection

- The ability to have multiple resistance values depending upon the materials used

The thermal properties of some of the alloys formed when a metal migrates into a Gechalcogenide glass layer during operation of a layered film phase-change memory device were studied under a previous Air Force contract, FA9550-07-1-0546. Raman Spectroscopy and differential scanning calorimetry (DSC) were used to observe the bonding structure and glass transition and crystallization temperatures of the alloys. Alloys with multiple crystallization transitions in the DSC data were identified as potential candidates for device fabrication.

<u>Problems/Challenges:</u> Some of the issues associated with fabrication of devices comprising the metal-doped chalcogenide materials include thin film deposition process development. It is not possible in many cases to evaporate a bulk material that exhibits the multiple crystalline transitions into a thin film and maintain the desired material stoichiometry. The physical properties of the resultant thin film can be much different than the bulk starting material. Characterization of the resultant thin film structural and physical properties is also a challenge.

Another challenge involves the electrical characterization of devices fabricated with the new materials. Without the ability to make the device volume very small (such as is the case with a fabrication facility equipped with state-of-the-art photolithography processes capable of < 20 nm feature sizes) it is possible that the fabricated device may require more potential, for longer time periods, to cycle between crystalline and amorphous states than may actually be necessary when used within a memory array with small feature size. This is due to the volume dependent heating necessary to change physical states of the material.

It is also challenging to determine the stability of the device in a given state (data retention) [38] since thermally heating a phase change material, like is done for traditional NVM lifetime

acceleration studies, can cause material migration (from another layer, for example [39, 40]) or structural relaxation of the material.

Methods of addressing the challenges: Materials deposition challenges can be addressed through exploration of materials deposition techniques other than evaporation. Techniques investigated in this work include PECVD deposition of Ge<sub>2</sub>Se<sub>3</sub> and transition metals, such as Ti, through collaboration with Prof. Rene Rodriguez at Idaho State University, and cosputtering metals and Ge<sub>2</sub>Se<sub>3</sub> at Boise State University. Devices were fabricated using both of these film deposition techniques. The thin film characterization techniques of Raman spectroscopy and UV-Vis spectroscopy were used to investigate the thin film structure of the materials.

Additionally, the migration of metal between layers of the layered phase change memory stack was investigated through time-resolved X-ray diffraction studies [39, 40] through collaboration with Prof. Santosh Kurinec at Rochester Institute of Technology.

Electrical characterization was addressed through DC and pulsed switching on the large devices fabricated at Boise State, as well as through fabrication of devices on platforms with smaller vias, either through collaboration with Micron Technology or through die fabricated through the MOSIS consortium.

The issue of data retention and stability was not addressed in this work.

#### 3 METHODS, ASSUMPTIONS, AND PROCEDURES

# 3.1 General Experimental Methods

#### 3.1.1 Fabrication

For each device technology, device fabrication followed similar process flows. The devices are

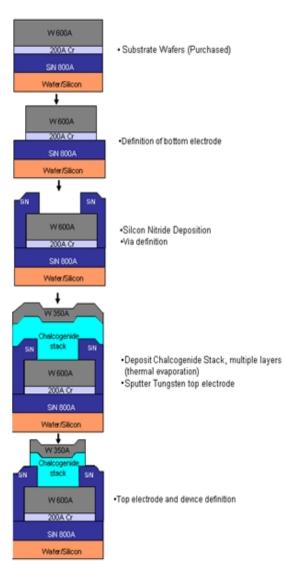

Figure 8. Common bottom electrode process flow

fabricated with either (1) a common bottom electrode (a blanket electrode over the entire wafer/die) or (2) an isolated bottom electrode (all devices are isolated from each other and the substrate). The main process steps in device fabrication for a common bottom electrode process are shown in Figure 8. The isolated bottom electrode process flow is shown in Figure 9. The common bottom electrode process flow is fast and allows for quick turnaround materials tests. These process flows are similar despite the type of mask used, since for any situation, the devices will have either a common or an isolated bottom electrode.

The devices were typically fabricated on 100 or 200 mm p-type Si wafer substrates. These wafers were purchased with the metal bottom electrode layer (W over Cr, Figures 8 and 9). For the case of

the common bottom electrode devices, the wafers were purchased with a layer of nitride above the metal layer.

The device active area diameter (referred to as the 'via') ranged from  $0.13~\mu m$  to  $60~\mu m$ , depending upon the layout and where the via photolithograph was performed. The minimum via size for the Boise State University clean room (the Idaho Microfabrication Laboratory) was  $1~\mu m$ .

The wafers were sputtered with Ar<sup>+</sup> to clean the W bottom electrode followed by in-situ sputter deposition of a Ge<sub>2</sub>Se<sub>3</sub> layer, using an AJA International ATC Orion 5 UHV Magnetron sputtering system and a Ge<sub>2</sub>Se<sub>3</sub> target from Process Materials. If present, M-Se layers were deposited by either thermal evaporation using a CHA Industries SE-600-RAP thermal evaporator equipped with three 200/100 mm wafer planetary rotation or sputtering with the AJA sputtering system. The rate of material deposition during evaporation was monitored using an Infincon IC 6000 with a single crystal sensor head. The base system pressure was  $1x10^{-7}$  Torr prior to evaporation. Bulk materials were deposited via thermal evaporation. A W top electrode was deposited by sputtering W (350 Å) using the AJA International system. Etching was performed with a Veeco ME1001 ion-mill by etching through the W and the memristor device materials and stopping on nitride.

Typically devices used three separate layers above the active layer, 150 Å Ge<sub>2</sub>Se<sub>3</sub>/500 Å Ag/100 Å Ge<sub>2</sub>Se<sub>3</sub>, which intermingle during sputter deposition to create a mixed conductive layer that is the source of metal ions during operation (denoted Ag-GeSe in Figure 1). The purpose of using these three layers is to create a good adhesion layer for the W top electrode to the active layer.

Figure 9. Isolated bottom electrode process flow

#### 3.1.2 Mask Layouts

The main masks created and used in this work for all device types are the in-via layout (which can be used for isolated and common bottom electrode tests), the  $10 \times 10$  array, the  $150 \times 150$  array, and the ZFS layout (high frequency device structures). Each mask is described in this section.

## 3.1.2.1 *In-via layout.*

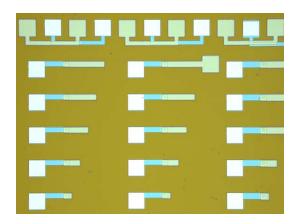

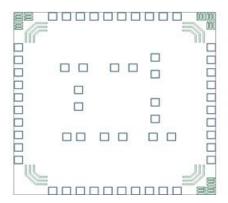

The in-via layout includes die with 20 rows of devices, and 9 columns of devices ranging is size from 1 um to 30 um in diameter (Figure 10, isolated bottom electrode case). Variations on this layout were made in which the top and bottom electrodes both have bond pads (Figure 1, right side) instead of the varying length top electrode contacts (shown in Figure 10).

# 3.1.2.2 10 x 10 and 150 x 150 array layouts.

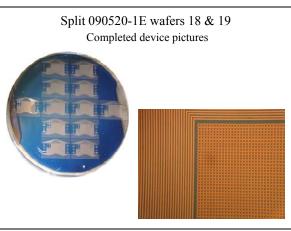

The 10 x 10 and 150 x 150 array layouts are isolated bottom electrode layouts with die each containing one, Figure 11.

Figure 10. Isolated bottom electrode invia layout. Top electrode is on the right (varying length lines) and bottom electrode is the square on the left

Figure 11. Optical image of a completed  $10 \times 10$  array and portion of  $150 \times 150$  array. The wafer image of the  $150 \times 150$  array is in the center and contains 12 die

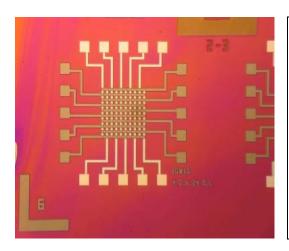

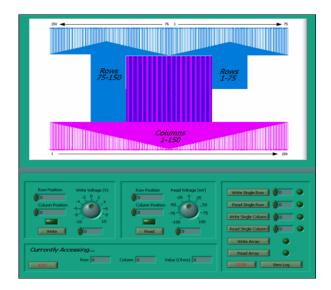

Figure 12. Front panel of the  $150 \times 150$  testing program showing the layout of electrical contacts to the array

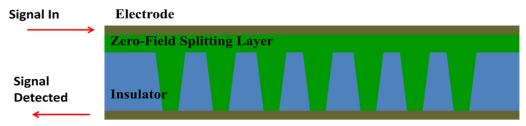

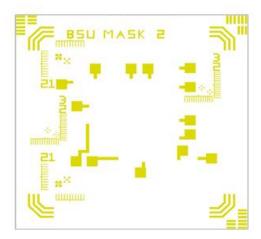

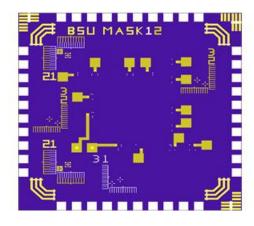

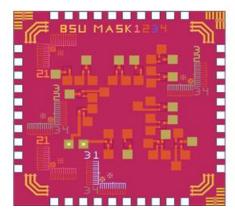

#### 3.1.2.3 ZFS mask layout.

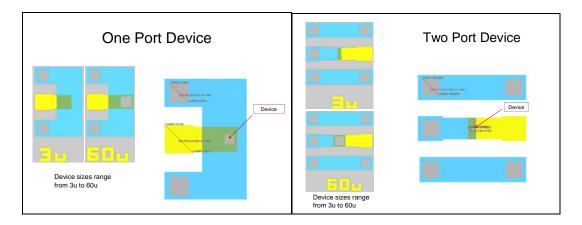

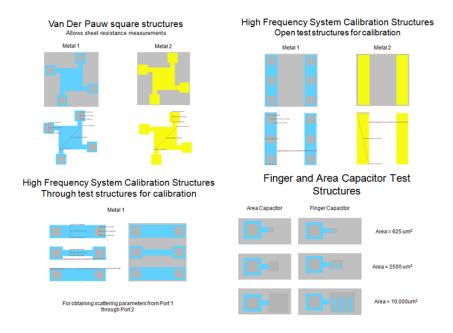

The ZFS mask set was designed to allow high frequency measurements of devices. To do these measurements, three separate high frequency test structures need to be available during testing. Therefore, the ZFS mask consists of three separate die types on one mask. The three die types are: one-port, two-port, and stacked-one-port. Figure 13 shows the one and two port device layout. In addition, each die contains five types of calibration and test structures (see Figure 14) which is also necessary for high frequency measurements. On each die, device sizes range from 3 um to 60 um. The large die was included to provide more volume for signal detection in the ZFS memory experiments.

Figure 13. One and Two Port device layouts

Figure 14. Test structures on ZFS layout. Not shown is the short test structure

# 3.1.3 Material Characterization and Fabrication Process Step Qualification

All fabrication process steps needed to be developed and qualified before device fabrication. Characterization methods/tools used for active layer film monitoring include:

- 1) Raman spectroscopy active device material characterization

- 2) UV-Vis active device material characterization for new materials

- 3) n&k 1280 broadband spectrometer film thickness qualification for process steps

- 4) SEM as needed for film thickness, profiles, overall cross section view

- 5) EPR for thin film ZFS investigations

#### 3.1.3.1 Raman spectroscopy.

Raman spectroscopy is typically used to characterize and then monitor in-line the active device layer films. The Raman spectroscopy investigations were performed with a backscattering configuration using a Renishaw Invia Raman Microscope with a resolution of 1 cm<sup>-1</sup>. The scattered light was dispersed by a spectrometer fitted with a 1200 lines/mm grating. The excitation wavelength was 785 nm produced by a single-mode wavelength stabilized laser diode (Innovative Photonic Solutions). The Raman spectra were measured three times on different points for each sample with a 20x objective lens (Leica, N.A. = 0.40) for all room temperature measurements. The beam spot size was approximately 10 µm at this configuration.

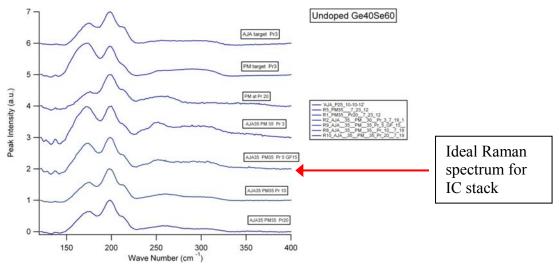

Slight changes in chalcogenide material stoichiometry can be detected easily in the Raman spectrum. Therefore, a Raman sample and spectrum was collected with each lot split. Figure 15 shows Raman spectra for several films of Ge<sub>2</sub>Se<sub>3</sub>, deposited at different deposition tool pressure and power conditions. The changes in the spectra correspond to differences in the Ge-Ge and Ge-Se bonding environment. The spectrum corresponding to the film that is most desirable for the IC stack device is the third from the bottom. If a process qualification run produces a Raman spectrum that is different from this (which is rare once the process conditions for a given sputter

target have been set) then the processing parameters are varied until the film has the desired Raman spectrum (and therefore, associated chemical structure).

Figure 15. Raman spectra of Ge<sub>2</sub>Se<sub>3</sub> films collected under different processing conditions.

#### 3.1.3.2 n&k tool.

The n&k 1280 broadband spectrophotometer tool uses film reflectance to calculate film thickness via a set of proprietary algorithms and a developed recipe for material type. The tool can also be used to collect transmission spectra. Recipes must be developed for each film type (and stack) that is measured. Once the recipe has been developed, the film thickness can be determined to typically 50 Å. This tool is necessary for processing since it is a fast and reliable way to determine film thicknesses in-line.

#### 3.1.3.3 UV-Vis.

New materials are characterized with UV-Vis in addition to Raman to try and learn more about the electronic structure of the material. The n&k tool is used to collect transmission and reflection spectra.

## 3.1.3.4 SEM imaging.

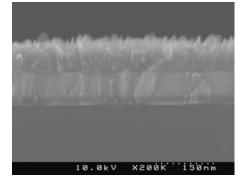

SEM imaging is typically used for initial materials morphology and thickness studies, or when something has gone wrong in the process and the source of the breakdown needs to be determined. Figure 16 shows a SEM image of evaporated SnSe above a W layer. Note in this case, the SEM imaging was used to investigate the structure of the rough SnSe film.

# 3.1.3.5 EPR spectroscopy.

The EPR spectra of chalcogenide glasses were recorded on a Bruker ESP 300E spectrometer operating at X-band

Figure 16. SEM image of evaporated SnSe film above a layer of W

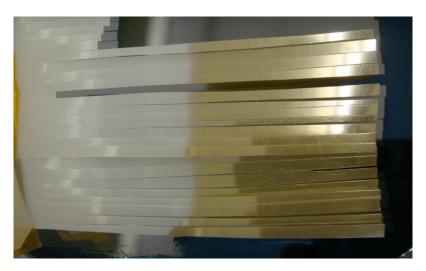

microwave frequency. A dual mode microwave cavity (Bruker, 4116M/0705) was used in order to allow spectra recording with perpendicular (H1  $\perp$  H) or parallel (H1  $\parallel$  H) polarization of the magnetic field vector H1 of the microwave relative to the static magnetic field H. Cryogenic temperatures were obtained with an Oxford ESR900 liquid helium cryostat. The temperature was controlled with an Oxford ITC503 temperature and gas flow controller, typically. Thin films were deposited on mylar strips cut to fit an EPR-grade quartz tube (Wilmad, 707-SQ).

A finger dewar flask (Wilmad, WG-819-B) was used to carry out measurements at 77 K in liquid nitrogen when temperatures did not need to go below 77 K.

Sample illumination was performed using a Dolan-Jenner MI-150R light source with EKE 21 V 150 W halogen lamp of color temperature 3250 K. Light was transmitted from the light source into the dual-mode cavity optical port through Dolan-Jenner B460 fiber with 6.35 mm output diameter, 152.4 cm length, 0.4 to 2.0 microns spectral transmittance and maximum 10 %/ft. at 0.6 microns transmission losses. EPR spectra were recorded on all samples in dark conditions, followed by spectra recording during in-situ illumination. Subsequently, EPR spectra was measured at dark and also, after 15 min of annealing at 300 K.

#### 3.1.4 Electrical

This section describes the experimental requirements for electrical testing of single devices, continuous-wave (CW), pulsed, high frequency, and temperature dependent studies.

#### 3.1.4.1 Single device measurements.

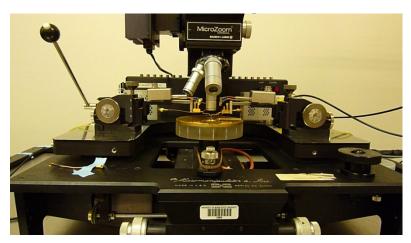

Electrical measurements included DC (quasi-static), continuous-wave, pulsed, or RF/microwave absorption. A MicroManipulator 6200 microprobe station, resting on a Technical Manufacturing Corporation MICRO-g air table for vibration reduction, equipped with a temperature controllable wafer chuck was used for the wafer-level device DC, CW and pulse measurements.

<u>DC:</u> DC measurements were performed with either HP4145B, HP4156A, or an Agilent B1500 semiconductor parameter analyzer.

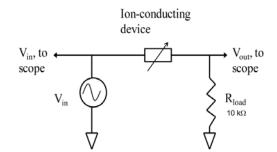

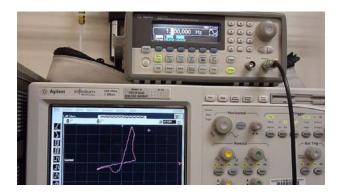

<u>CW</u>: CW measurements were performed on ion-conducting devices using either an HP33250A arbitrary waveform generator and an Agilent 54815A oscilloscope using the circuit shown in Figure 17, or without the external circuit, using only the Agilent B1500 and two integrated waveform generation units for direct measurement of the current through the device upon application of a continuous-wave signal.

Figure 17. Continuous-wave device measurement circuit schematic for the pulse generator and scope measurement technique

For the oscilloscope and circuit version of the CW measurement, a load resistor (typically, 1 k $\Omega$  < Rload < 50 k $\Omega$ ) was used to limit the current through the device during CW measurements

(since programming current can influence the programmed resistance of an ion-conducting device [18, 22, 23]), and to allow measurement of the voltage drop across the device. The IV curves of the device, showing the hysteresis loops, are recorded during measurement, Figure 18.

Figure 18. Test set up for the CW measurement using the test set up in Figure 17, showing an IV curve measured for a memristor device

<u>Pulsed:</u> Pulsed measurements (and the B1500 CW measurements) were performed with an Agilent B1500 Semiconductor Parameter Analyzer equipped with two B1511A medium-power Semiconductor Measurement Units (SMU) for DC measurements and a two channel B1530A

Figure 19. Probe station for pulsed measurements showing the WGFMUs (right and left, rear)

Waveform Generator/Fast

Measurement Unit (WGFMU)

with two B1531A Remote-sense

and Switch Units (RSU) for AC

(alternating current) pulsing

measurements. The probe station

equipped with the

micromanipulators and RSUs are

shown in Figure 19.

The two-channel WGFMU is a self-contained module with each channel able to generate arbitrary linear waveforms with a 10 ns minimum time step. Each channel can also simultaneously measure current or voltage with a

variety of options for measurement range and speed, and the channels share a common ground. The ability to simultaneously apply a test voltage while measuring voltage and current makes it a good tool for rapidly observing changes in device resistance. Each channel of the WGFMU is connected to an RSU located near the probes to improve timing and sourcing. Additionally, each RSU features a switch that allows a direct connection from the SMUs to the device to facilitate high precision DC measurements without the need to lift the probes which could disturb the device state.

<u>Temperature dependence from 298 K to 423 K:</u> Temperature dependence measurements on this probe station were performed using an MC-Systems Hot Chuck Controller with a maximum temperature of 150 °C for the high temperature measurement studies. Devices were equilibrated at the chuck temperature for at least 30 minutes prior to all measurements.

Cold Temperature from 5 K to 350 K: Low temperature measurements were made using a Lake Shore CRX-4K Probe Station, Figure 20. The CRX-4K facilitates temperature control using two Lake Shore Model 340 temperature controllers, a SHI RDK-408D2 Closed Cycle Refrigerator and an RC-EM10-208230-60 CE Liquid Helium Recirculating Chiller for dewerless operation. Lake Shore ZN50R alumina ceramic probe cards with 25 µm tungsten tips were used for measurements. Probe cards were anchored to the sample stage with copper braiding to ensure temperature

Figure 20. Cold temperature probe station

equilibration between stage and probe. Vacuum was maintained and monitored with a Varian V-81 turbo pump. Each temperature was equilibrated at least 20 minutes prior to a measurement at that temperature.

## 3.1.4.2 10 x 10 and 150 x 150 crossbar array measurements

A test system was designed using a probe card and a National Instruments PXI platform to test the DC response of devices in the array structures. The wafer level probe card is designed to make electrical contact with all of the row and column pads on each array. An autoprober can sequentially step through each die. This system, without the autoprober, is shown in Figure 21 and consists of the following:

- 1) Completed Wafer Test Demonstration Platform

- a) A wafer-level probe station is used for wafer level access to custom memristor devices

- b) A wafer level probe card has been designed to interface the test electronics to the devices under test

- c) Custom switching circuitry is used to allow multiplexing the 150 rows by 150 columns of devices to 10 rows by 10 columns

- d) Breakout box conversion is used to convert the cabling from the switching circuitry to the input channels of the switch matrix

- e) A National Instruments switch matrix is implemented to convert to 10 rows by 10 columns of circuit output to a single row and column device access point

- f) An Agilent 4156A semiconductor parameter analyzer is used to measure each device in the cross-point array

- g) An EG1032 autoprober can be used to step through all of the test die on a wafer

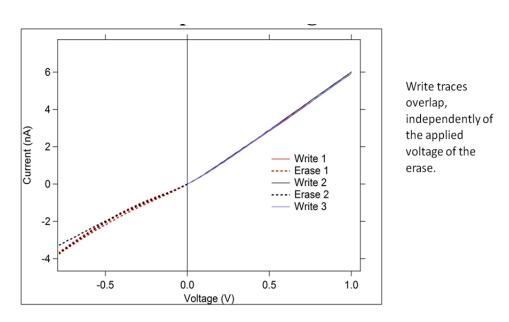

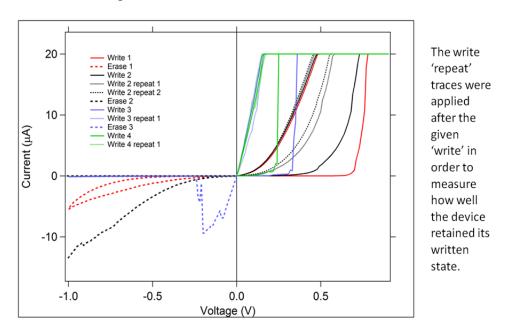

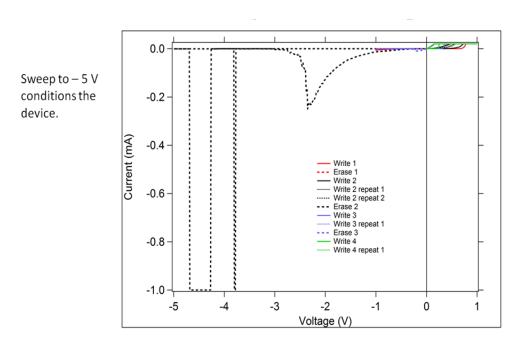

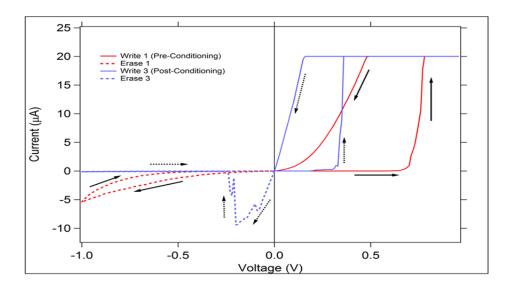

- h) A custom user interface has been designed to control device access and initiate testing