# UNCLASSIFIED

| AD NUMBER                                                    |

|--------------------------------------------------------------|

| AD801769                                                     |

| NEW LIMITATION CHANGE                                        |

| TO<br>Approved for public release, distribution<br>unlimited |

|                                                              |

| FROM<br>Distribution: No foreign.                            |

|                                                              |

| AUTHORITY                                                    |

| SAMSO, USAF ltr., 28 Feb 1972                                |

|                                                              |

|                                                              |

THIS PAGE IS UNCLASSIFIED

AD 801 769

- 2-

### NOTICE

The information and design disclosed herein were originated by and are the property of Lockheed Aircraft Corporation. Lockheed reserves all patent, proprietary, design, manufacturing, reproduction, use, and sales rights thereto, and to any article disclosed herein, except to the extent rights are expressly granted to others. The foregoing does not apply to vendor proprietary parts.

111

į

「日日、小山市、いまいは国産業があるのが常用がない」を通い通い、国際市場にはないないでは、「日本の日本の時間」となっていました。

部領法

Į

Ī

Ĩ

### FOREWORD

This instruction manual on the PAM-FM Ground Station has been prepared as a guide to the operation and maintenance of the Vibration and G-A Ground Station developed under Contract AF 04(647)-347. It is divided into two volumes: Vol. I, Installation, Checkout, and Operation; Vol. II, Theory of Operation and Maintenance.

Volume I is published in two parts. Part 1 describes the installation, checkout, and operation procedures for the trailer-mounted station at Atlantic Missile Range (Patrick Air Force Base). Part 2 describes the installation, checkout, and operation procedures applicable at locations where the ground station is installed on a permanent or semi-permanent basis. Part 2 constitutes a manual of instruction for a complete ground station with record, reproduce, and display capabilities for Vibration and G-A signals. Operators can use the instructions that apply to their installation cupabilities and ignore instructions that do not apply. Thus, if capabilities at a specific installation should change, appropriate instructions for installation, checkout, and operation will be available.

Volume II, published as a single unit, contains a description of the theory of operation for a ground station having record and reproduce capabilities for Vibration and G-A and specific information designed to assist the operator in maintenance of the equipment.

Instruction manuals for operation and maintenance of components supplied by manufacturers other than Lockheed Missiles and Space Division are also furnished to each station.

# CONTENTS

| Section | i e. |            |                                  | Page |

|---------|------|------------|----------------------------------|------|

|         | NOTI | CE         |                                  | 111  |

|         | FORJ | EWORD      |                                  | v    |

|         | LIST | OF ILLUS   | TRATIONS                         | xiii |

| 7.      | THE  | ORY OF OF  | PERATION                         | 7~1  |

|         | 7.1  | Introducti | Q.C.                             | 7-1  |

|         |      | 7.1.1      | Vibration                        | 7-2  |

|         |      | 7.1.2      | G-A                              | 7 -7 |

|         | 7.2  | Vibration  |                                  | 7-11 |

|         |      | 7.2.1      | Receiver                         | 7-11 |

|         |      | 7.2.2      | Base Band Unit, Record Mode      | 7-11 |

|         |      | 7.2.2.1    | DC Amplifier                     | 7-15 |

|         |      | 7.2.2.2    | Noise Filter                     | 7-17 |

|         |      | 7.2.2.3    | Noise Filter Amplifier           | 7-18 |

|         |      | 7.2.2.4    | Reference Voltage Optional Clamp | 7-20 |

|         |      | 7.2.2.5    | Gate Driver Amplifier            | 7-21 |

|         |      | 7.2.2.3    | Reference Amplifier              | 7-22 |

|         |      | 7.2.3      | Demuitiplexer, Record Mode       | 7-23 |

|         |      | 7.2.3.1    | Data Sync Separator              | 7-26 |

|         |      | 7.2.3.2    | Frame Sync Separator             | 7-28 |

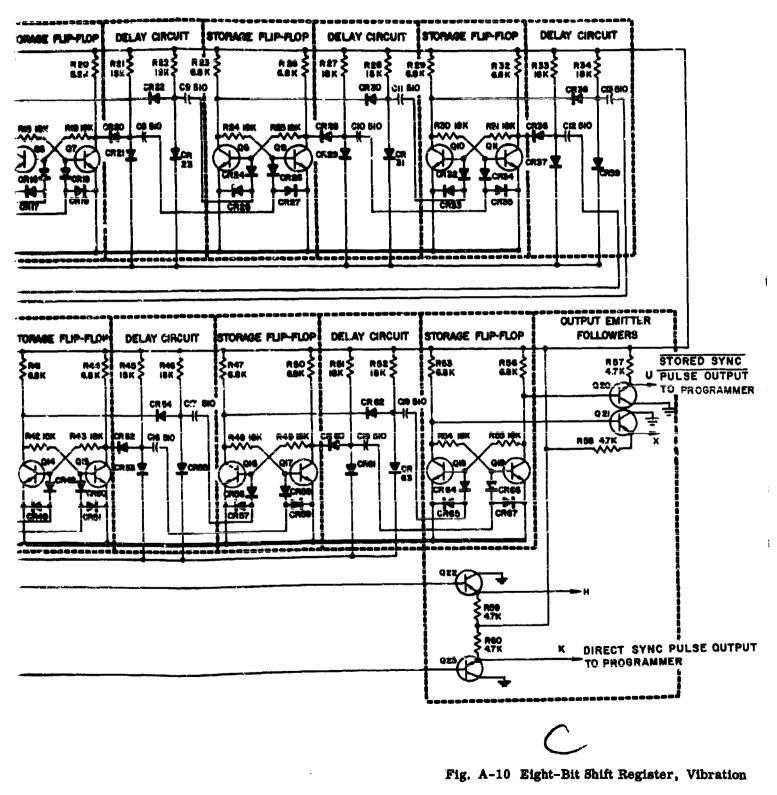

|         |      | 7.2.3.3    | Eight-Bit Shift Register         | 7-30 |

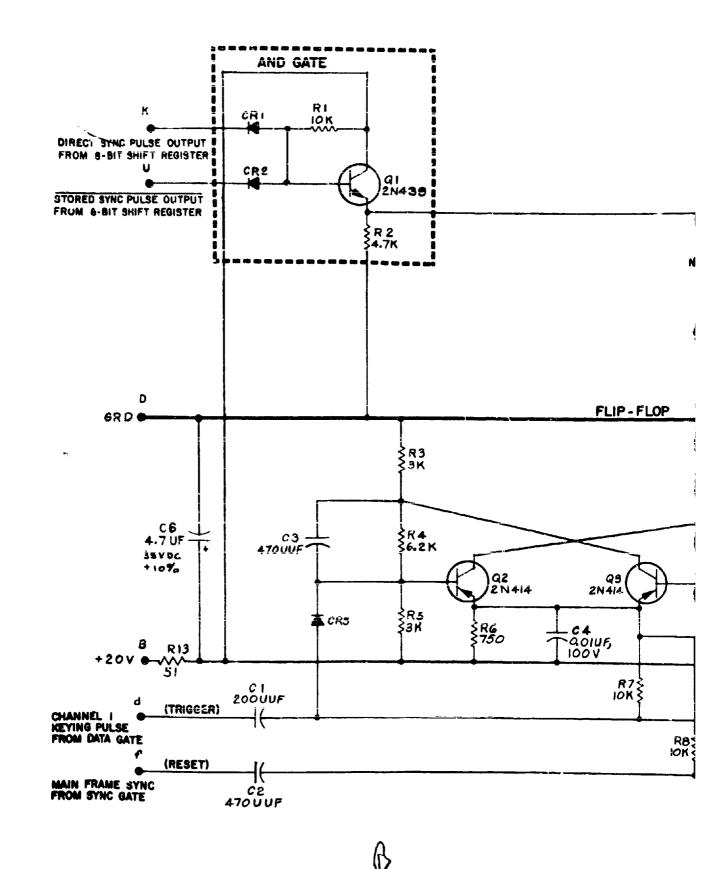

|         |      | 7.2.3.4    | Programmer                       | 7-31 |

|         |      | 7.2.3.5    | Sync Selector                    | 7-31 |

|         |      | 7.2.3.6    | Sync Gate                        | 7-33 |

|         |      | 7.2.3.7    | Zero Data Selector               | 7-34 |

Ī

ł

Ĩ

II L

4

MISSILES and SPACE DIVISION

vii

The second s

1

T.

L

1

E

ſ

Ē

|     |          |                                                | Page   |

|-----|----------|------------------------------------------------|--------|

|     | 7.2.3.8  | Frequency Divider                              | 7-35   |

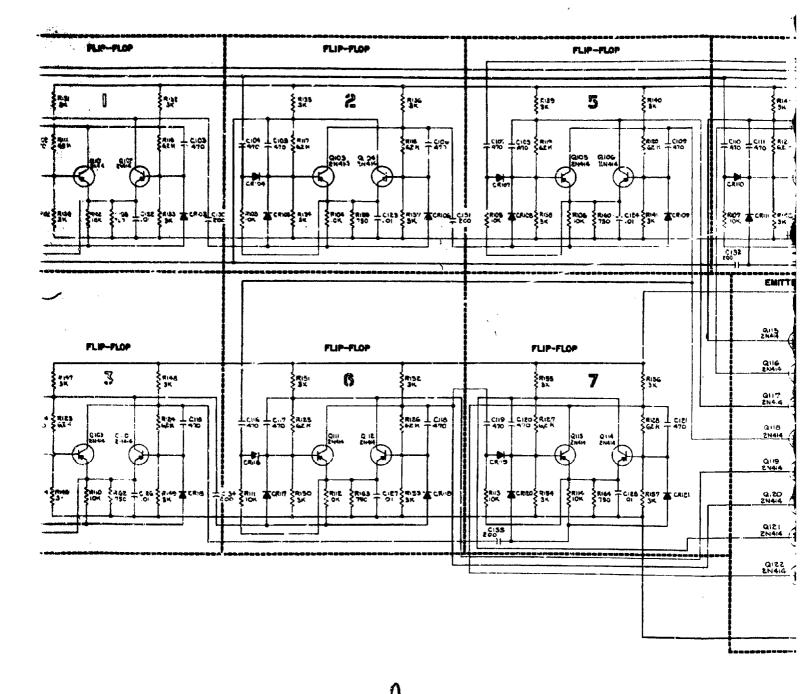

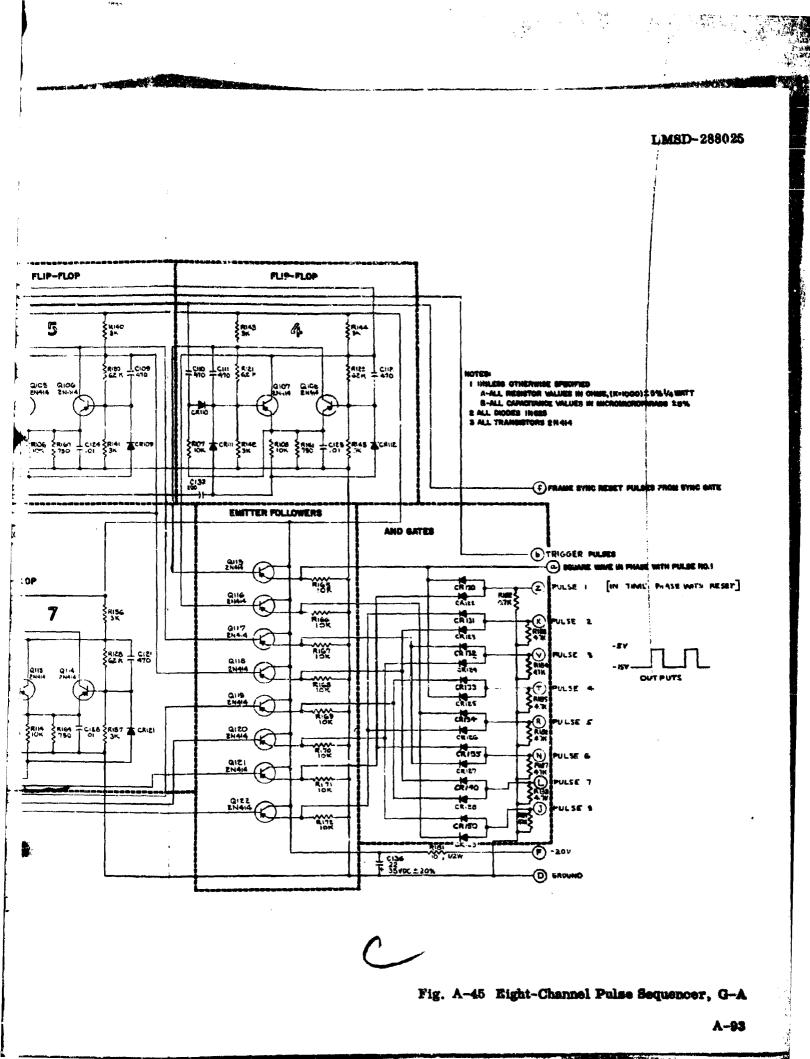

|     | 7.2.3.9  | Eight-Channel Pulse Sequencer                  | 7-36   |

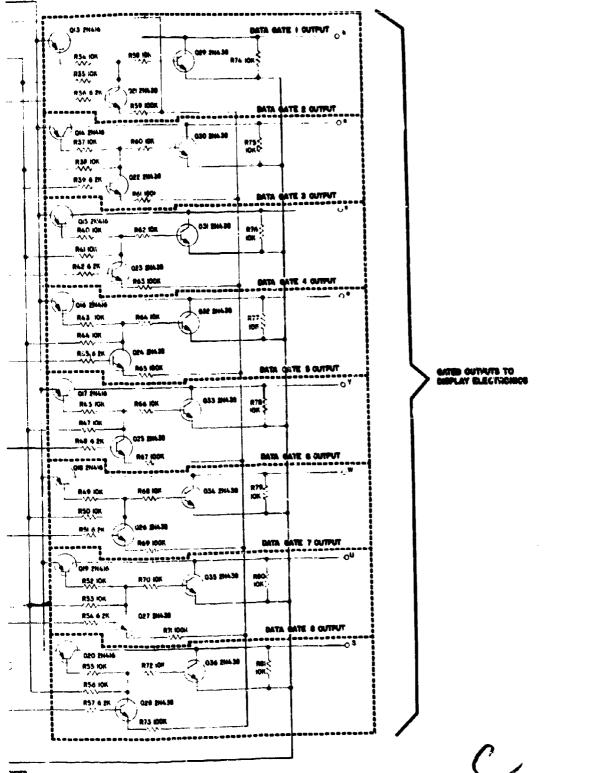

|     | 7.2.3.10 | Data Gates                                     | 7-36   |

|     | 7.2.3.11 | Data Sync Delay Record                         | 7-37   |

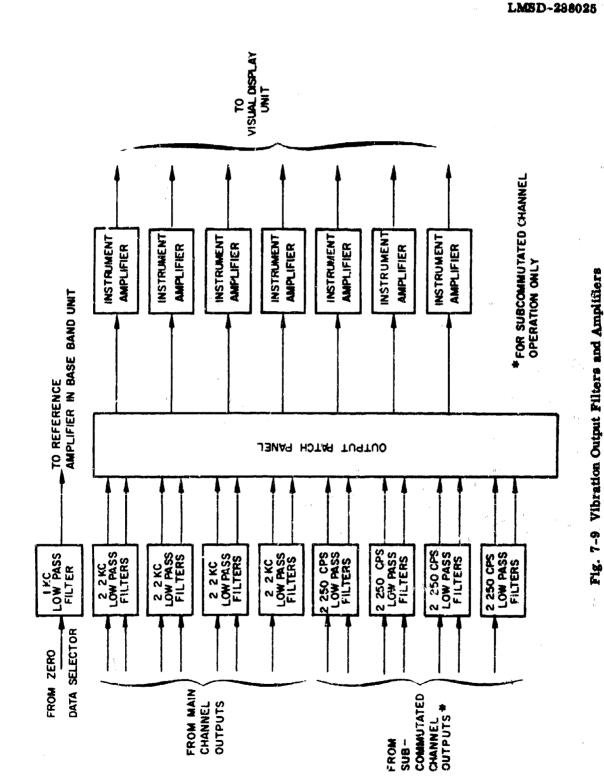

|     | 7.2.4    | Output Filters and Amplifiers                  | 7-38   |

|     | 7.2.5    | Visual Display Unit                            | 7 -40  |

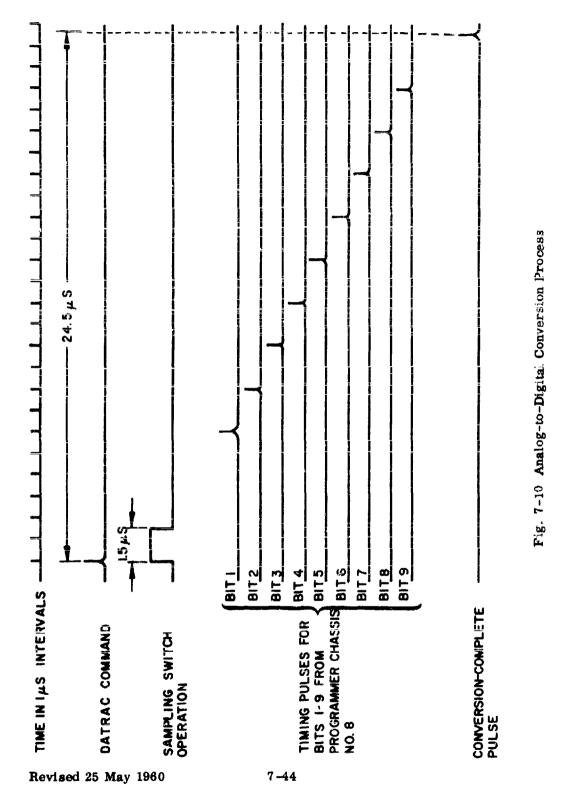

|     | 7.2.6    | Analog-to-Digital Converter                    | 7-40   |

|     | 7.2.7    | Digital Record Electronics                     | 7-46   |

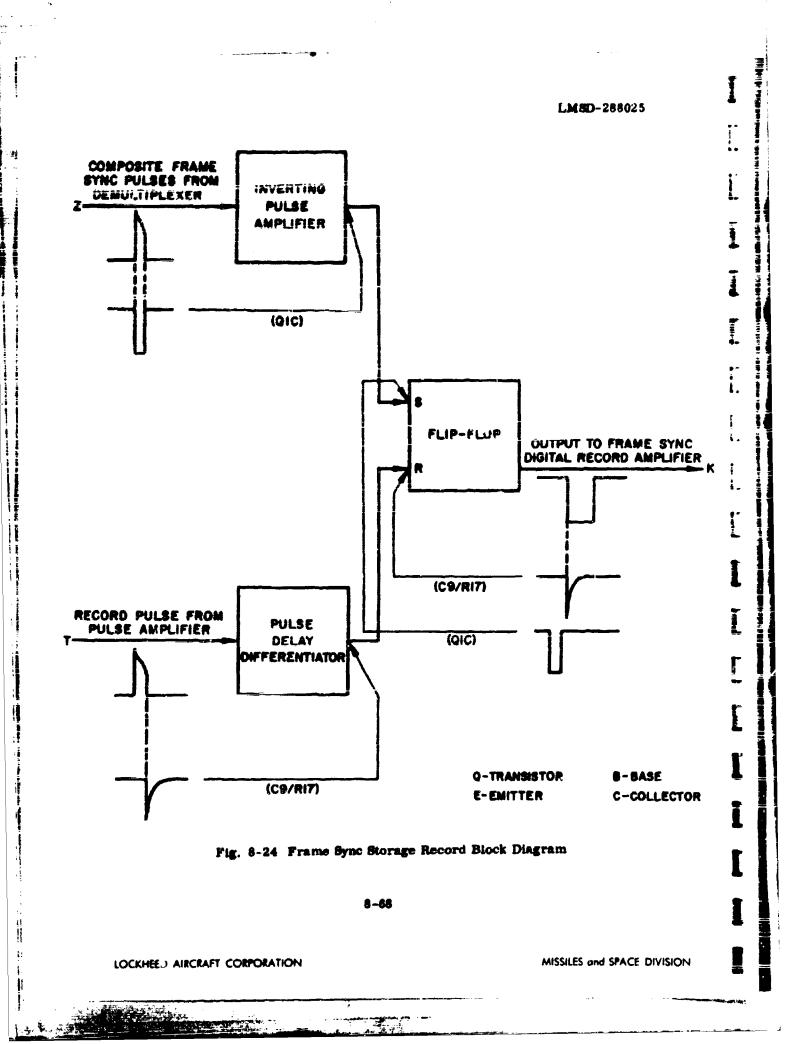

|     | 7.2.7.1  | Frame Sync Storage Record                      | 7-48   |

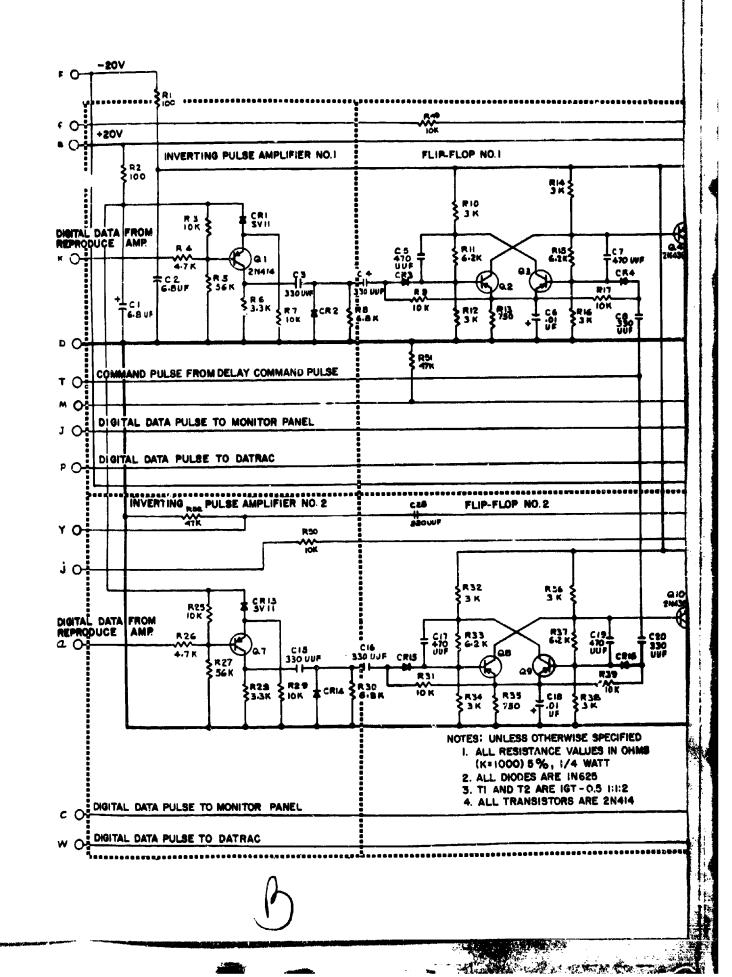

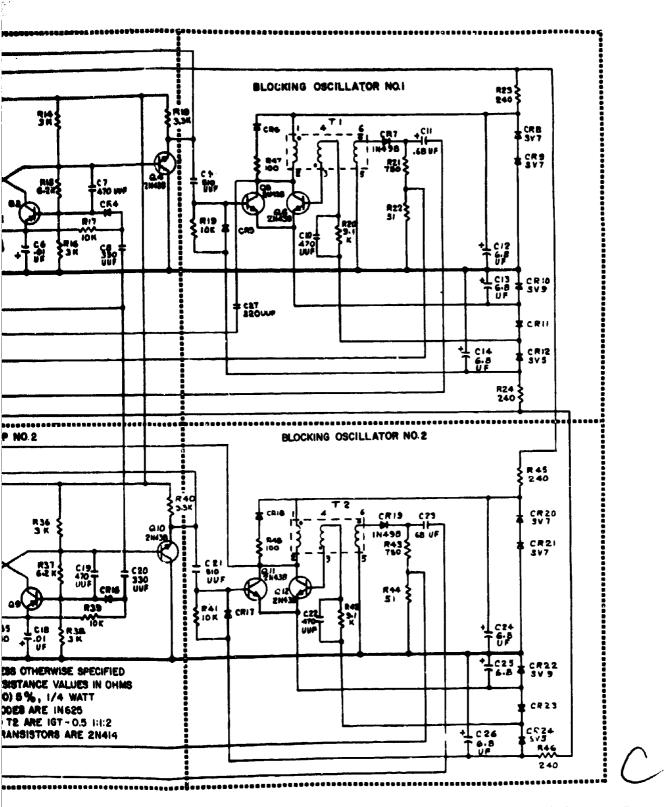

|     | 7.2.7.2  | Pulse Amplifier                                | 7-49   |

|     | 7.2.7.3  | Digital Record Amplifier                       | 7 -49  |

|     | 7.2.8    | Magnetic Tape Recorder                         | 7-51   |

|     | 7.2.9    | Digital Reproduce Electronics                  | 7-52   |

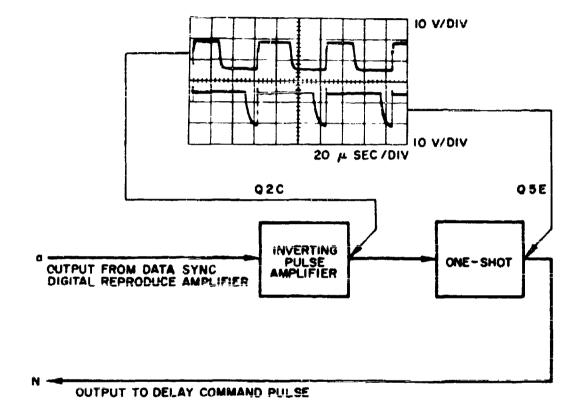

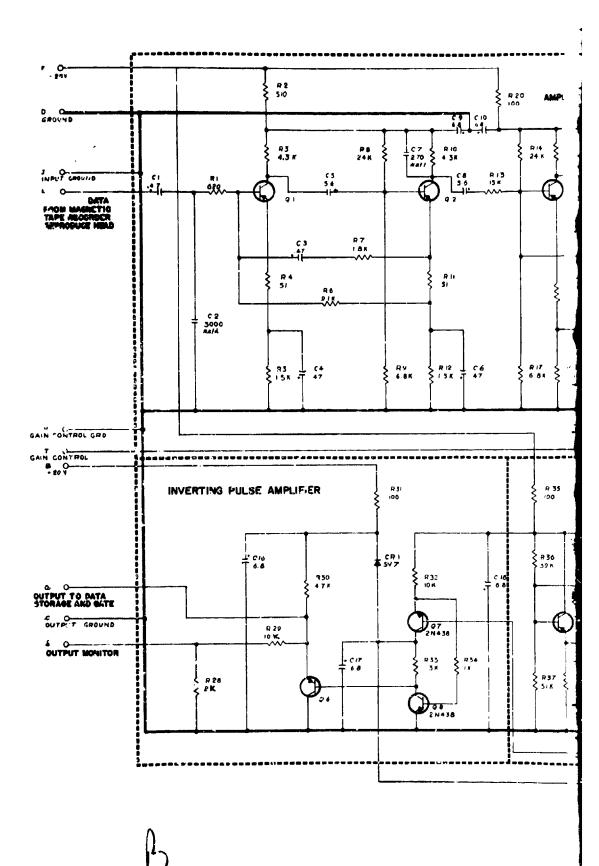

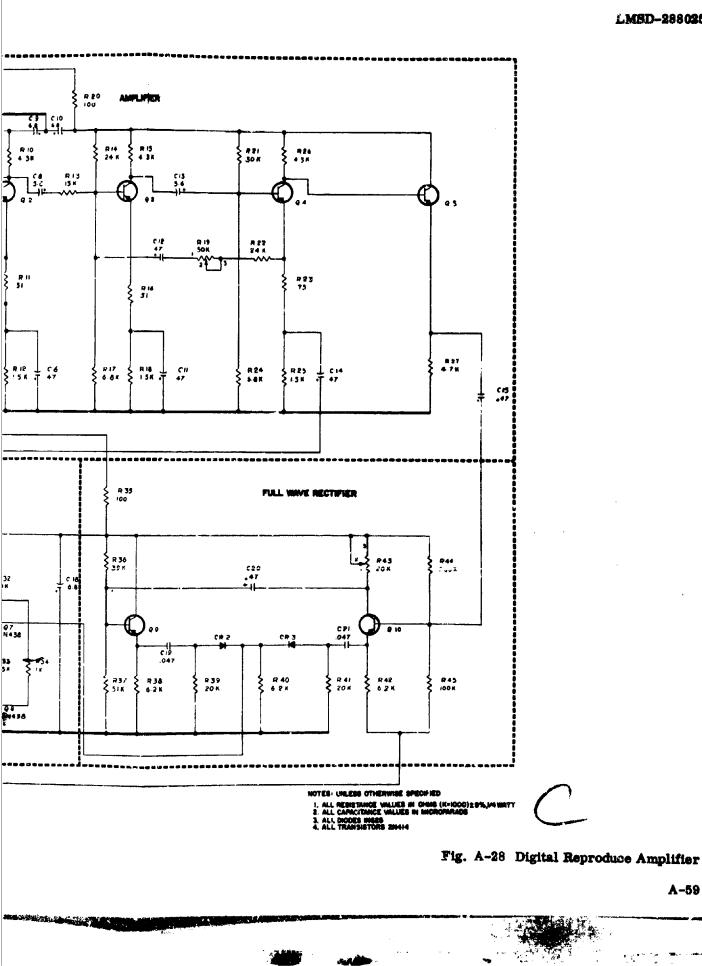

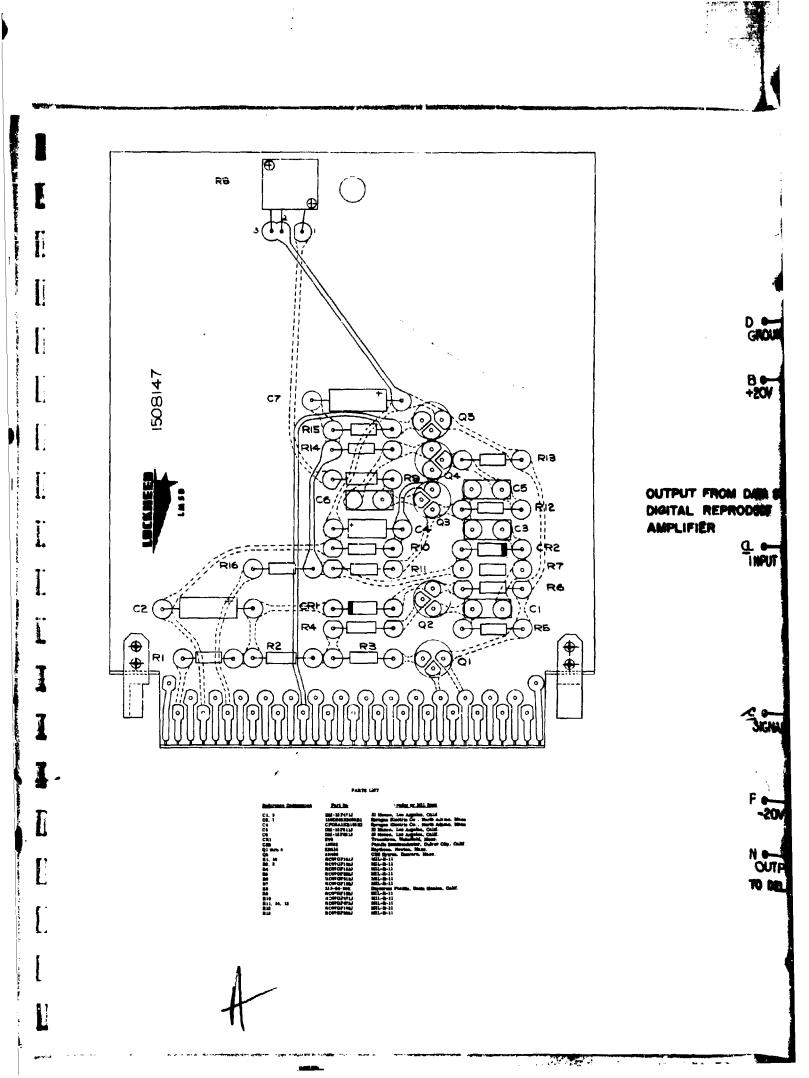

|     | 7.2.9.1  | Digital Reproduce Amplifier                    | 7-54   |

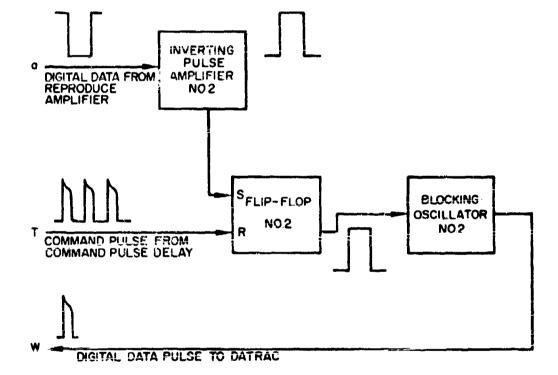

|     | 7,2.9.2  | Data Storage and Gate                          | 7 -55  |

|     | 7.2.9.3  | Data Sync Delay Reproduce                      | 7 - 57 |

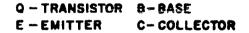

|     | 7.2.9.4  | Delay Command Pulse                            | 7 - 57 |

|     | 7.2.10   | Digital-to-Analog Converter                    | 7-58   |

|     | 7.2.11   | Base Band Unit, Reproduce Mode                 | 7 - 59 |

|     | 7.2.12   | Demultiplexer, Reproduce Mode                  | 7 ~59  |

|     | 7.2.12.1 | Duty Cycle I                                   | 7-59   |

|     | 7.2.12.2 | Frame Sync Delay Reproduce                     | 7-63   |

|     | 7.2.13   | Power Supply Interlock                         | 7-64   |

|     | 7.2.14   | Relay Board                                    | 7-64   |

|     | 7, 2, 15 | Main Monitor Panel                             | 7-65   |

|     | 7.2.16   | Signal Strength and Voice Record and Reproduce |        |

|     |          | Filters                                        | 7-65   |

| 7.3 | G-A      |                                                | 7-67   |

|     | 7.3.1    | Receiver                                       | 7-67   |

Section

× . . .

핵교

viii

TED AIRCRAFT CORPORATION

|          |                                  | Page  |

|----------|----------------------------------|-------|

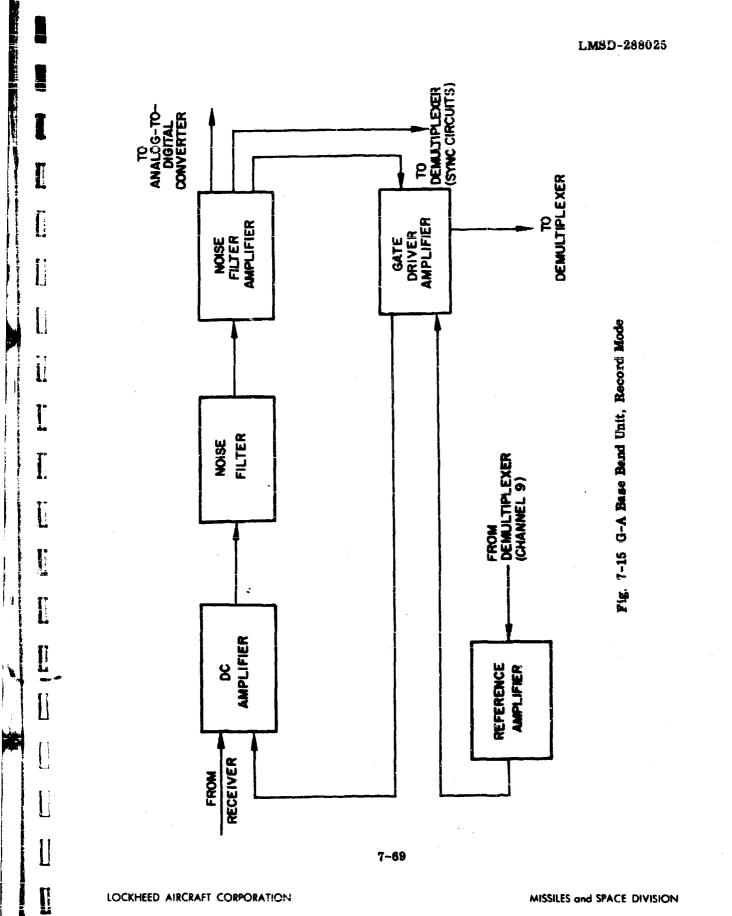

| 7.3.2    | Base Band Unit, Record Mode      | 7-67  |

| 7.3.2.1  | DC Amplifier                     | 7-71  |

| 7.3.2.2  | Noise Filter                     | 7-73  |

| 7,3.2.3  | Noise Filter Amplifier           | 7-74  |

| 7.3.2.4  | Reference Voltage Optional Clamp | 7-76  |

| 7.3.2.5  | Gate Driver Amplifier            | 7-77  |

| 7.3.2.6  | Reference Amplifier              | 7-78  |

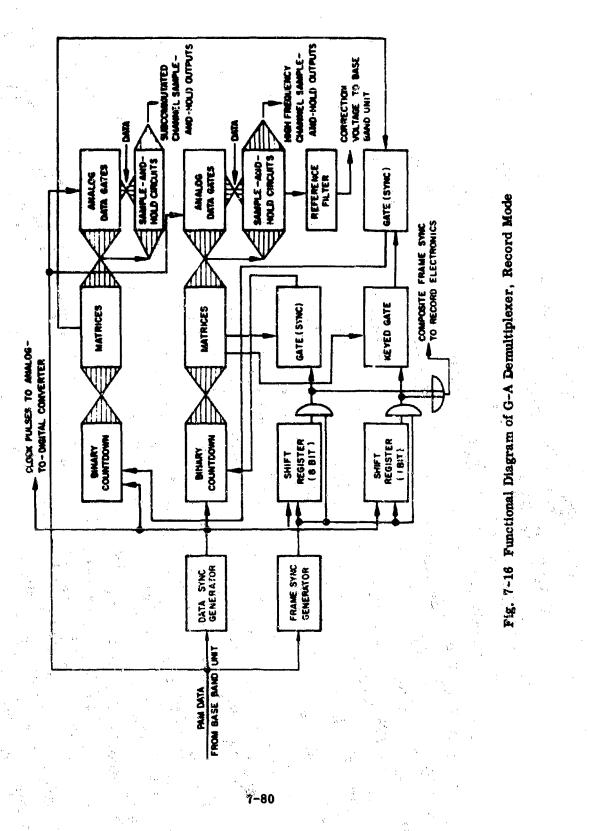

| 7.3.3    | Demultiplexer, Record Mode       | 7-79  |

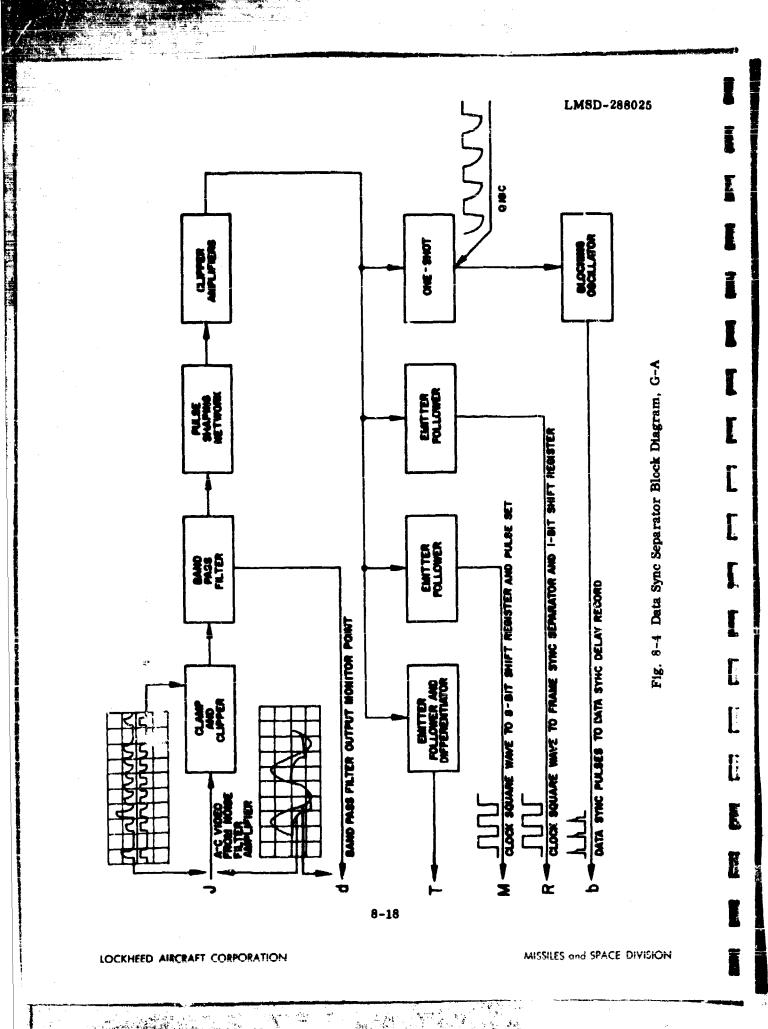

| 7.3.3.1  | Data Sync Separator              | 7-82  |

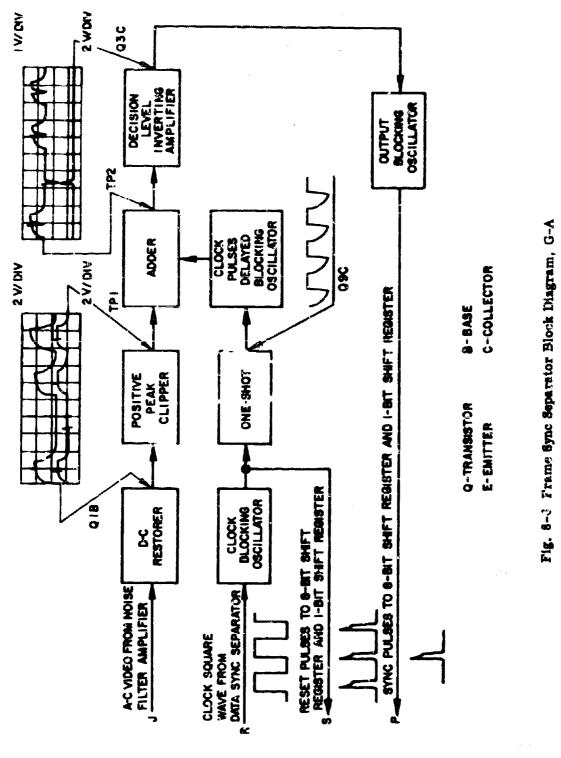

| 7.3.3.2  | Frame Sync Separator             | 7-85  |

| 7.3.3.3  | Eight-Bit Shift Register         | 7-86  |

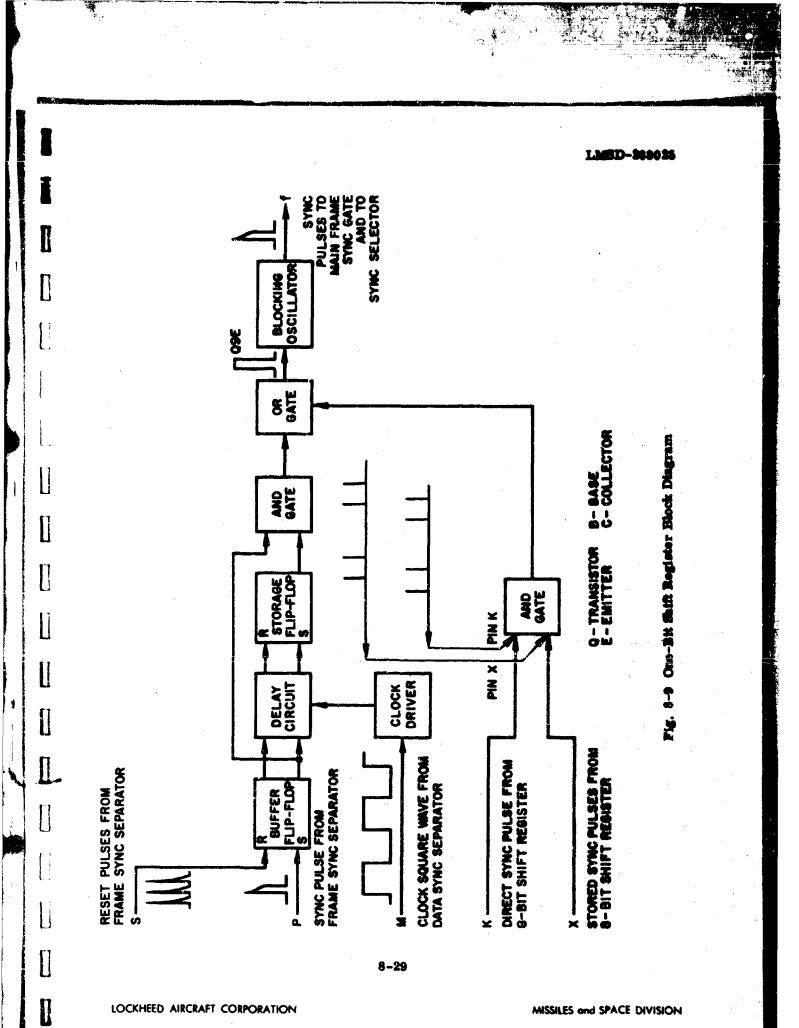

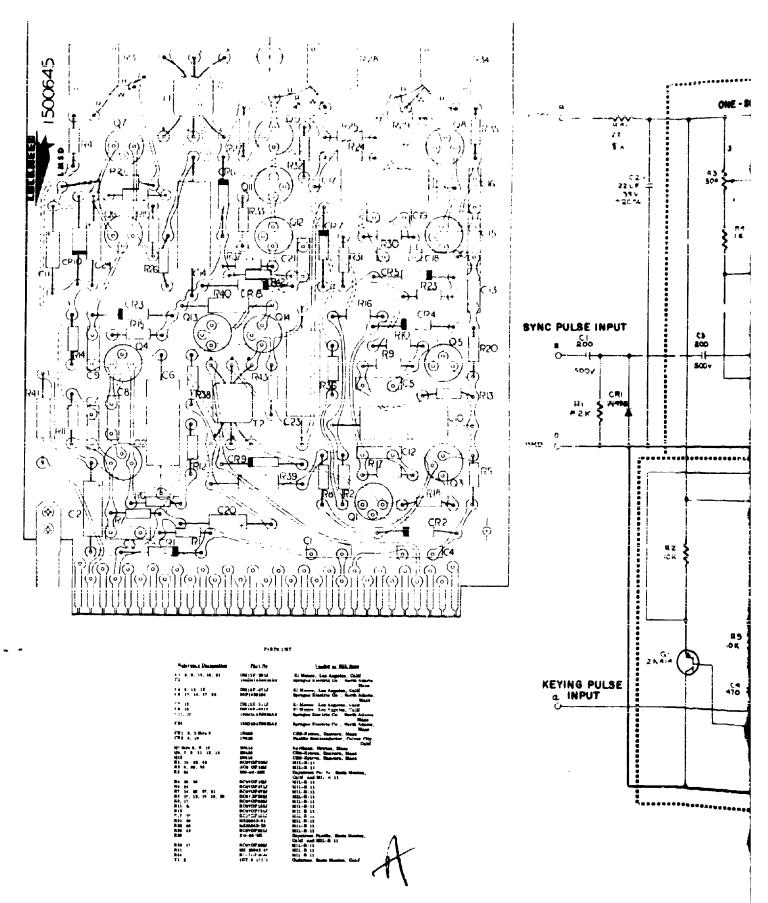

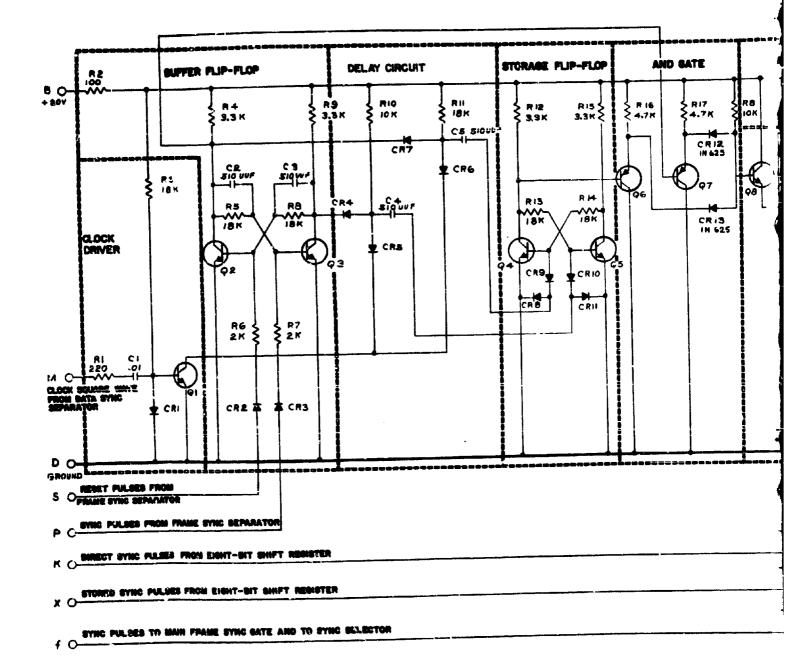

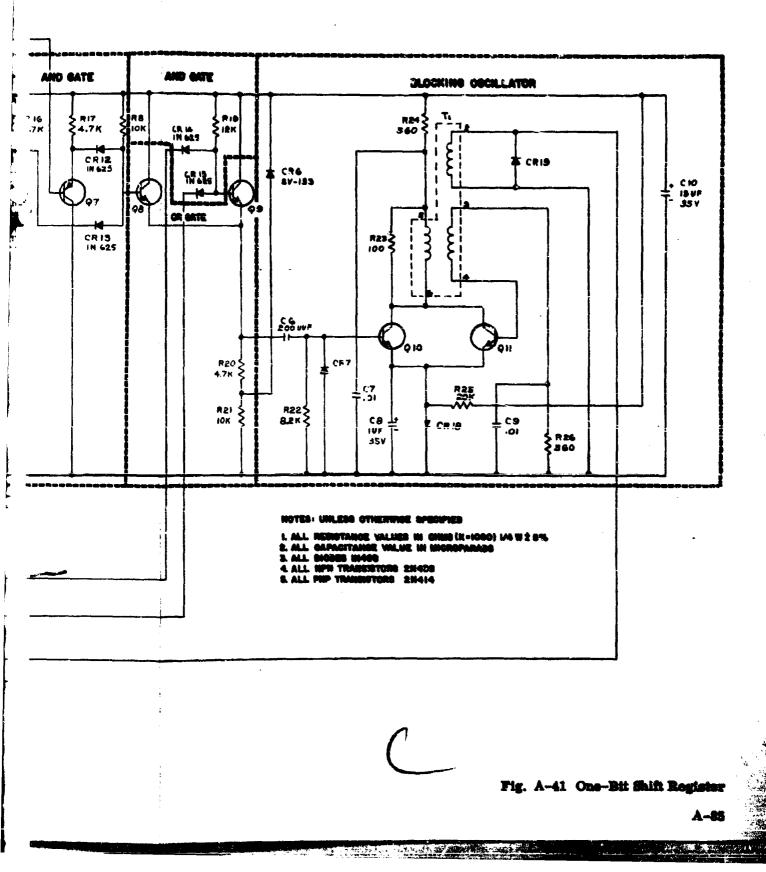

| 7.3.3.4  | One-Bit Shift Register           | 7-87  |

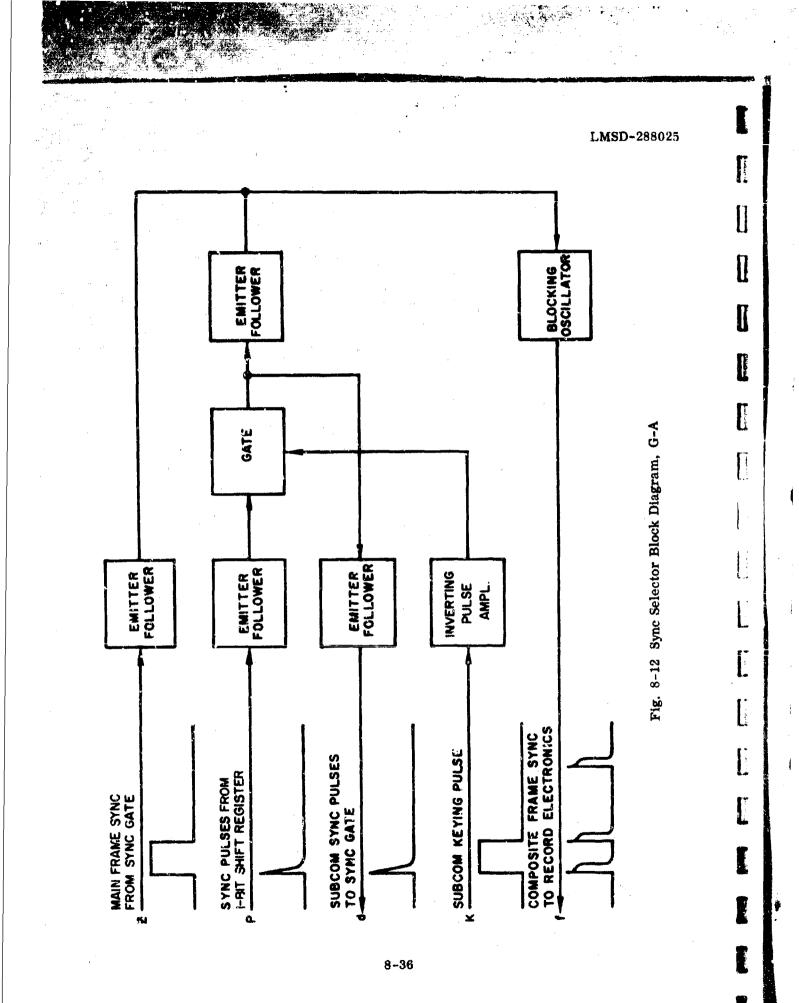

| 7.3.3.5  | Sync Selector                    | 7-89  |

| 7.3.3.6  | Sync Gate                        | 7-90  |

| 7.3.3.7  | Frequency Divider                | 7-92  |

| 7.3.3.8  | Eight-Channel Pulse Sequencer    | 7-92  |

| 7.3.3.9  | Matrix                           | 7-93  |

| 7.3.3.10 | Data Gates                       | 7-93  |

| 7,3.3.11 | Puise Set                        | 7-94  |

| 7.3.3.12 | Duty Cycle II                    | 7-96  |

| 7.3.3.13 | Data Sync Delay Record           | 7-96  |

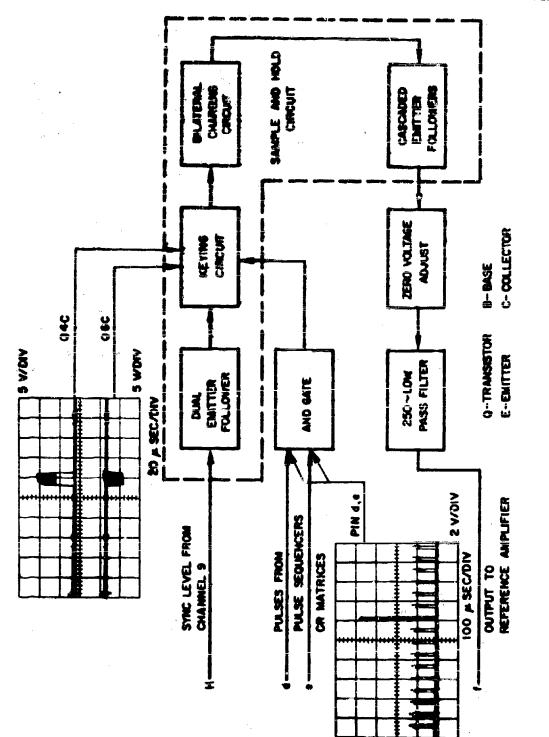

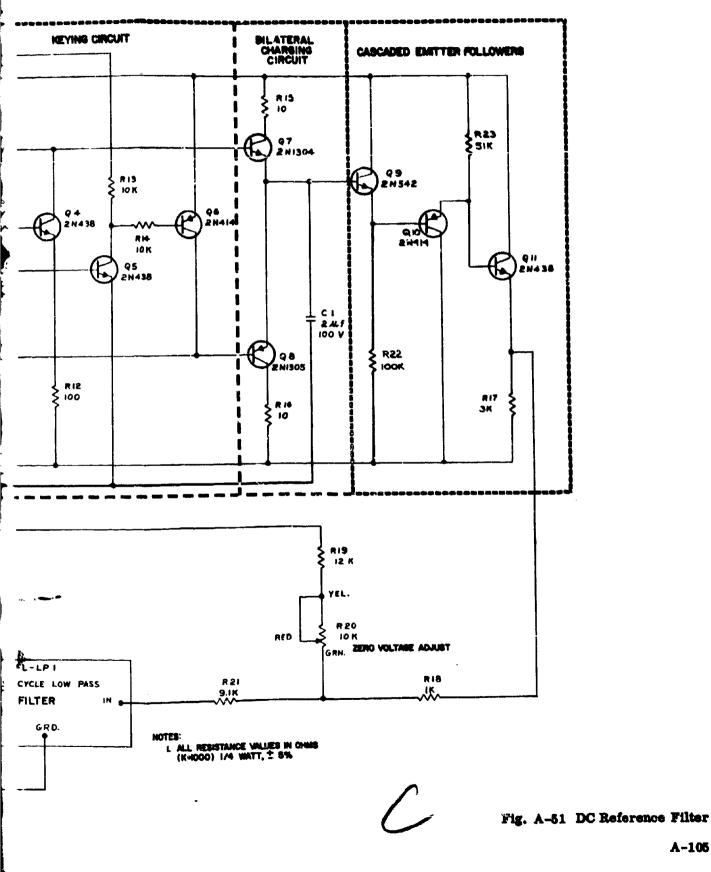

| 7. 3.14  | DC Reference Filter              | 7-97  |

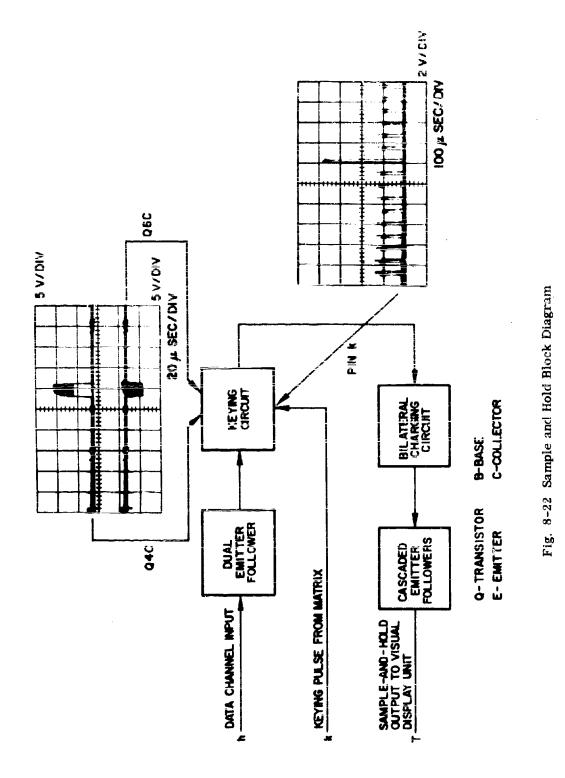

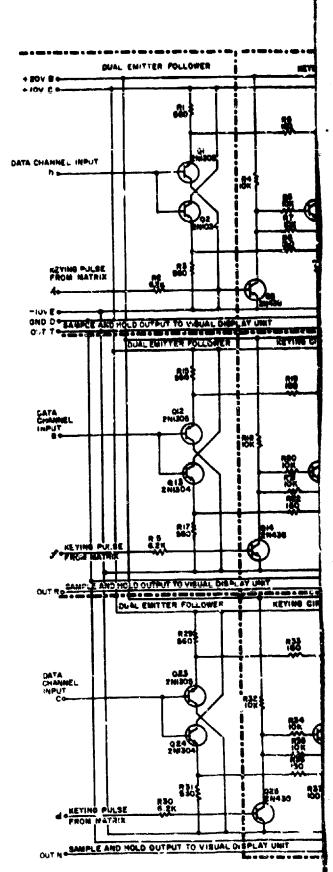

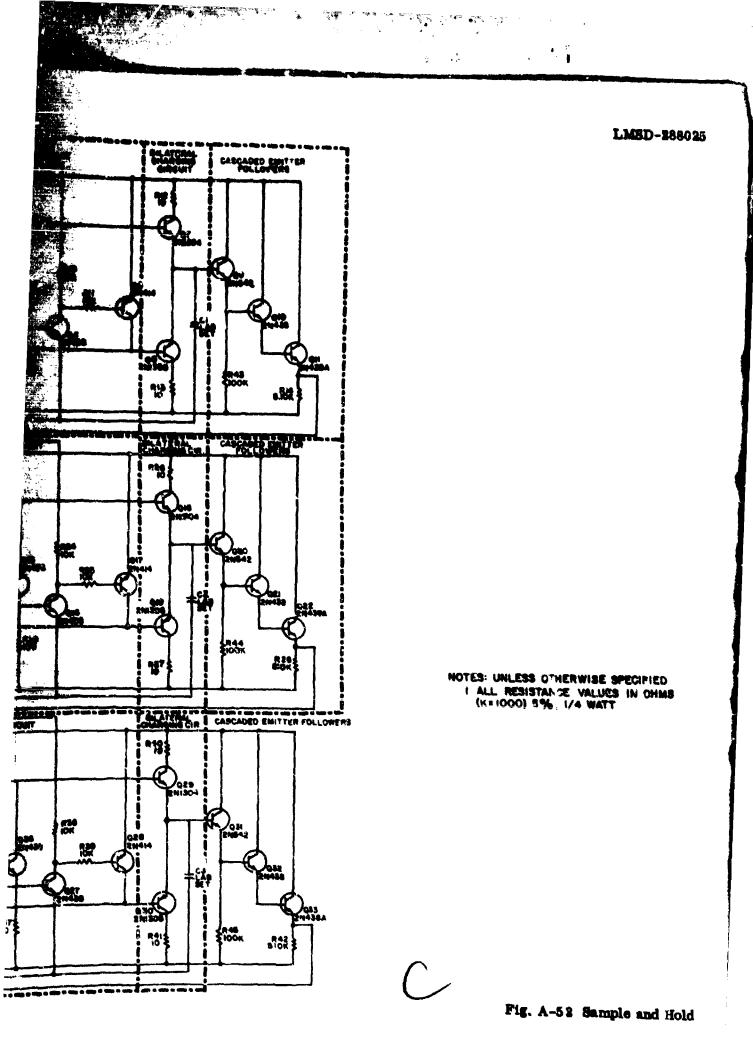

| 7.3.4    | Sample and Kold Output Circuits  | 7-98  |

| 7,3.4.1  | Sample and Hold                  | 7-100 |

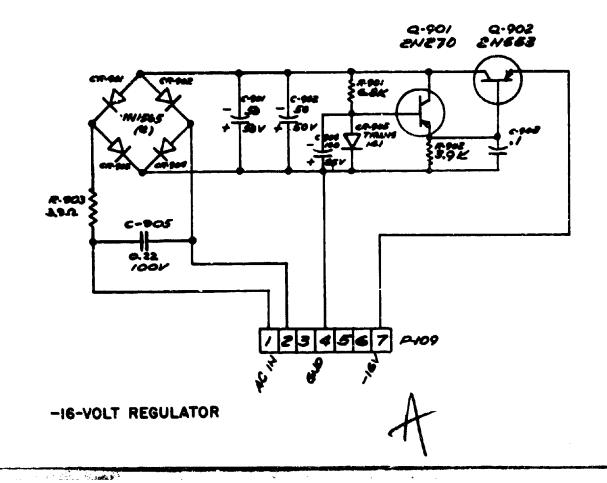

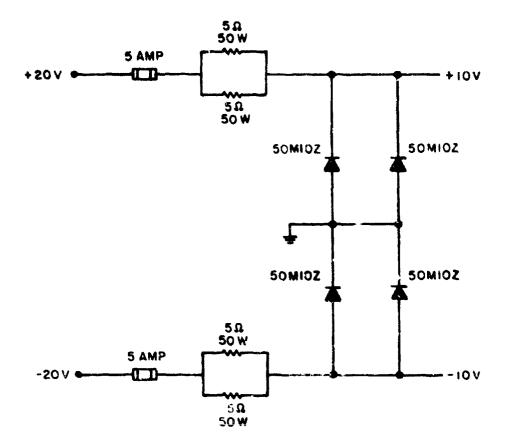

| 7.3.4.2  | Plus/Minus 10-Volt Regulator     | 7~101 |

| 7.3.5    | Analog-to-Digital Converter      | 7-102 |

| 7.3.6    | Digital Record Electronics       | 7-107 |

| 7.3.6.1  | Frame Sync Storage Record        | 7-107 |

| 7.3.6.2  | Pulse Amplifier                  | 7-108 |

| 7.3.6.3  | Digital Record Amplifier         | 7-109 |

# Section

ł

į.

$!_{i,j}$

1

11

**1**

۲. 14

4= 3 } #4∖

11

í

۱ ۹.

1

ŧ

F

----

Ą

L

ţ. ÷ -

i .

Ľ

Ľ

E

Ĩ

Ľ

ŧ

Į

| ion |      |            |                                                         | Page  |

|-----|------|------------|---------------------------------------------------------|-------|

|     |      | 7.3.7      | Magnetic Tape Recorder                                  | 7-110 |

|     | · .  | 7.3.8      | Digital Reproduce Electronics                           | 7-111 |

|     |      | 7.3.8.1    | Digital Reproduce Amplifier                             | 7-112 |

|     |      | 7.3.8.2    | Data Storage and Gate                                   | 7-114 |

|     |      | 7.3.8.3    | Data Sync Delay Reproduce                               | 7-115 |

|     |      | 7.3.8.4    | Delay Command Pulse                                     | 7-116 |

|     |      | 7.3.9      | Digital-to-Analog Converter                             | 7-117 |

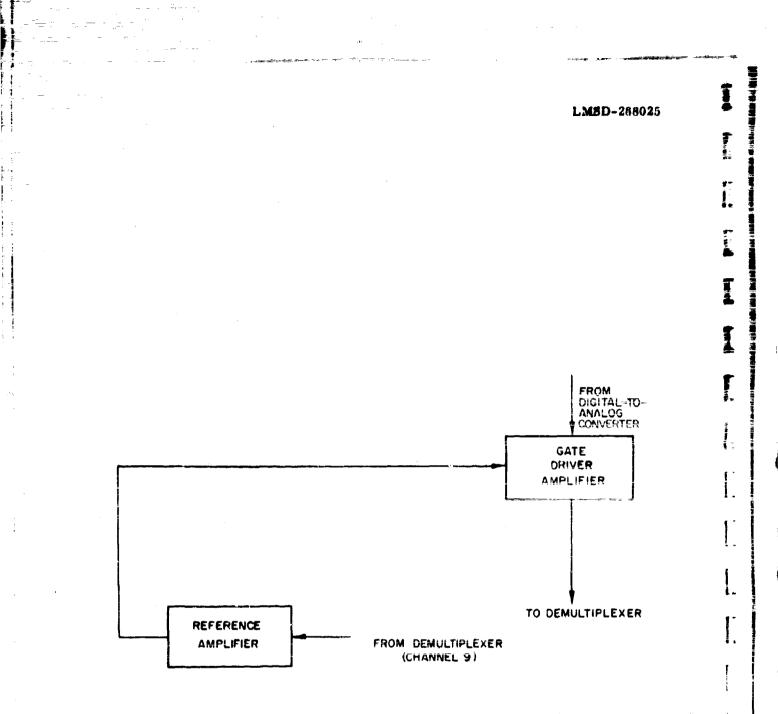

|     |      | 7.3.10     | Base Band Unit, Reproduce Mode                          | 7-117 |

|     |      | 7.3.11     | Demultiplexer, Reproduce Mode                           | 7-117 |

|     |      | 1.3.11.1   | Frame Sync Delay Reproduce                              | 7-120 |

|     |      | 7.3.12     | Power Supply Interlock                                  | 7-121 |

|     |      | 7.3.13     | Test Signal Generator                                   | 7-121 |

|     |      | 7.3.14     | Relay Board                                             | 7-122 |

|     |      | 7.3.15     | Main Monitor Panel                                      | 7-123 |

|     |      | 7.3.16     | Signal Strength and Voice Record and                    |       |

|     |      |            | Reproduce Filters                                       | 7-123 |

| •   | MAIN | ITENANCE   | 2                                                       |       |

|     | 8.1  | Introducti | lon                                                     | 8-1   |

|     |      | 8.1.1      | Scope                                                   | 8-1   |

|     |      | 8.1.2      | General Information                                     | 8-2   |

|     | 8.2  | General I  | instructions                                            | 8-3   |

|     | 8.3  | Troubles   | hooting for Absent or Incorrect Inputs                  | 8-4   |

|     | 8.4  | Troubles   | hooting Blocking Oscillators, One-Shots, and Flip-Flops | 8-5   |

|     |      | 8.4.1      | Blocking Oscillator                                     | 8-5   |

|     |      | 8.4.2      | One-Shot                                                | 8-6   |

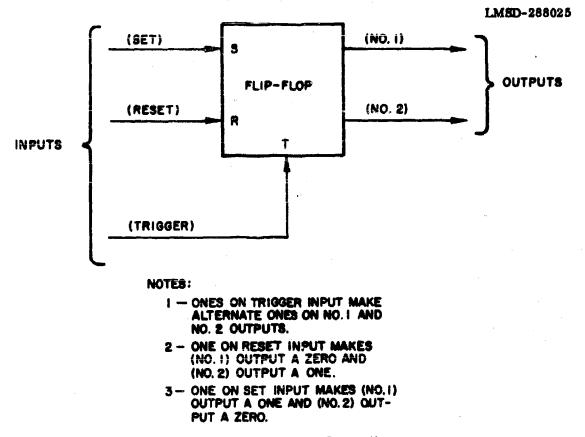

|     |      | 8.4.3      | Flip-Flop                                               | 8-6   |

|     | 8.5  | Receiver   |                                                         | 8-7   |

|     | 8.6  | DC Ampl    | ifier                                                   | 8-7   |

|     | 8.7  | Noise Fil  | ter, Vibration                                          | 8-10  |

|     | 8.8  | Noise Fil  | ter, G-A                                                | 8-11  |

# Sec

х

- <u>-</u>

warman and a

. . ...

Ī

a sea sa partir da la compañía de la

21.1

| Section |                                    | Page        |

|---------|------------------------------------|-------------|

| 8.9     | Noise Filter Amplifier             | 8-12        |

| 8.1     | 0 Reference Voltage Optional Clamp | 8-13        |

| 8.1     | 1 Gate Driver Amplifier            | 8-14        |

| 8.1     | 2 Reference Amplifier              | 8-16        |

| 8.1     | 3 Data Sync Separator              | 8-16        |

| 5.1     | 4 Frame Sync Separator             | 8-21        |

| 8.1     | 5 Eight-Bit Shift Register         | 8-24        |

| 8.1     | 6 One-Bit Shift Register           | 8-28        |

| 8.1     | 7 Programmer                       | 8-32        |

| 8.1     | 8 Sync Selector                    | 8-34        |

| 8.1     | 9 Sync Gate                        | 8-37        |

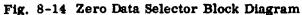

| 8.2     | 20 Zero Data Selector              | 8-40        |

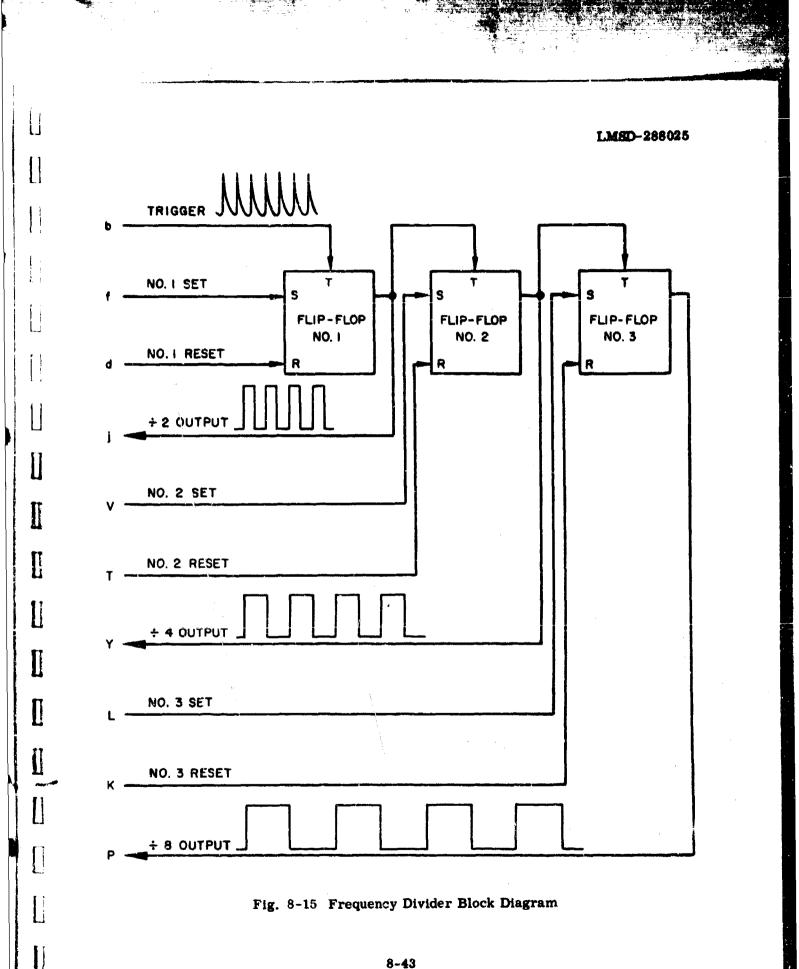

| 8,2     | 1 Frequency Divider                | 8-42        |

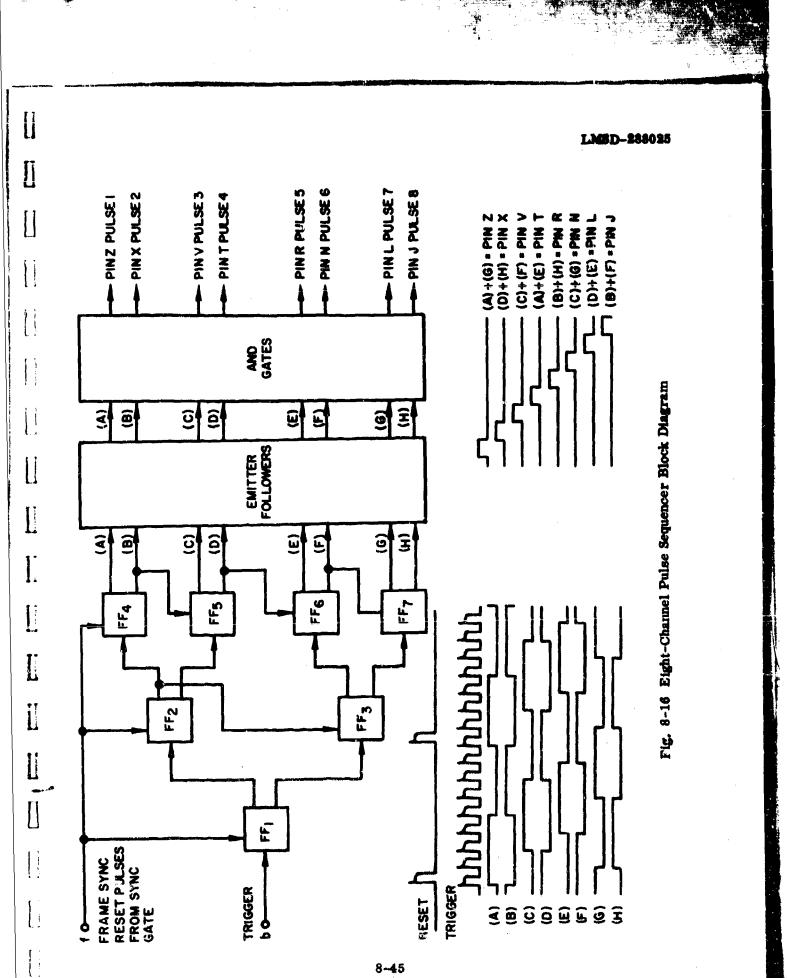

| 8,2     | 2 Eight-Channel Pulse Sequencer    | 8-44        |

| 8.2     | 3 Matrix                           | 8-49        |

| 8.2     | 4 Data Gates                       | 8-50        |

| 8.2     | 5 Pulse Set                        | 8-55        |

| 8.2     | 6 Duty Cycle II                    | 8-58        |

| 8.2     | 7 Data Sync Delay Record           | 8-60        |

| 8.2     | 8 Filter Board                     | 8-61        |

| 8.2     | 9 Sample and Hold                  | 8-61        |

| 8.3     | 0 DC Reference Filter              | 8-63        |

| 8.3     | 1 Frame Sync Storage Record        | 8-67        |

| 8.3     | 2 Pulse Amplifier                  | <b>8-69</b> |

| 8.3     | 3 Digital Record Amplifier         | 8-70        |

| 8.3     | 4 Digital Reproduce Amplifier      | 8-73        |

| 8.3     | 5 Data Storage and Gate            | 8-76        |

| 8.3     | 6 Data Sync Delay Reproduce        | 8-78        |

| 8.3     | 7 Delay Command Pulse              | 8-80        |

| 8.3     | 8 Duty Cycle I                     | 8-82        |

and an owner

ł

I

1.

. .

1

τ.

ί.

E

Į.

.,

Ŀ

Ι...

L

1

| Bection |                                  | Page |

|---------|----------------------------------|------|

|         | 8.39 Frame Sync Delay Reproduce  | 8-84 |

|         | 8.40 Analog-to-Digital Converter | 8-87 |

|         | 8.41 Magnetic Tape Recorder      | 8-87 |

|         | 8.42 Powar Supply Interlock      | 8-87 |

| 9.      | VACUUM TUBE VOLTAGE CHART        | 9-1  |

| 10.     | WIRING                           | 10-1 |

| 11.     | MONITOR SWITCH OUTPUTS           | 11-1 |

|         |                                  |      |

### Appendix

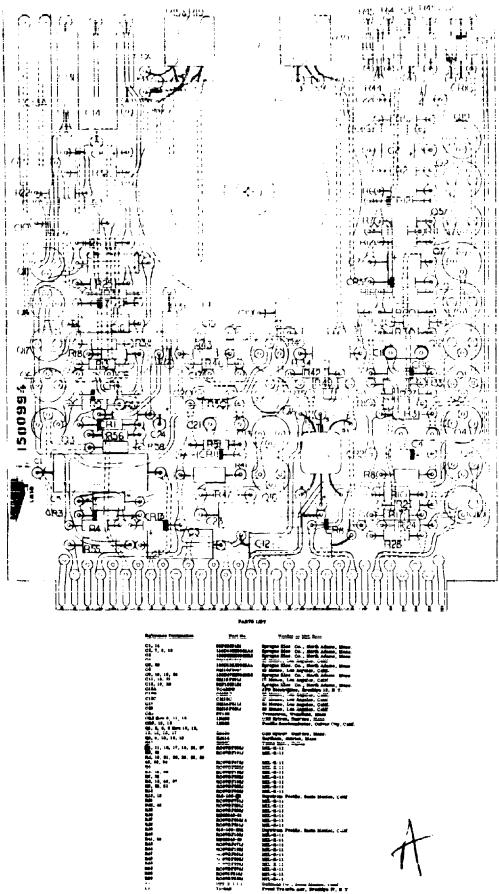

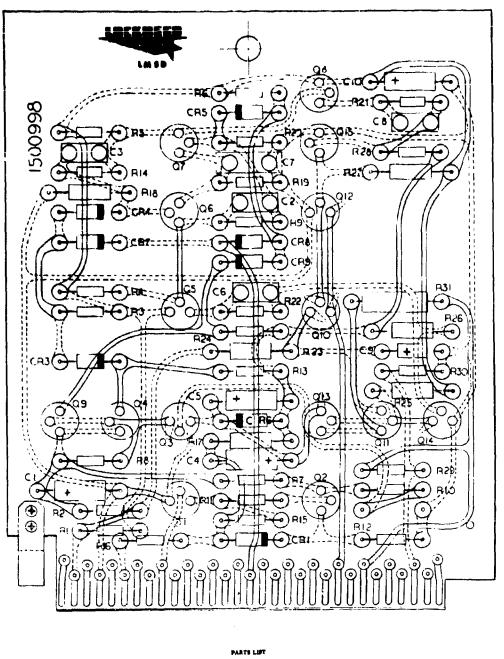

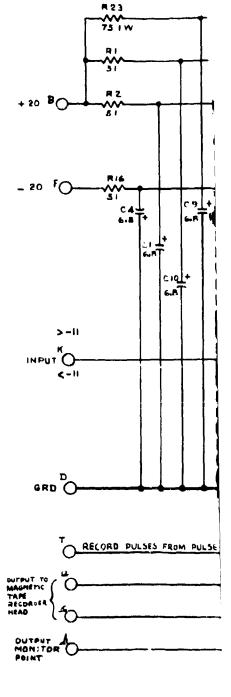

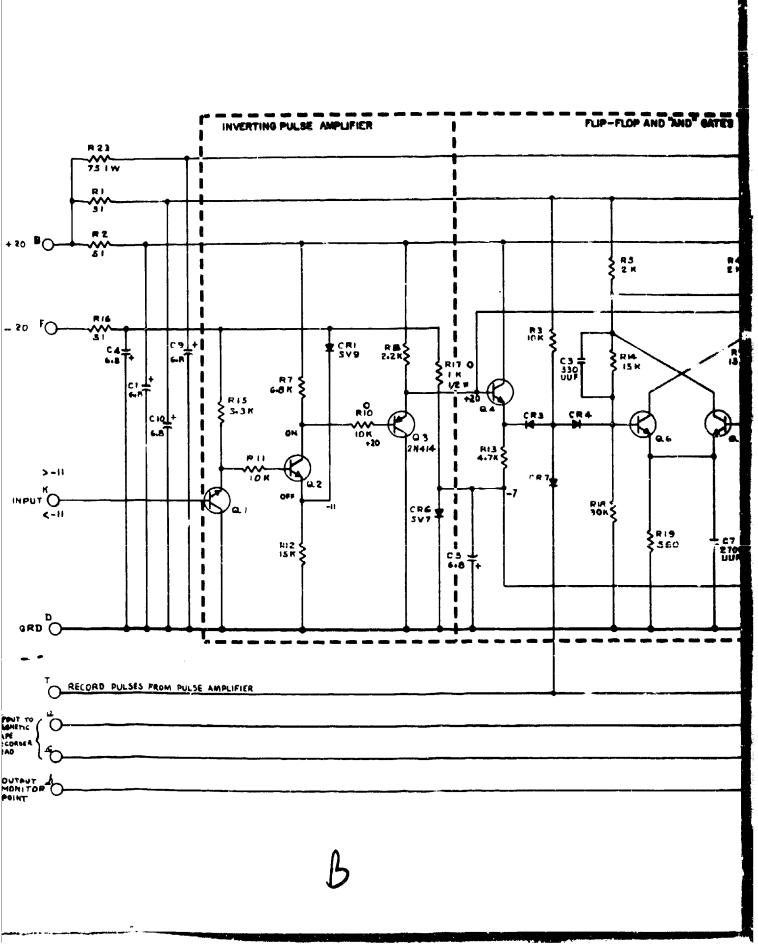

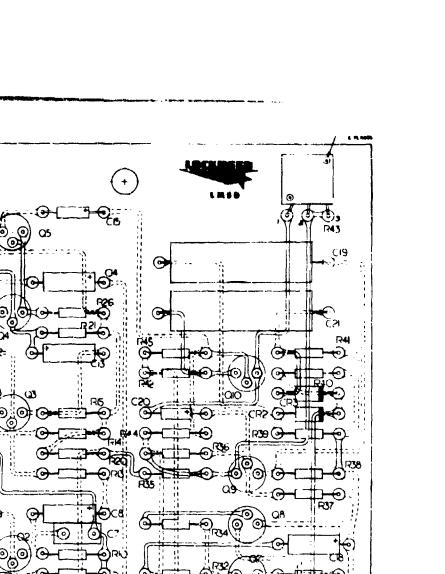

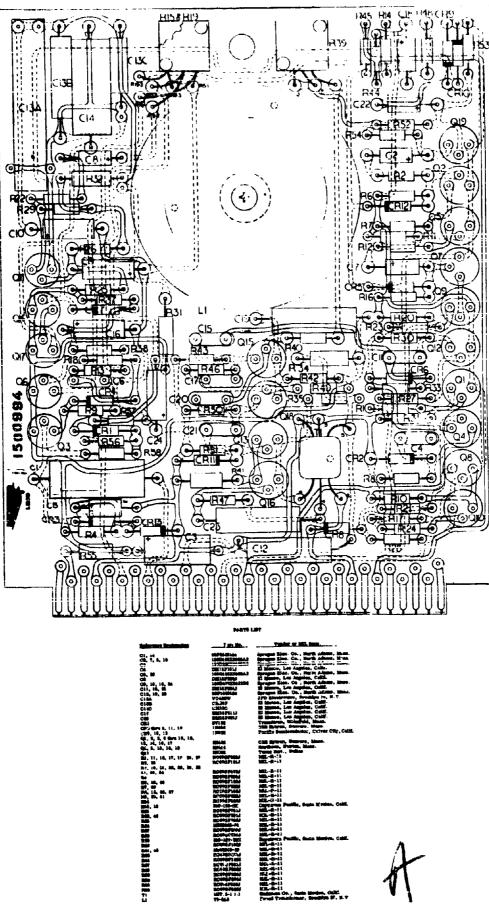

SCHEMATICS, PARTS LISTS, AND COMPONENT ASSEMBLIES

A-1

LOCKHEED AIRCRAFT CORPORATION

### LIST OF ILLUSTRATIONS

| Figure |                                                               | Page   |

|--------|---------------------------------------------------------------|--------|

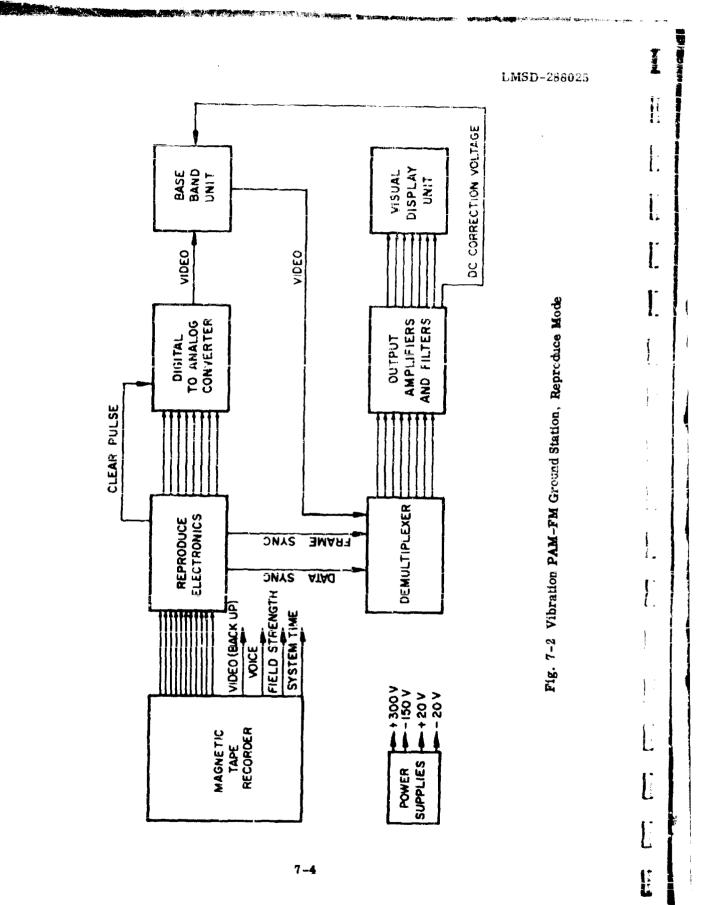

| 7-1    | Vibration PAM-FM Ground Station, Record Mode                  | 7-3    |

| 7 -2   | Vibration PAM-FM Ground Station, Reproduce Mode               | 7-4    |

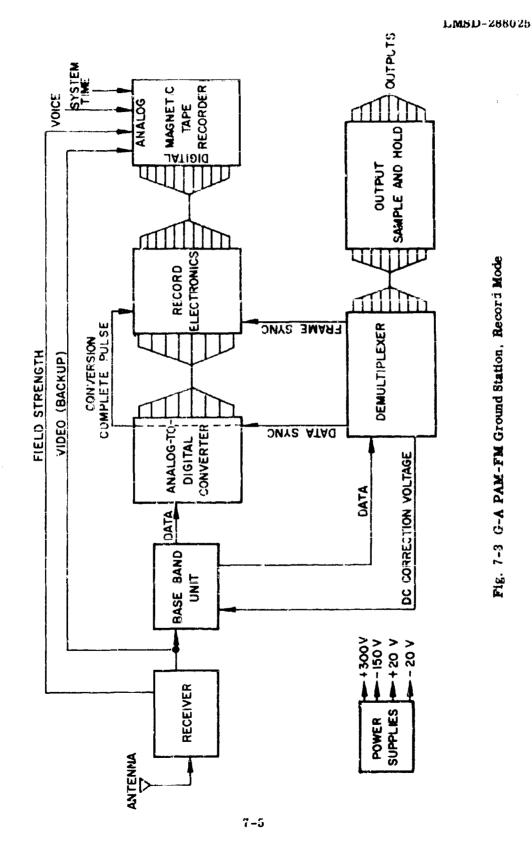

| 7-3    | G-A PAM-FM Ground Station, Record Mode                        | 7-5    |

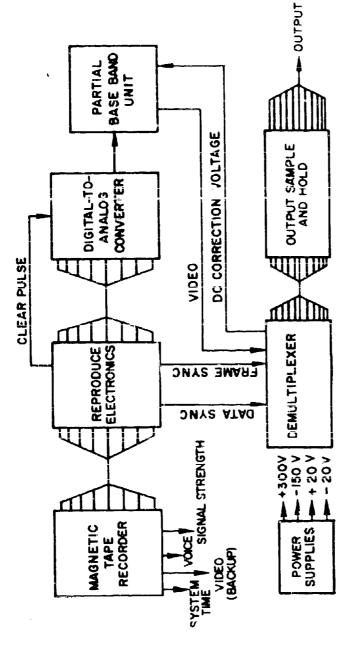

| 7 -4   | G-A PAM-FM Ground Station, Reproduce Mode                     | 7-6    |

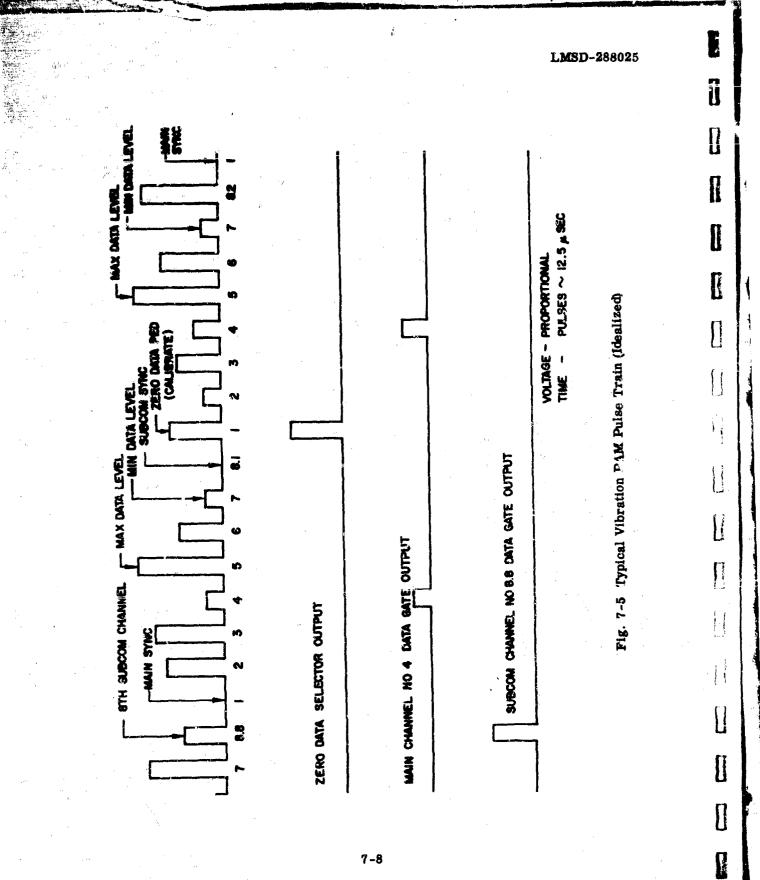

| 7-5    | Typical Vibration PAM Pulse Train (Idealized)                 | 7 -8   |

| 7 -6   | Typical G-A PAM Pulse Train (Idealized)                       | 7-10   |

| 7 -7   | Vibration Base Band Unit, Record Mode                         | 7-13   |

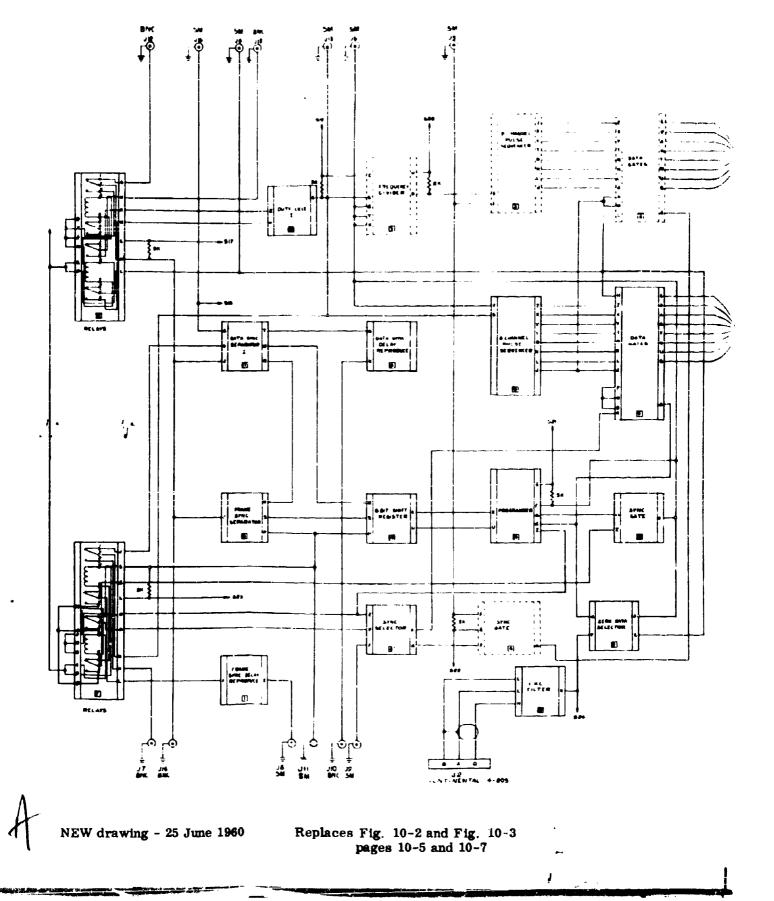

| 7 -8   | Functional Diagram of Vibration Demultiplexer, Record Mode    | 7-24   |

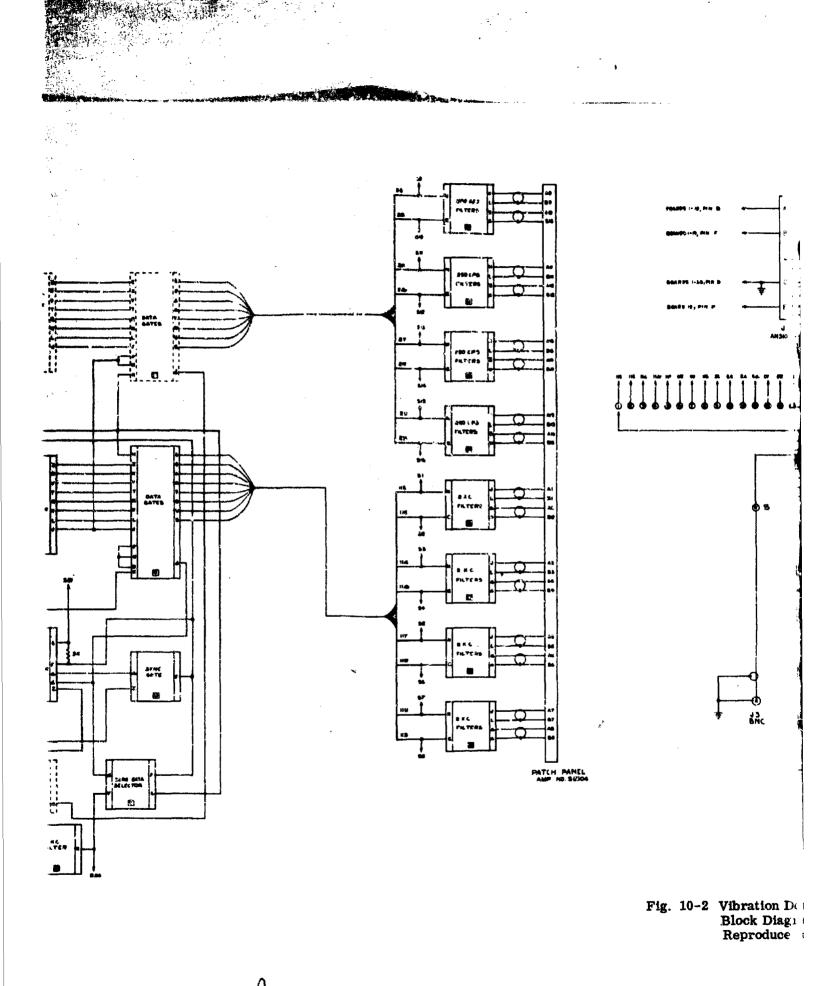

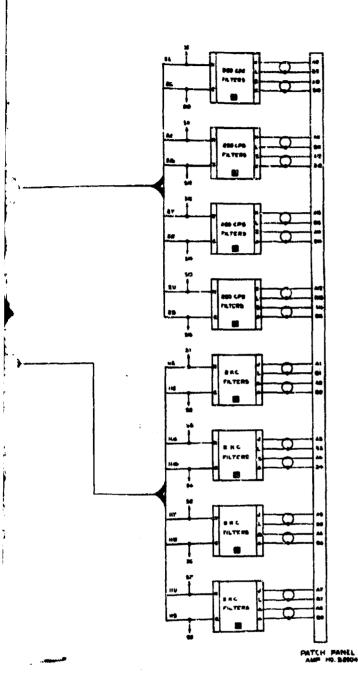

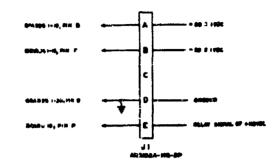

| 7 -9   | Vibration Output Filters and Amplifiers                       | 7 - 39 |

| 7-10   | Analog-to-Digital Conversion Process                          | 7-44   |

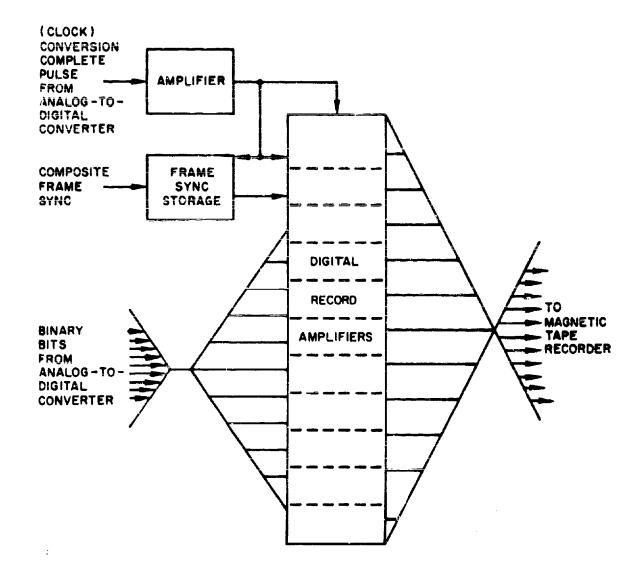

| 7-11   | Functional Diagram of Digital Record Electronics              | 7 -47  |

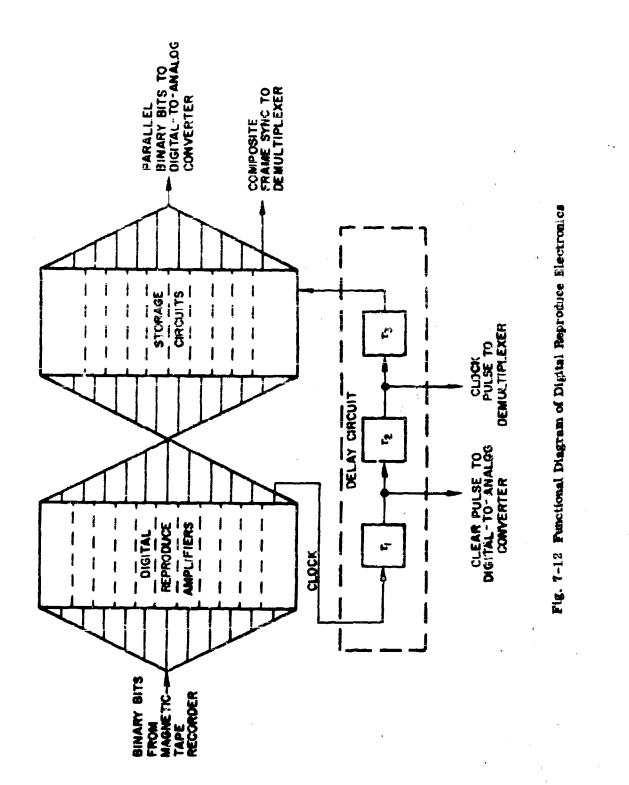

| 7-12   | Functional Diagram of Digital Reproduce Electronics           | 7 -53  |

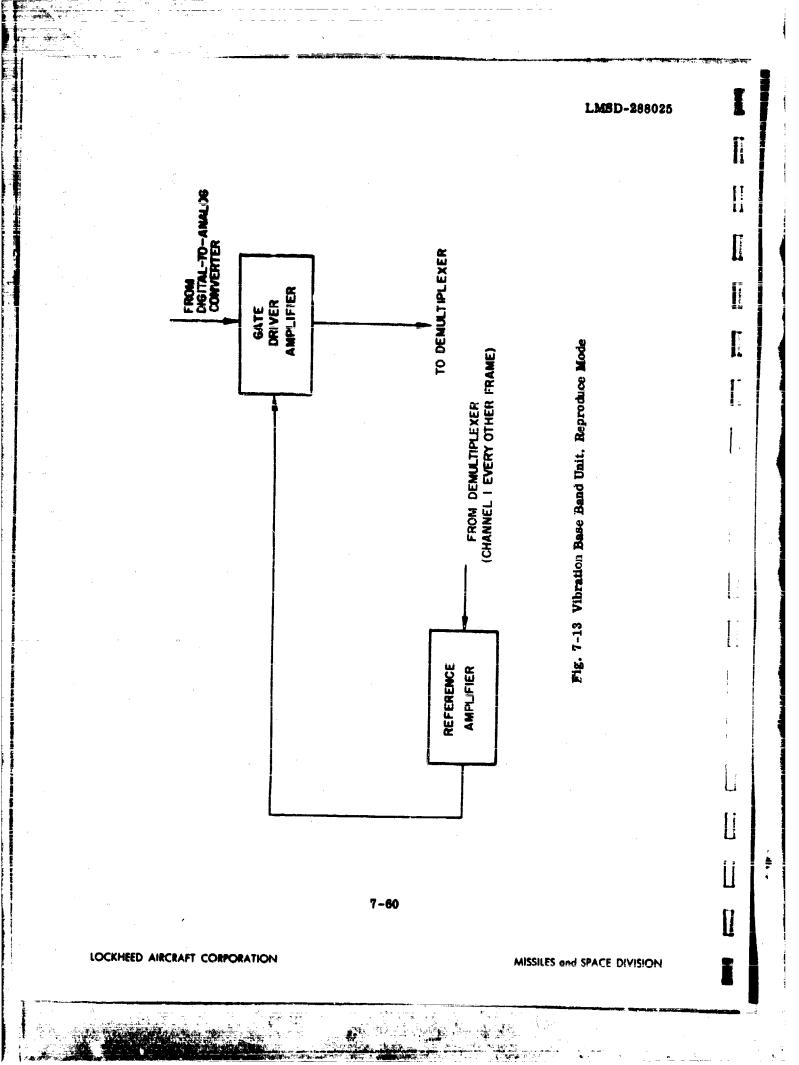

| 7-13   | Vibration Base Band Unit, Reproduce Mode                      | 7 -60  |

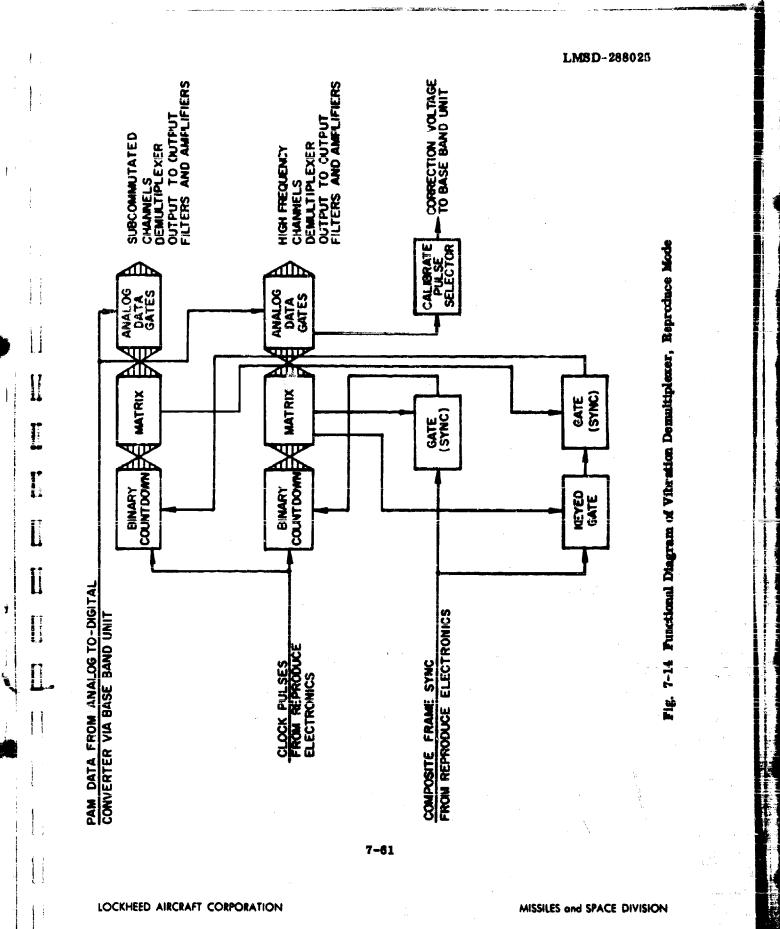

| 7-14   | Functional Diagram of Vibration Demultiplexer, Reproduce Mode | 7-61   |

| 7-15   | G-A Base Band Unit, Record Mode                               | 7 -89  |

| 7-16   | Functional Diagram of G-A Demultiplexer, Record Mode          | 7 -80  |

| 7-17   | G-A Sample and Hold Output Circuits                           | 7-99   |

| 7-18   | G-A Base Band Unit, Reproduce Mode                            | 7-118  |

| 7 -19  | Functional Diagram of G-A Demultiplexer, Reproduce Mode       | 7-119  |

| 8-1    | Flip-Flop Convention                                          | 8-3    |

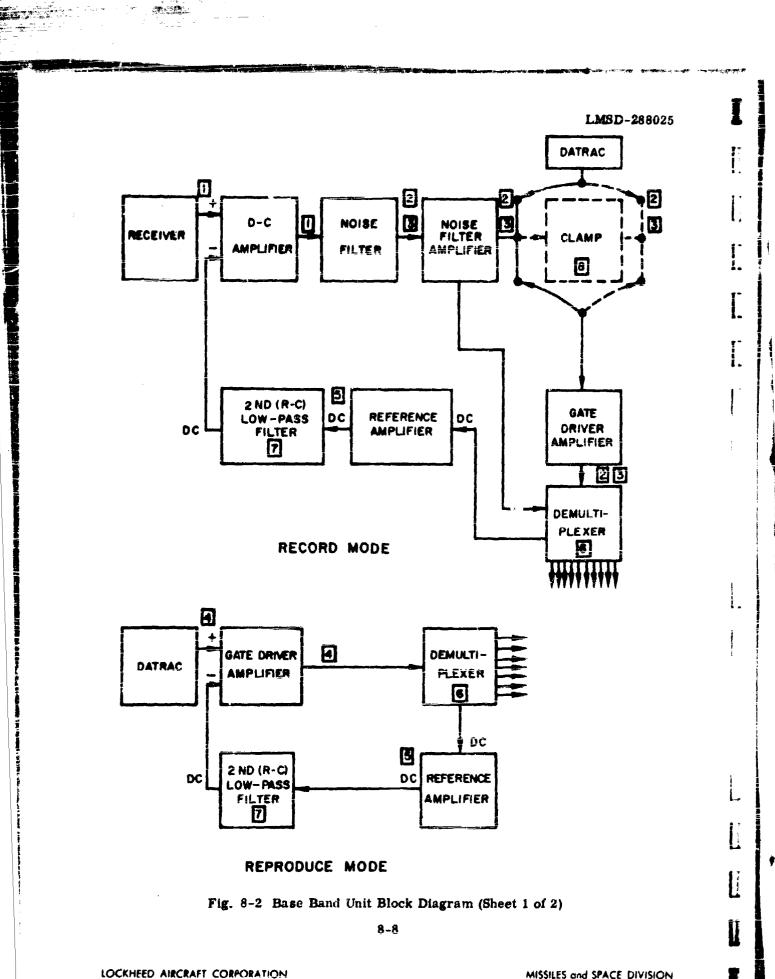

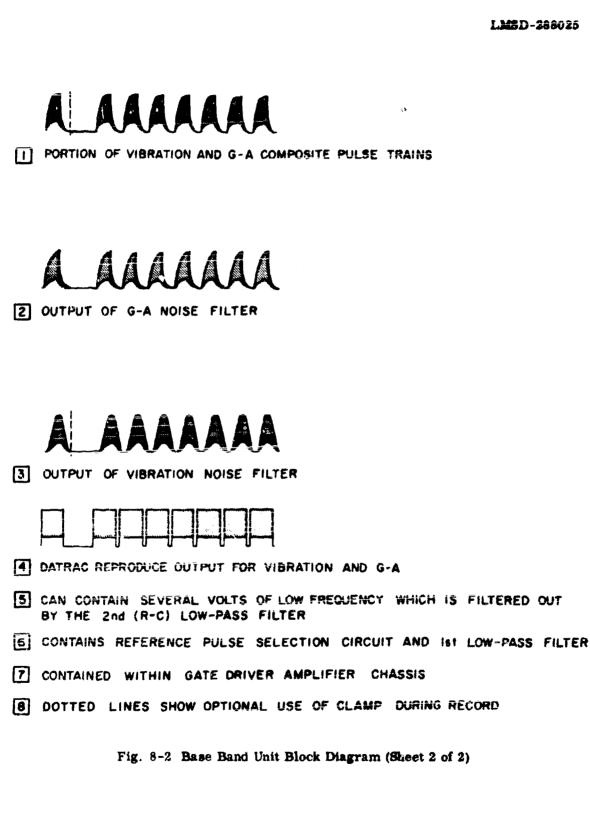

| 8-2    | Base Band Unit Block Diagram (Sheet 1 of 2)                   | 8-8    |

| 8-2    | Base Band Unit Block Diagram (Sheet 2 of 2)                   | 8-9    |

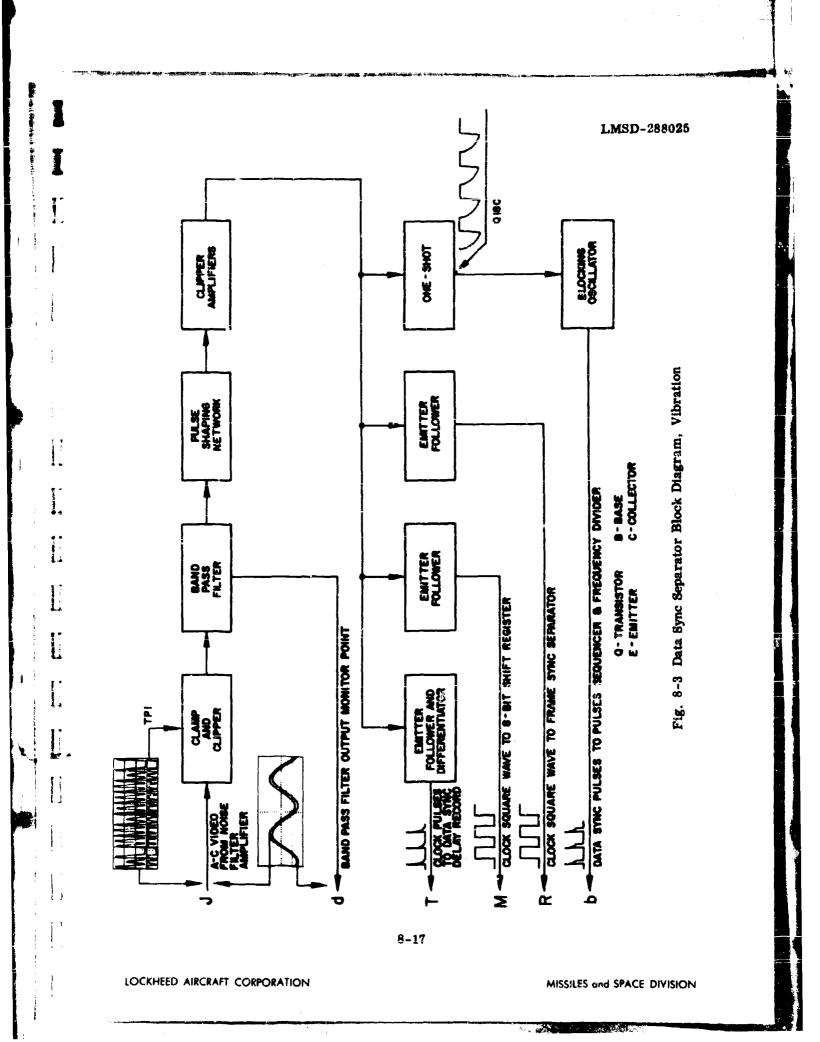

| 8-3    | Data Sync Separator Block Diagram, Vibration                  | 8-17   |

| 8-4    | Data Sync Separator Block Diagram, G-A                        | 8-18   |

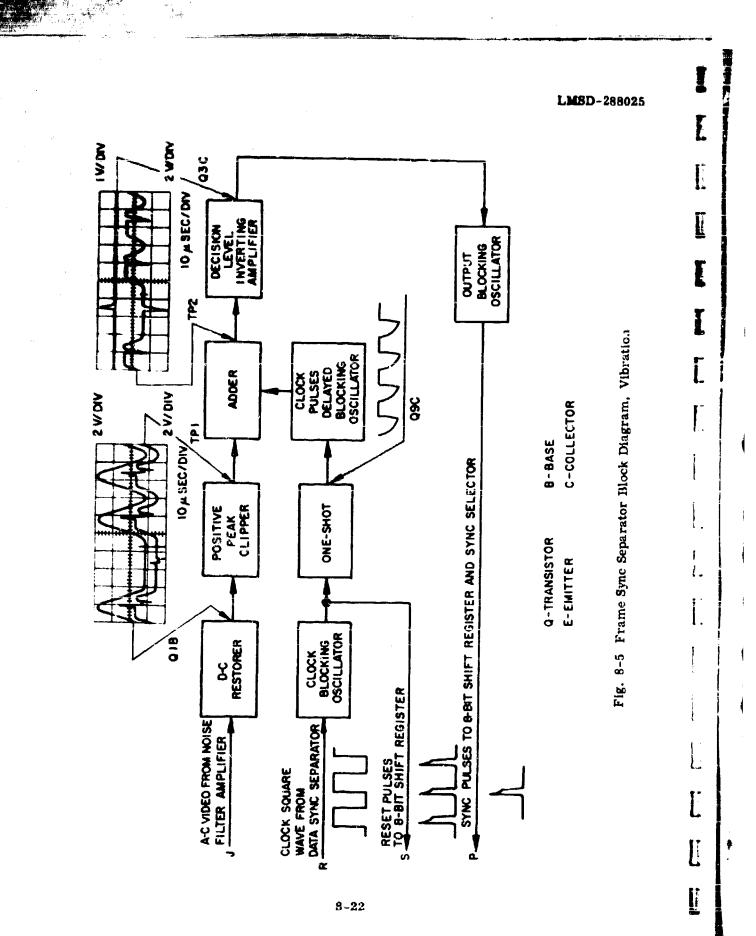

| 8-5    | Frame Sync Separator Block Diagram, Vibration                 | 8-22   |

Revised 25 June 1960

3

1

E

Ŀ

$\Pi$

1

Ľ

G

\$

xiii

LOCKHEED AIRCRAFT CORFORATION

E

[]

Ĩ

| Figure       |                                                   | Page | 1 -        |

|--------------|---------------------------------------------------|------|------------|

| 8-6          | Frame Sync Separator Block Diagram, G-A           | 8-23 | 1 1        |

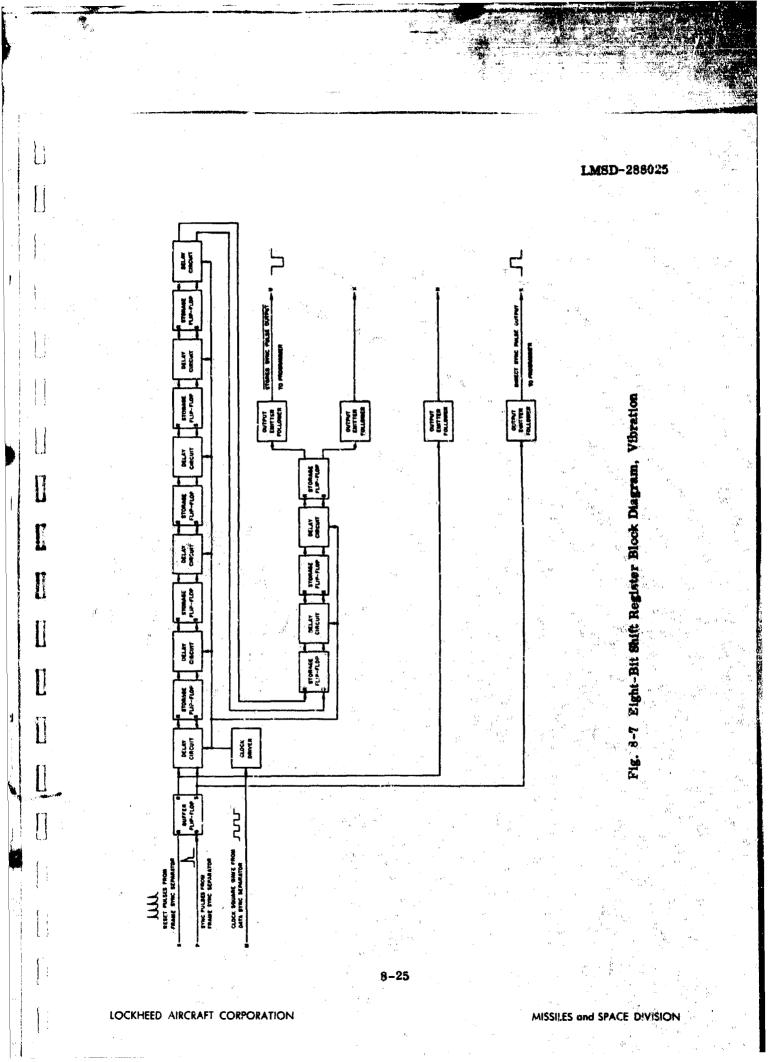

| 8-7          | Eight-Bit Shift Register Block Diagram, Vibration | 8-25 |            |

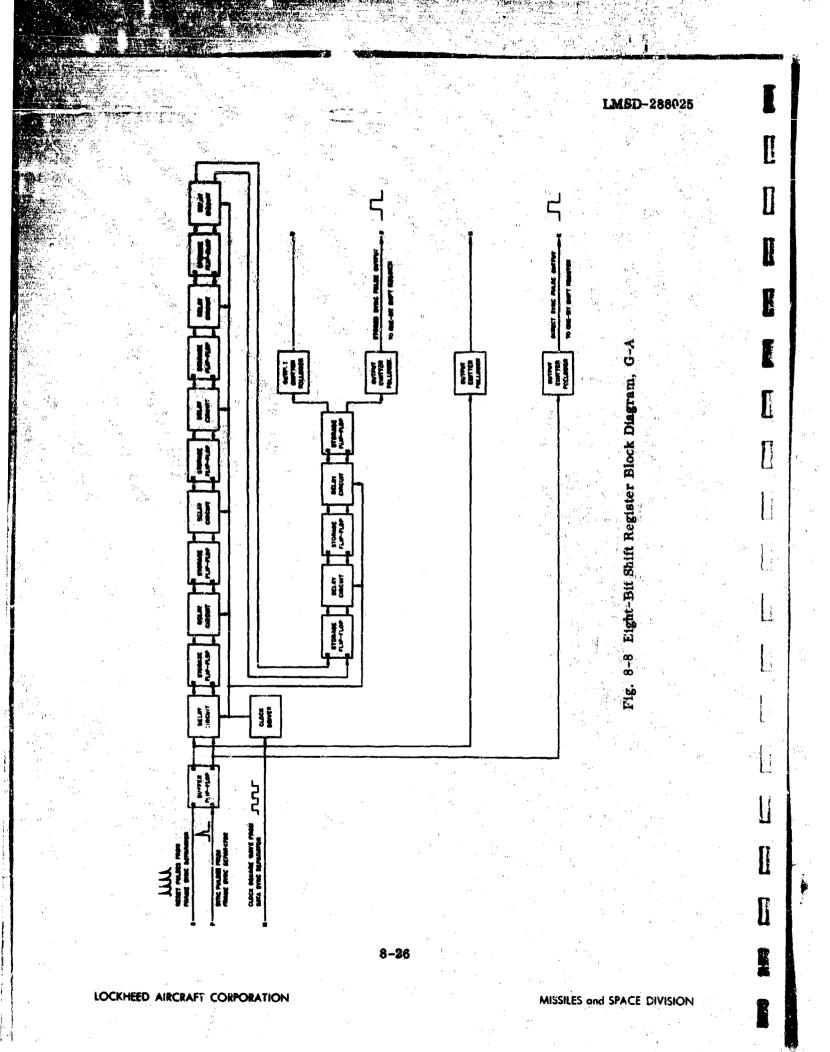

| <b>3-8</b>   | Eight-Bit Shift Register Block Diagram, G-A       | 8-26 |            |

| 8-9          | One-Bit Shift Register Block Diagram              | 8-29 |            |

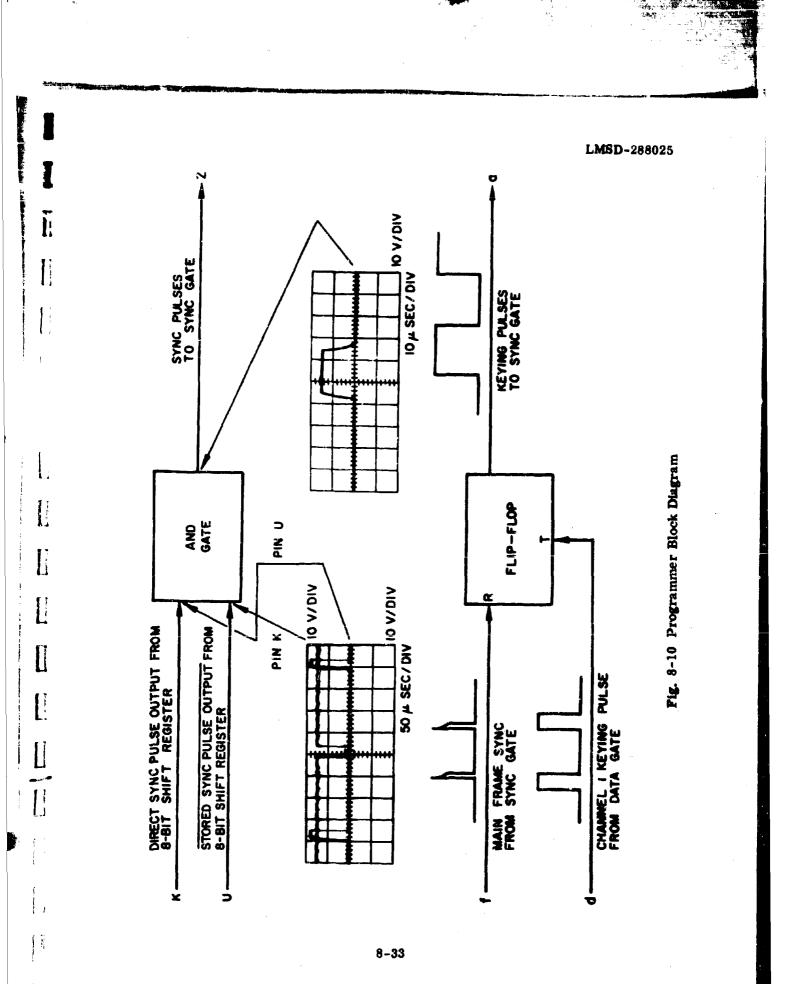

| 8-10         | Programmer Block Diagram                          | 8-33 | L.J        |

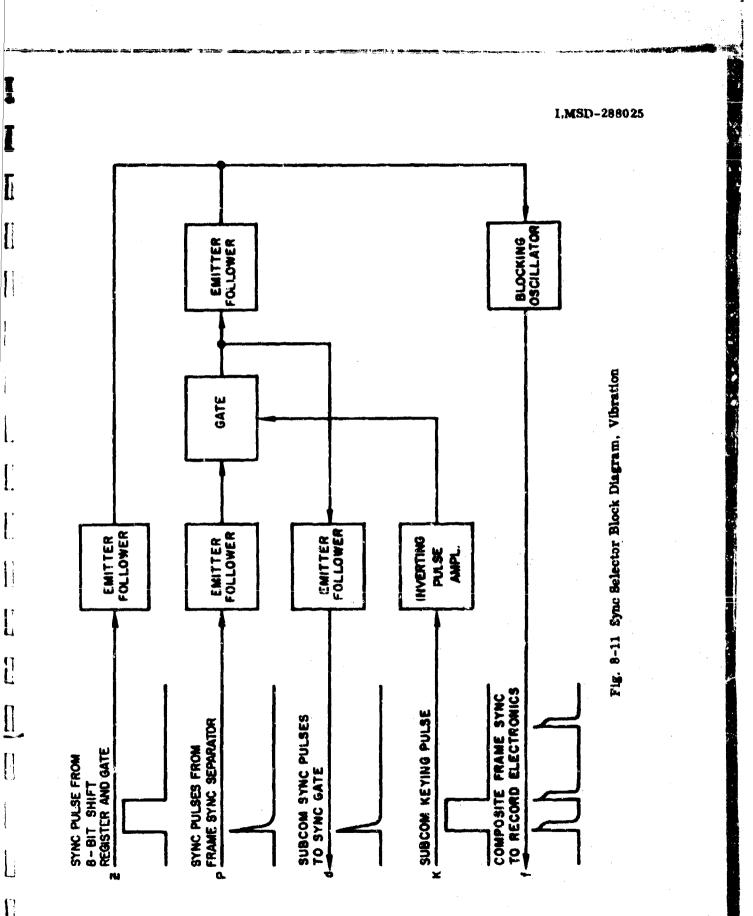

| 8-11         | Sync Selector Block Diagram, Vibration            | 8-35 | E          |

| 8-12         | Sync Selector Block Diagram, G-A                  | 8-36 | نا         |

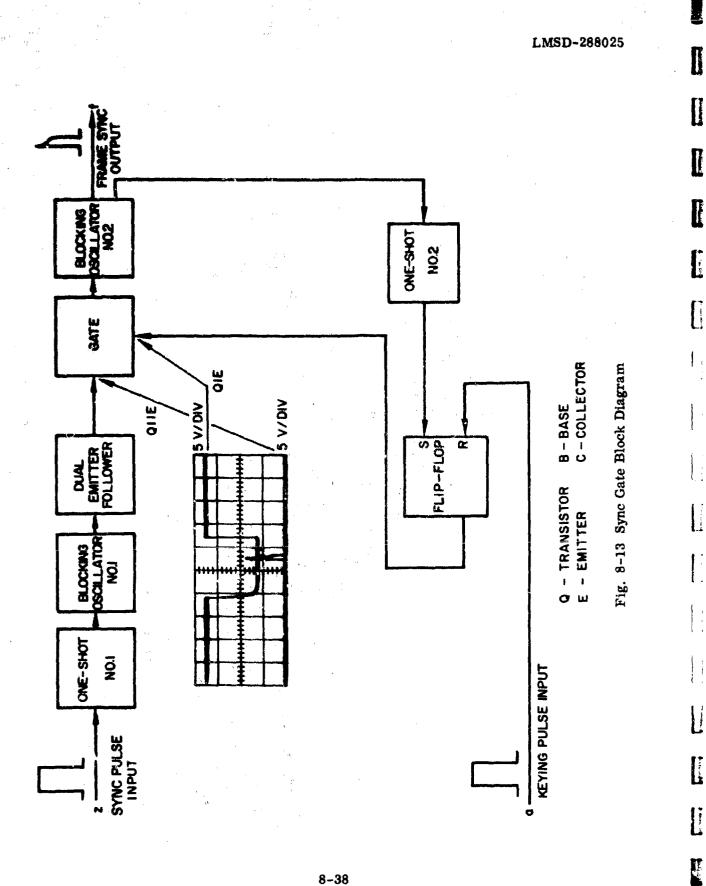

| 8-13         | Sync Gate Block Diagram                           | 8-38 | r          |

| 8-14         | Zero Data Selector Block Diagram                  | 8-41 | Li         |

| 8-15         | Frequency Divider Block Diagram                   | 8-43 | r -        |

| 8-1 <b>6</b> | Eight-Channel Pulse Sequencer Block Dizgram       | 8-45 | Ì          |

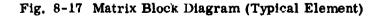

| 8-17         | Matrix Block Diagram (Typical Element)            | 8-49 |            |

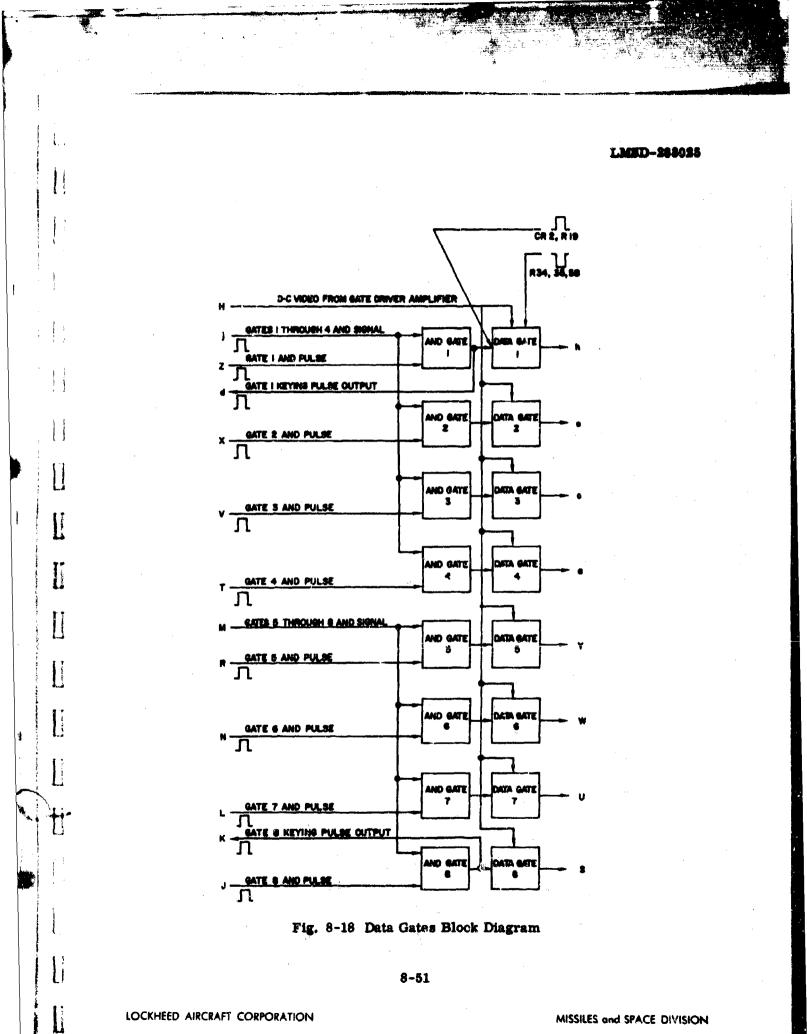

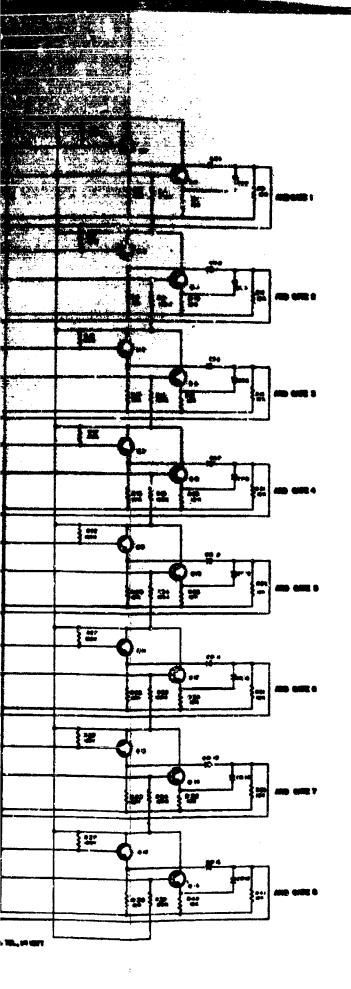

| 8-18         | Data Gates Block Diagram                          | 8-51 | 1          |

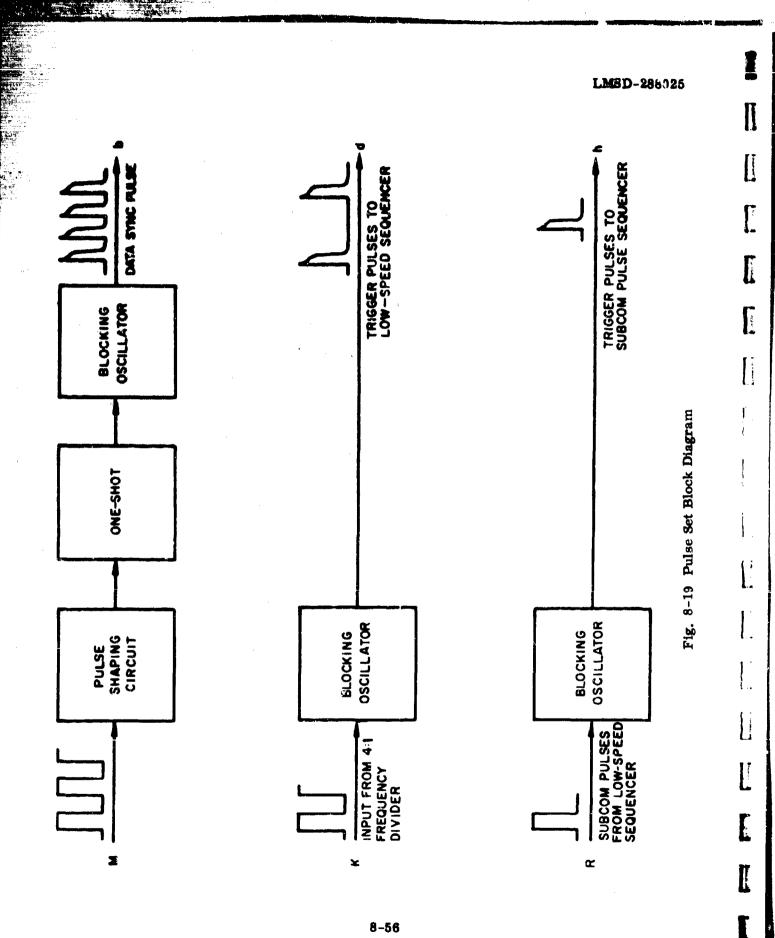

| 8-19         | Pulse Set Block Diagram                           | 8-56 |            |

| 8-20         | Duty Cycle II Block Diagram                       | 8-58 |            |

| 8-21         | Data Sync Delay Record Block Diagram              | 8-60 | ŗ          |

| 8-22         | Sample and Hold Block Diagram                     | 8-62 | 1          |

| 8-23         | DC Reference Filter Block Diagram                 | 8-64 | L          |

| 8-24         | Frame Sync Storage Record Block Diagram           | 8-68 | f-         |

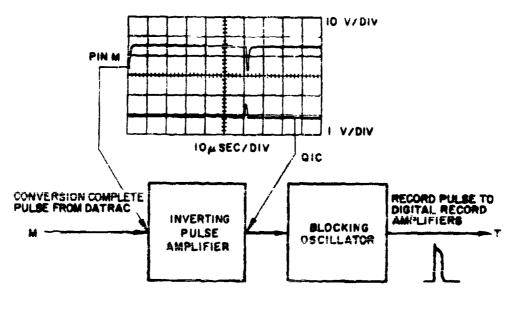

| 8-25         | Pulse Amplifier Block Diagram                     | 8-69 | E          |

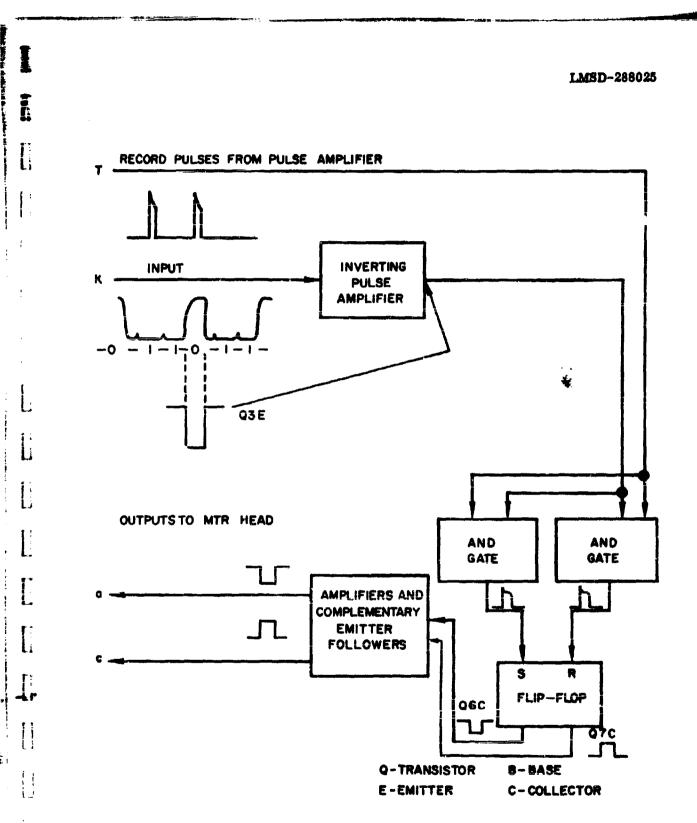

| 8-28         | Digital Record Amplifier Block Diagram            | 8-71 | <i>.</i> . |

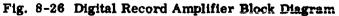

| 8-27         | Digital Reproduce Amplifier Block Diagram         | 8-74 | -          |

| 8-28         | Data Storage and Gate Block Diagram               | 8-77 | •          |

| 8-29         | Data Sync Delay Reproduce Block Diagram           | 8-79 | ₹.         |

| 8-30         | Delay Command Pulse Block Diagram                 | 8-81 | \$         |

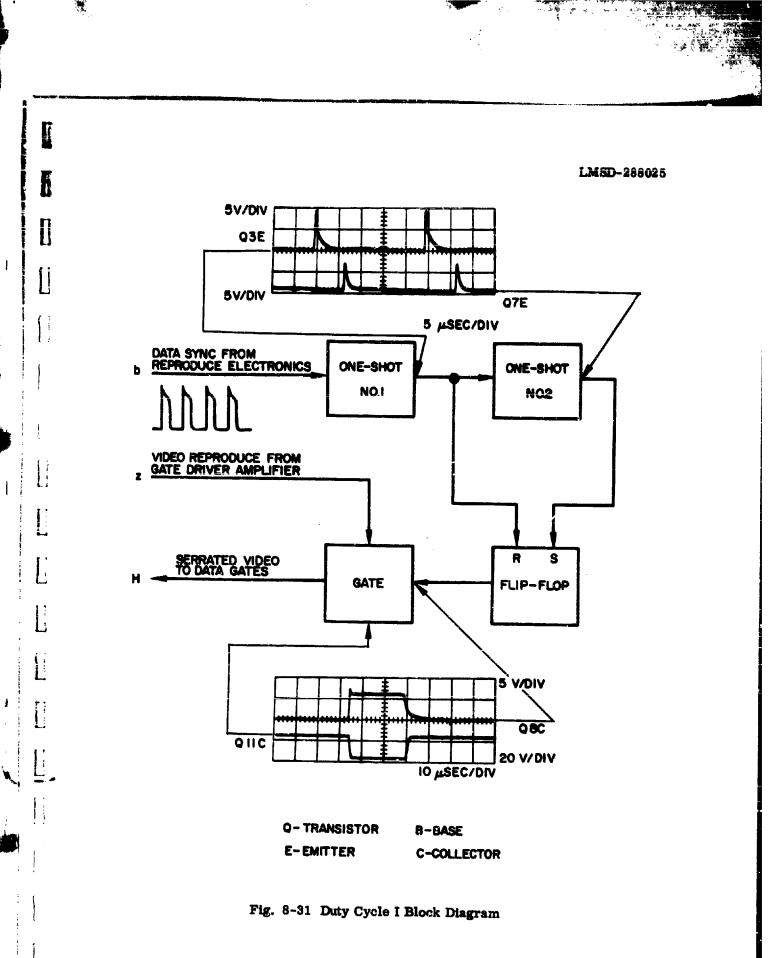

| 8-31         | Duty Cycle I Block Diagram                        | 8-83 |            |

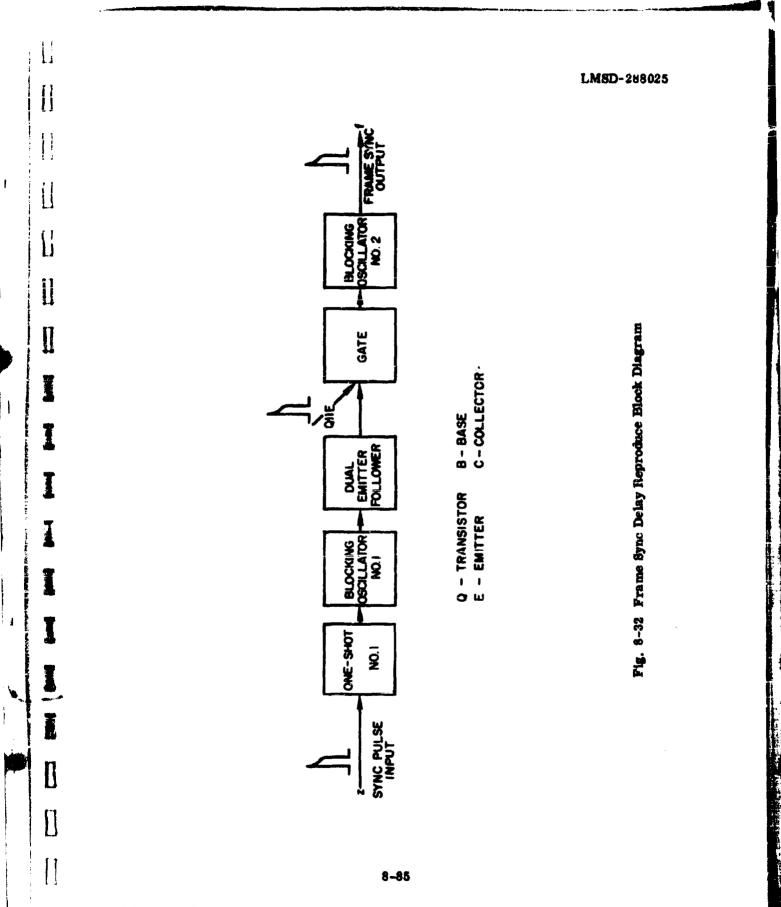

| 8-32         | Frame Sync Delay Reproduce Block Diagram          | 8-85 |            |

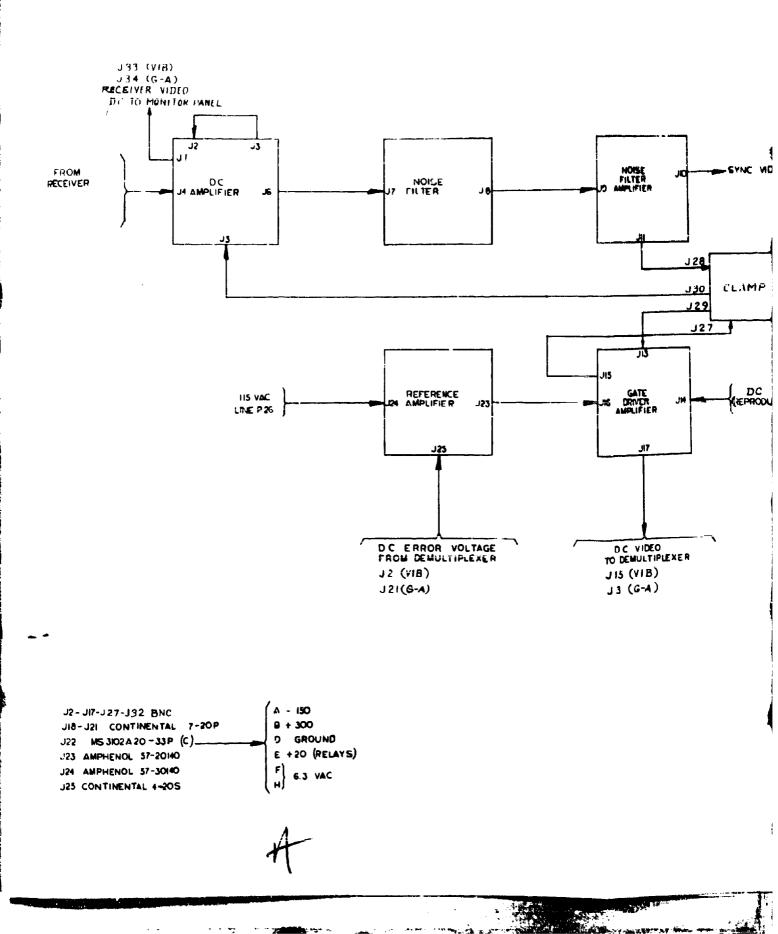

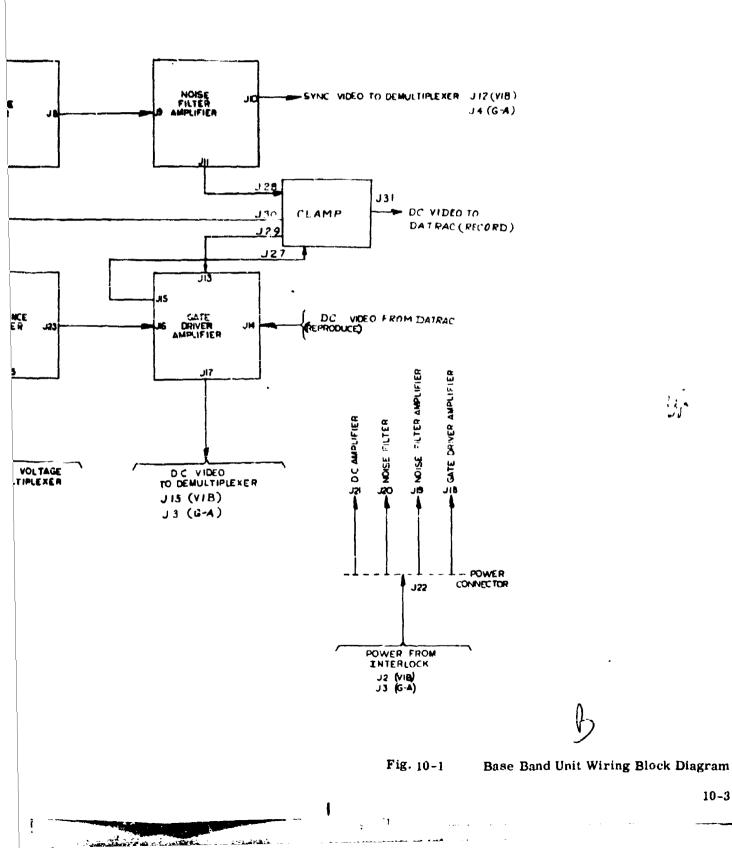

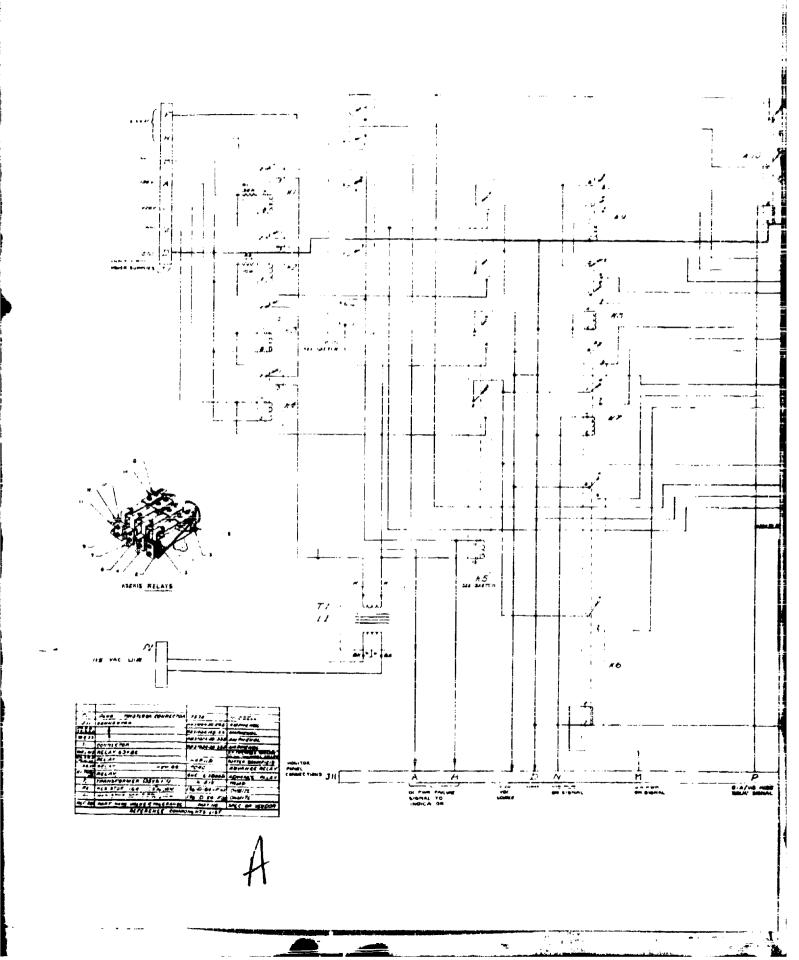

| 10-1         | Base Band Unit Wiring Block Diagram               | 10-3 | r.         |

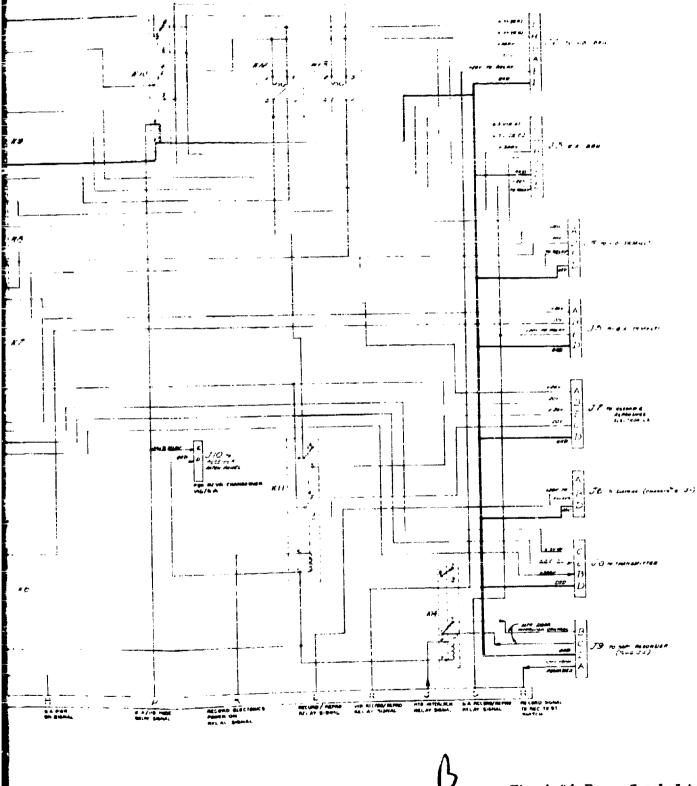

| 10-2         | Vibration Demultiplexer Wiring Block Diagram -    | 10-5 | E          |

|              | Record and Reproduce                              |      | 67         |

| 10-3         | (Not used. Replaced by new Fig. 10-2, page 10-5.) | 10-7 | Ľ          |

Revised 25 June 1960

xiv

LOCKHEED AIRCRAFT CORPORATION

| Figure       |                                                                           | Page         |

|--------------|---------------------------------------------------------------------------|--------------|

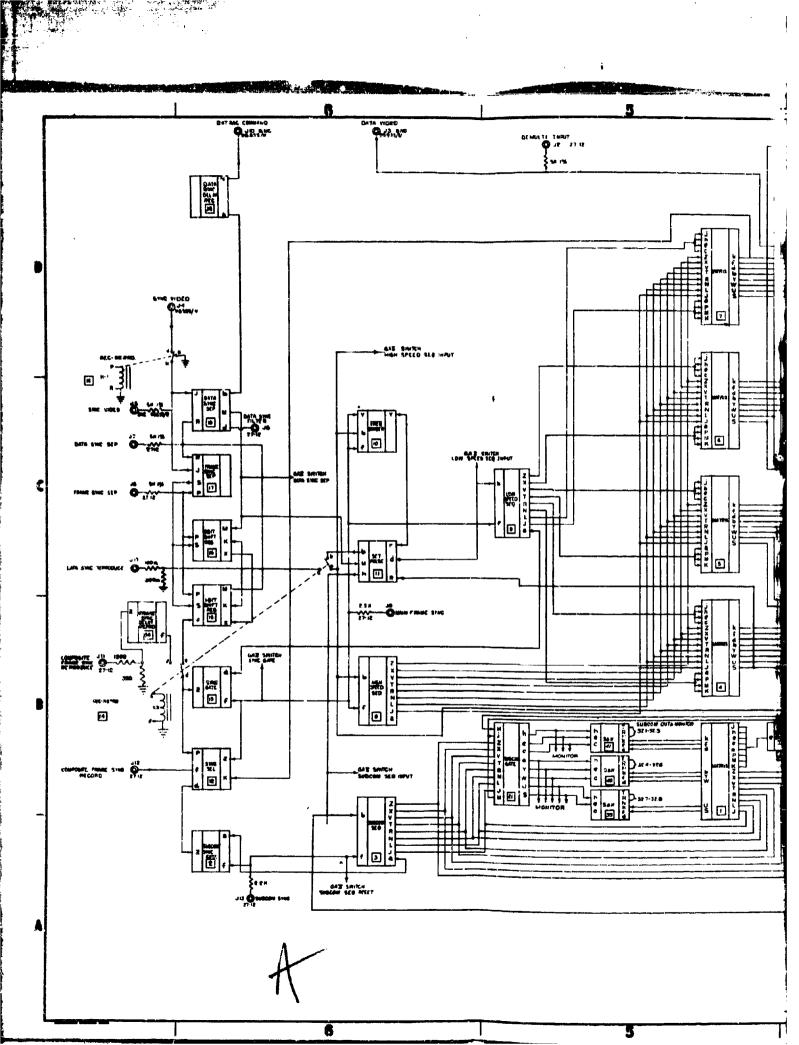

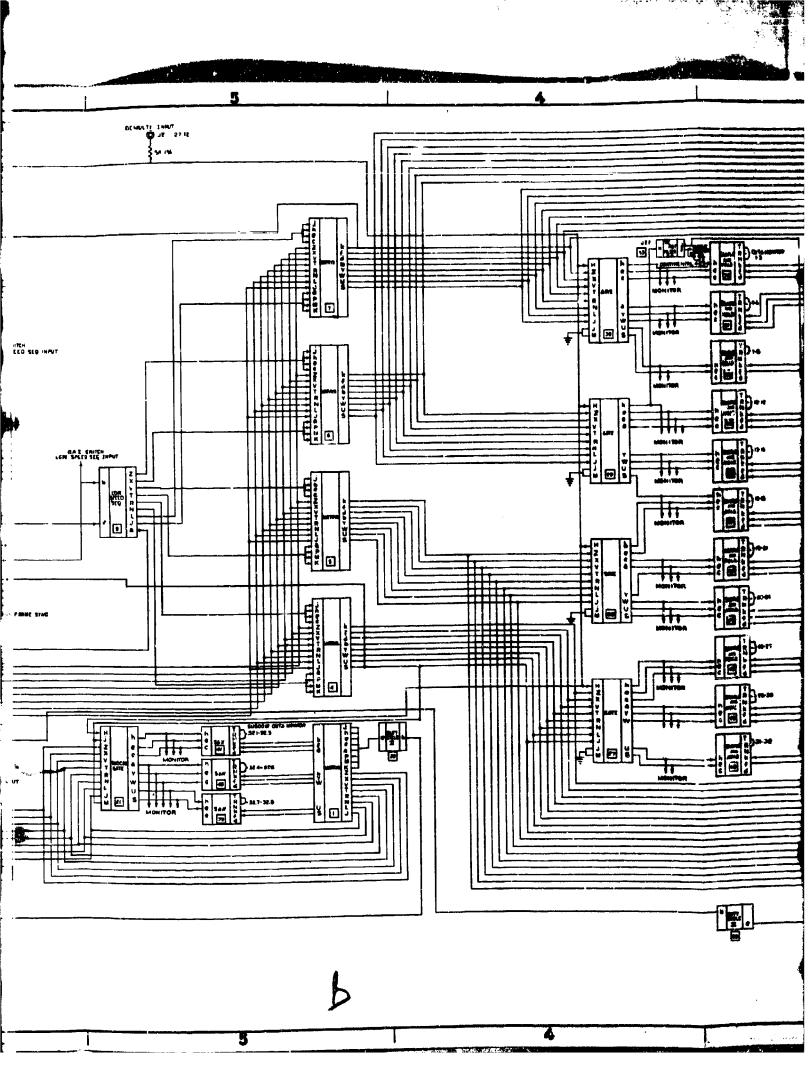

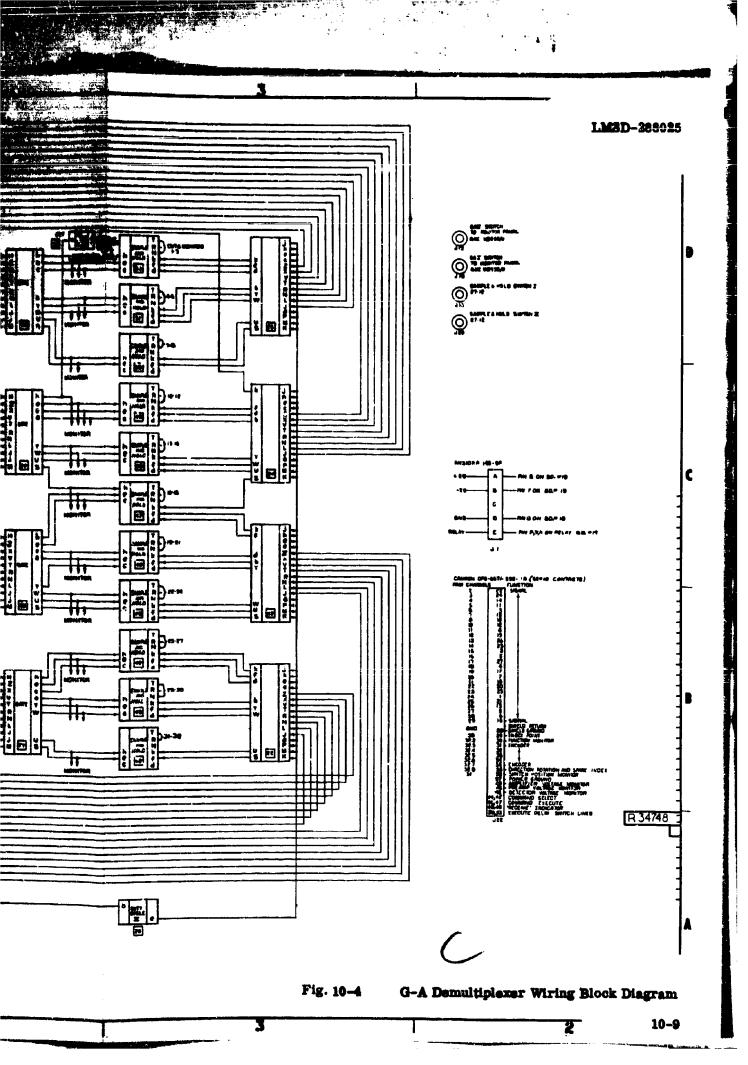

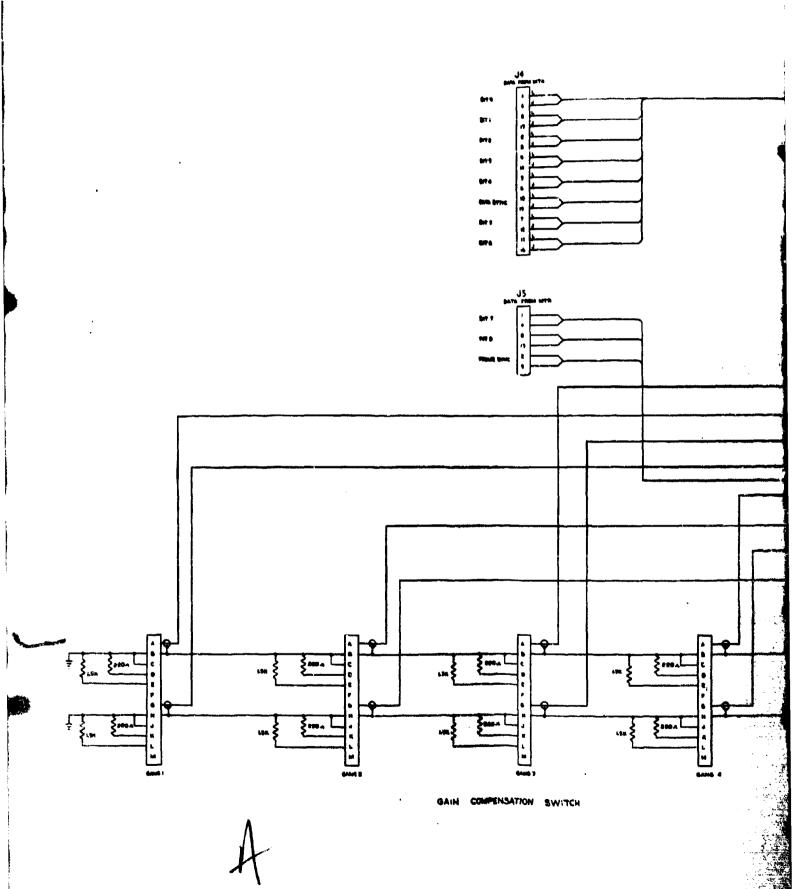

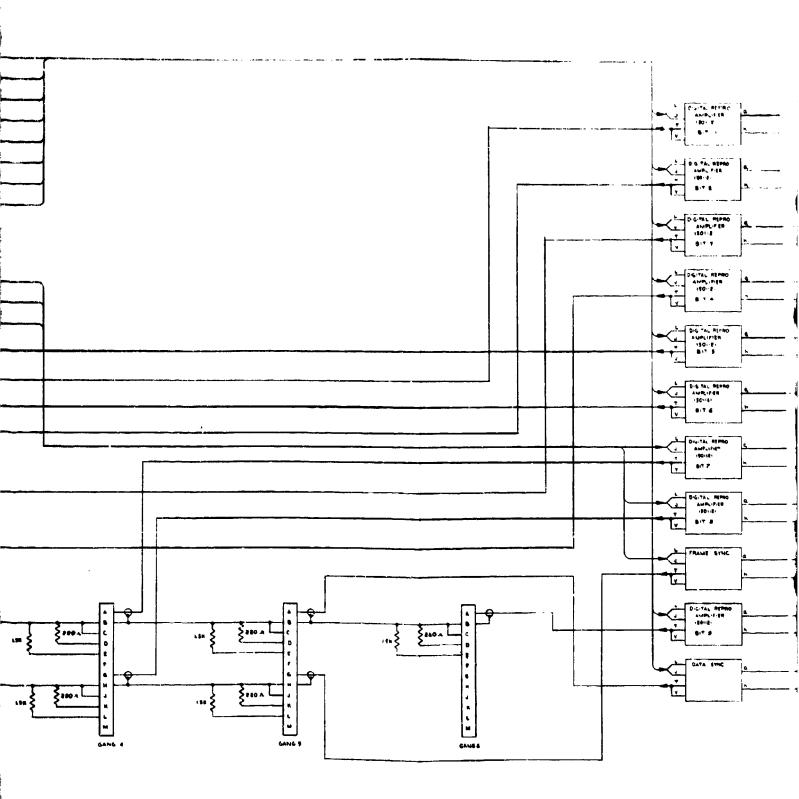

| 10-4         | G-A Demultiplexer Wiring Block Diagram                                    | 10-9         |

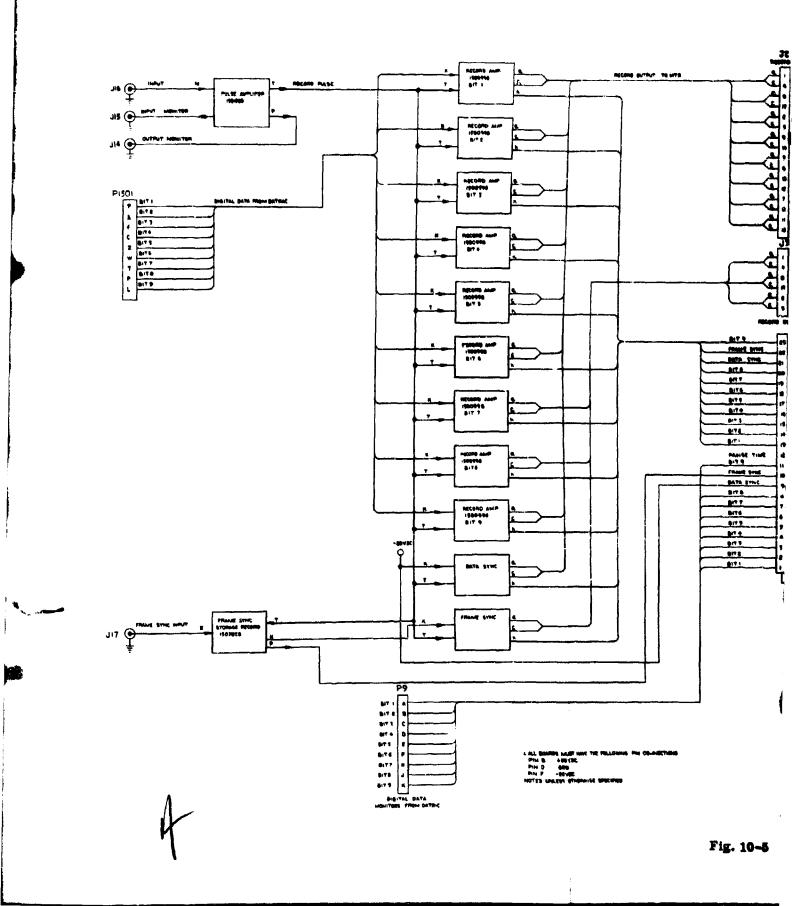

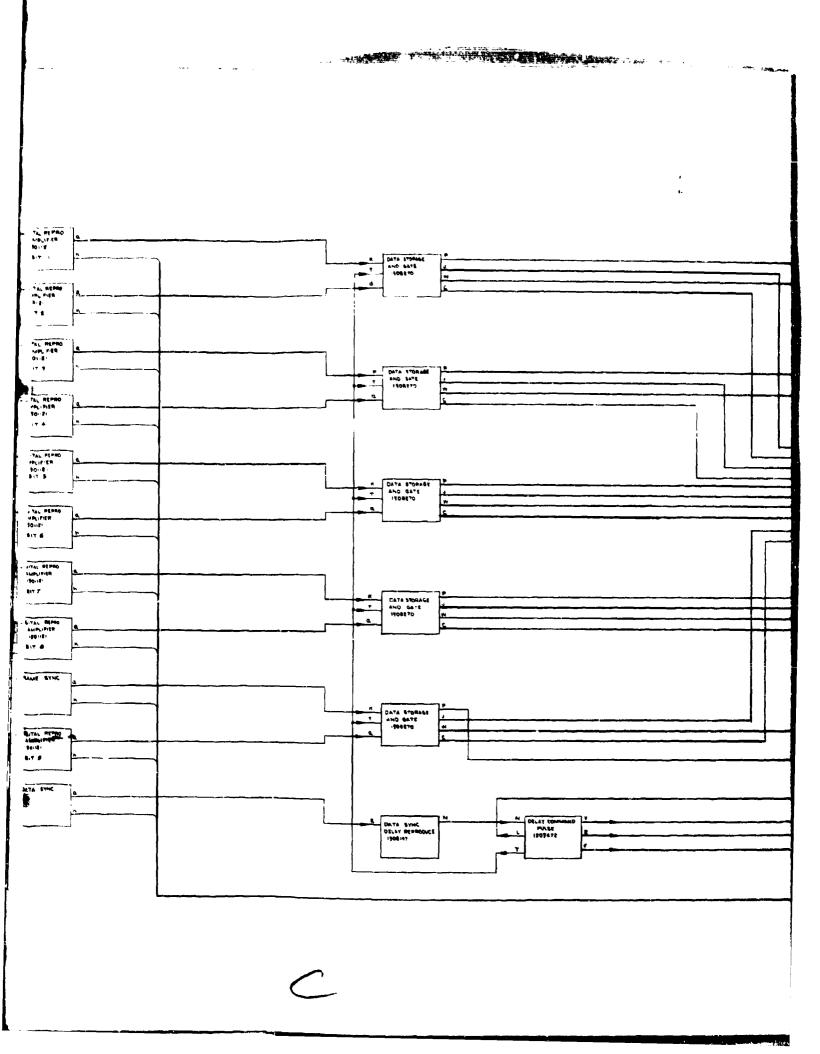

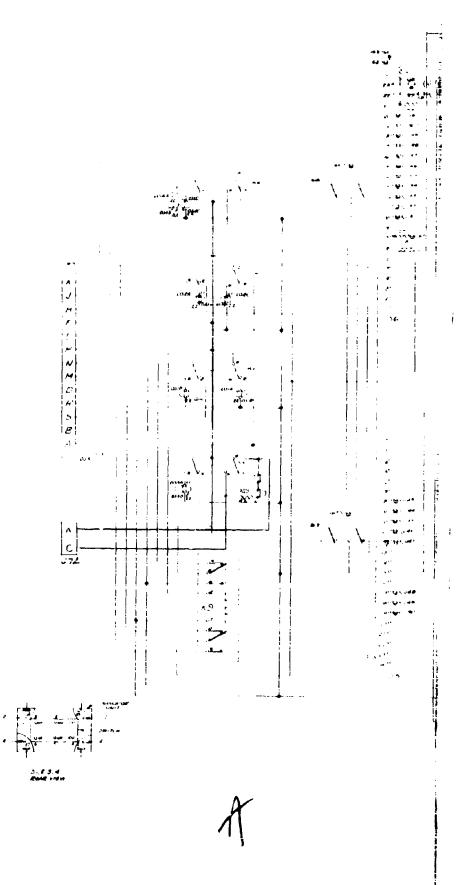

| 10-5         | Digital Record Electronics Wiring Block Diagram                           | 10-11        |

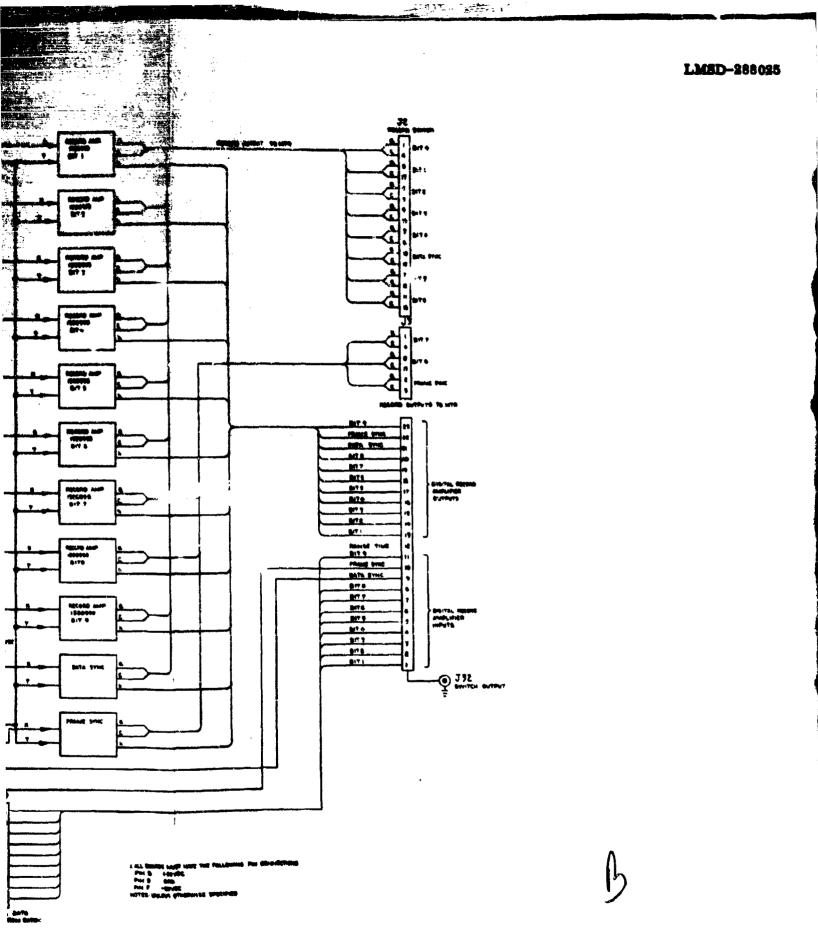

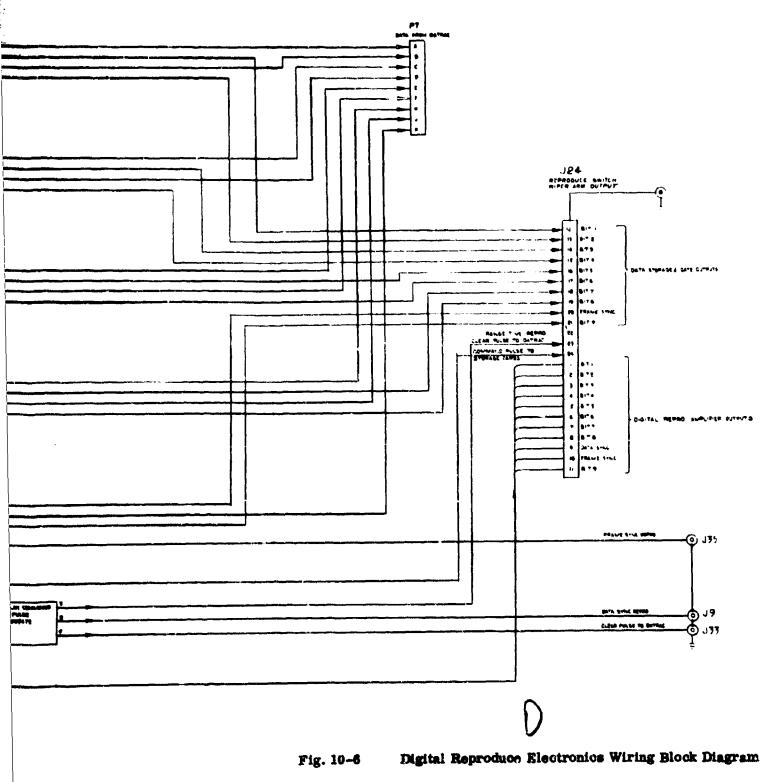

| 10-6         | Digital Reproduce Electronics Wiring Block Diagram                        | 10-13        |

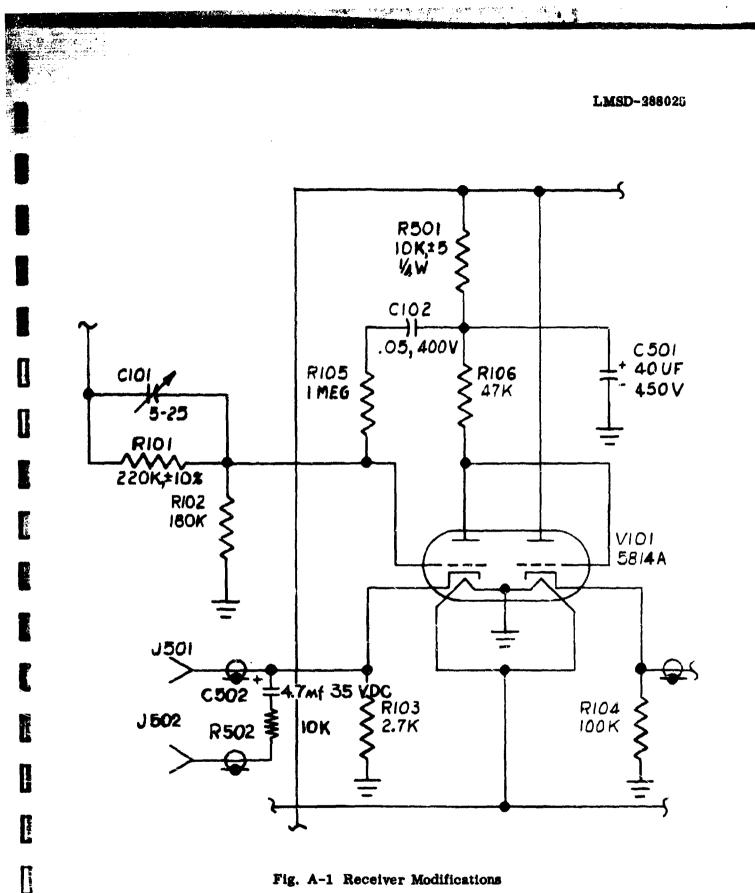

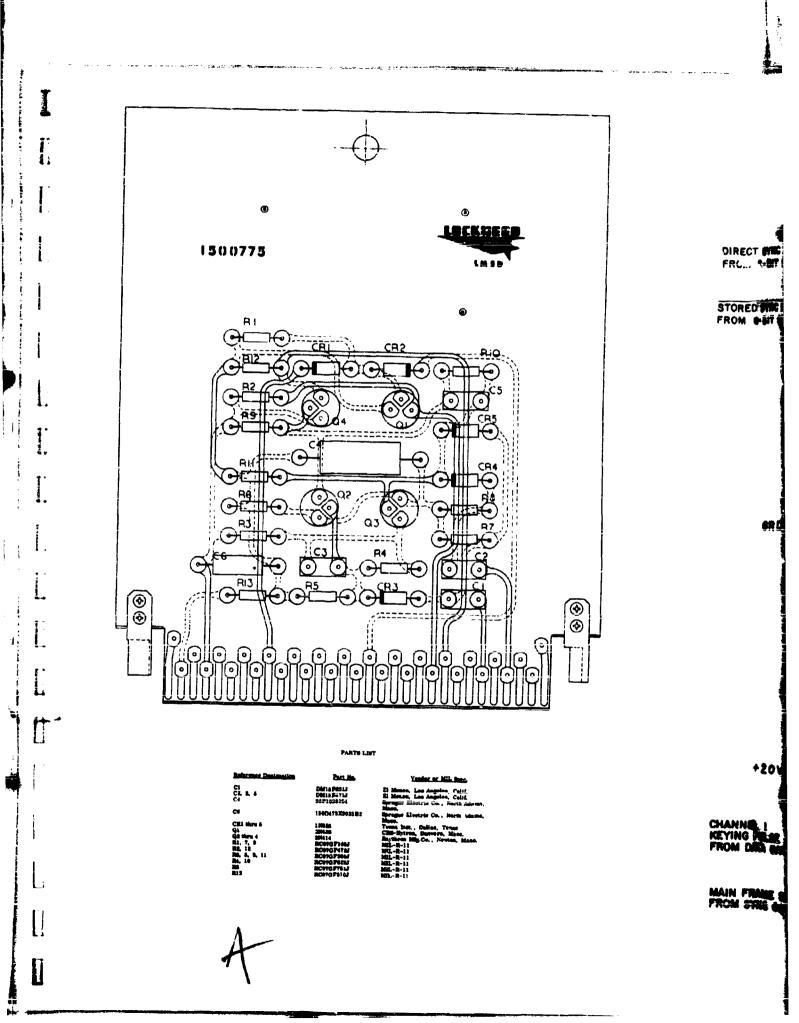

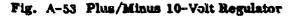

| <b>A-</b> 1  | Receiver Modifications                                                    | <b>A-1</b>   |

| A-2          | DC Amplifier                                                              | A-3          |

| <b>A-3</b>   | Noise Filter                                                              | A-5          |

| A-4          | Noise Filter Amplifier                                                    | A-7          |

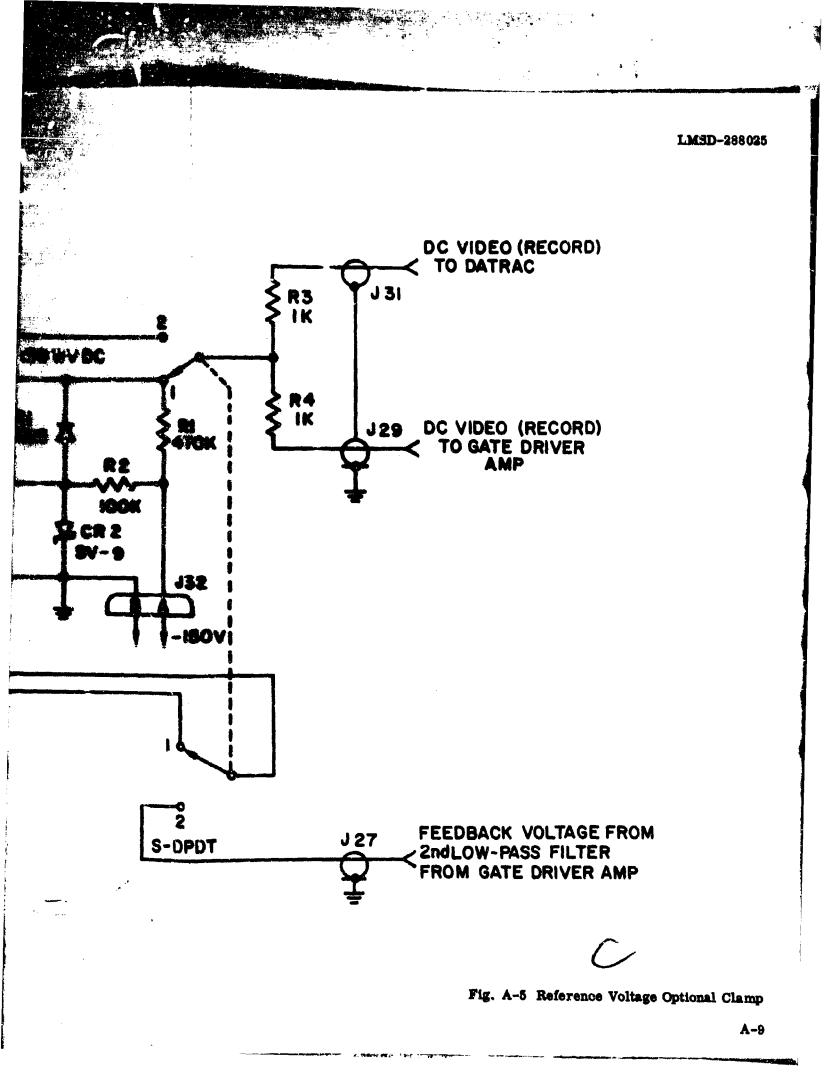

| <b>A-</b> 5  | Reference Voltage Optional Clamp                                          | A-9          |

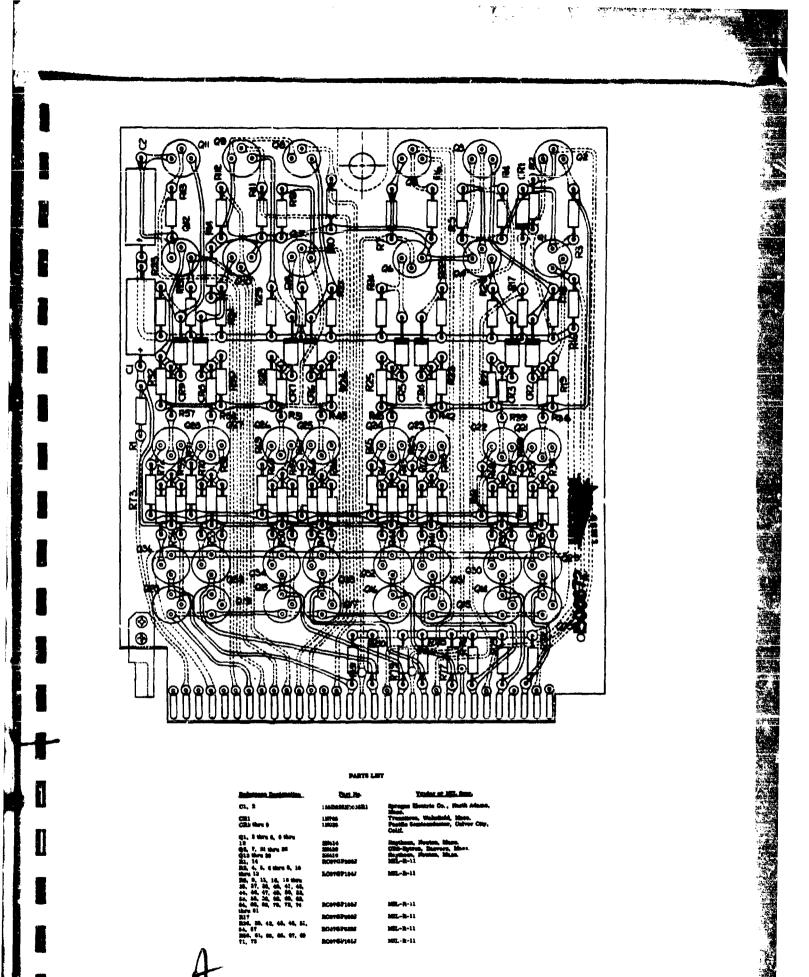

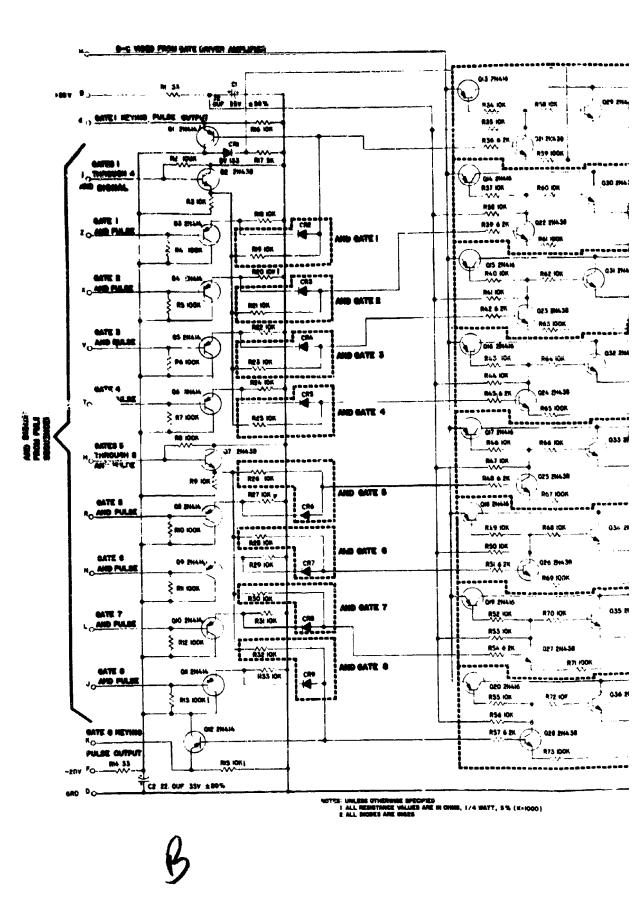

| <b>A-6</b>   | Gate Driver Amplifier                                                     | <b>A-1</b> 1 |

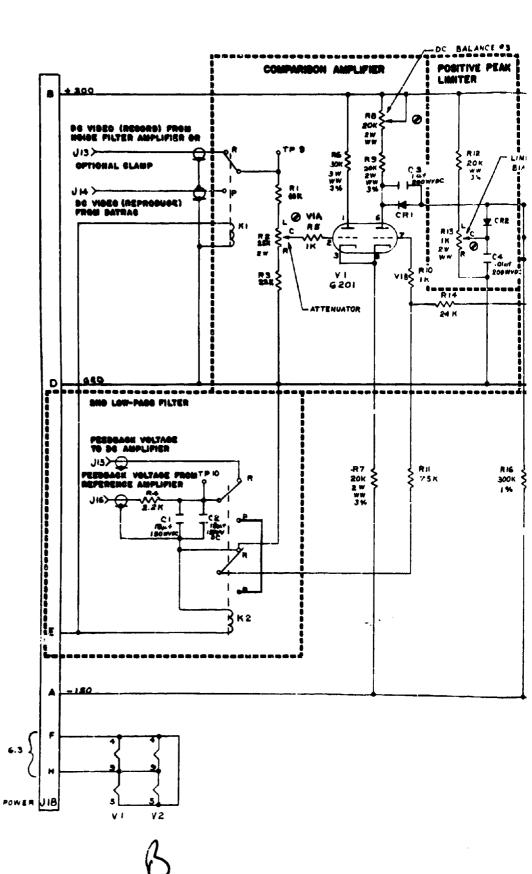

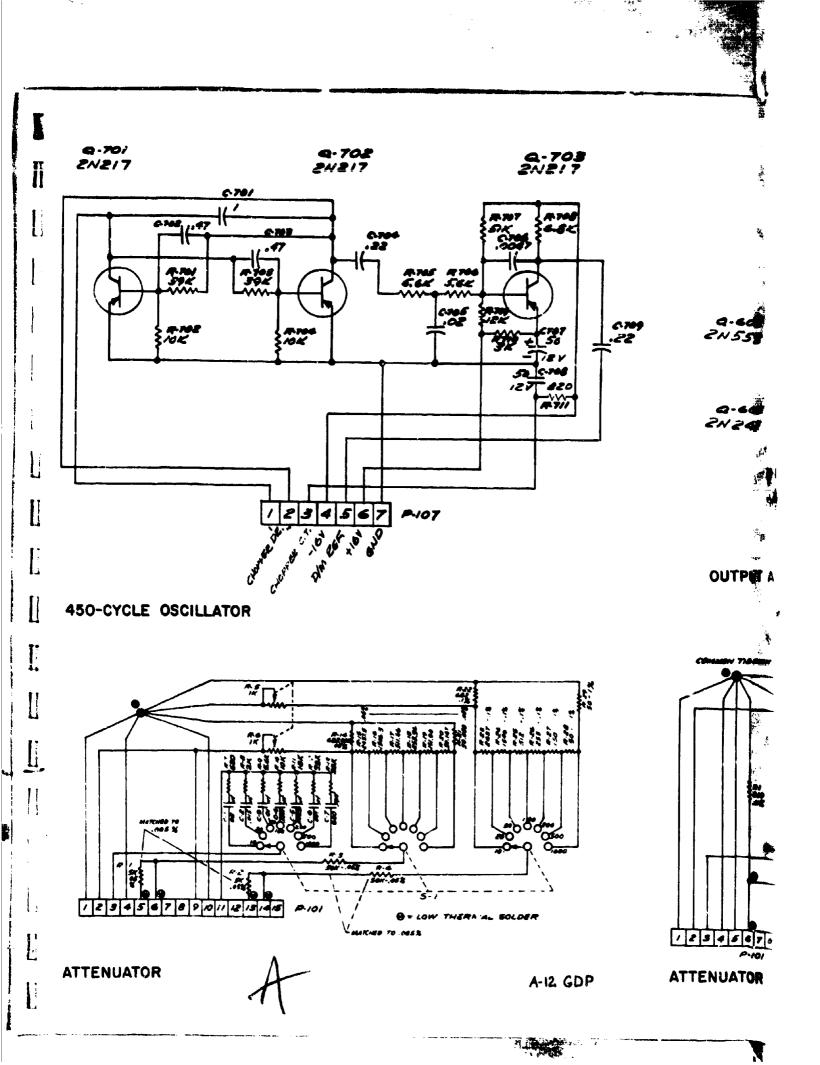

| Å-7          | Reference Amplifier (Sheet 1 of 3)                                        | A-13         |

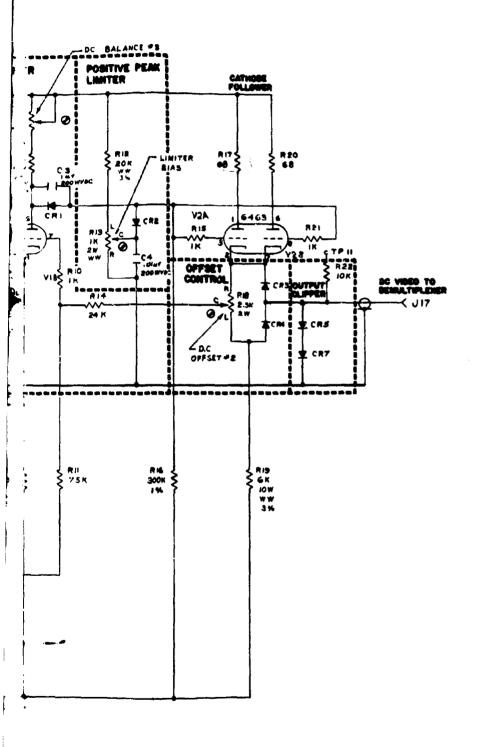

| <b>A-</b> 7  | Reference Amplifier (Sheet 2 of 3)                                        | <b>A-15</b>  |

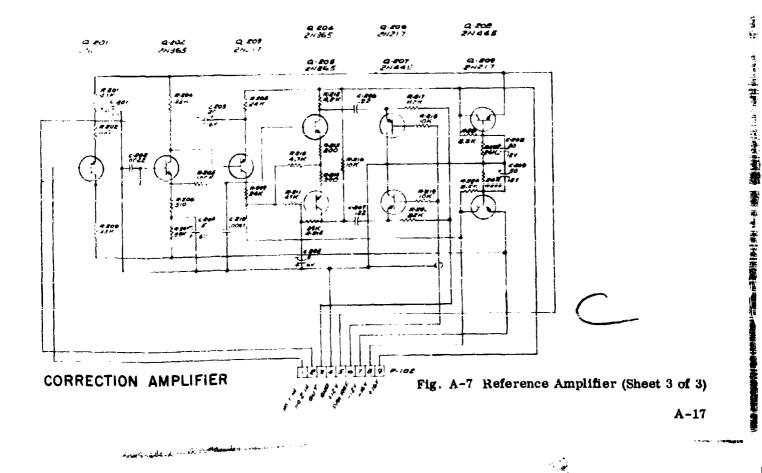

| <b>A-</b> 7  | Reference Amplifier (Sheet 3 of 3)                                        | <b>A</b> -17 |

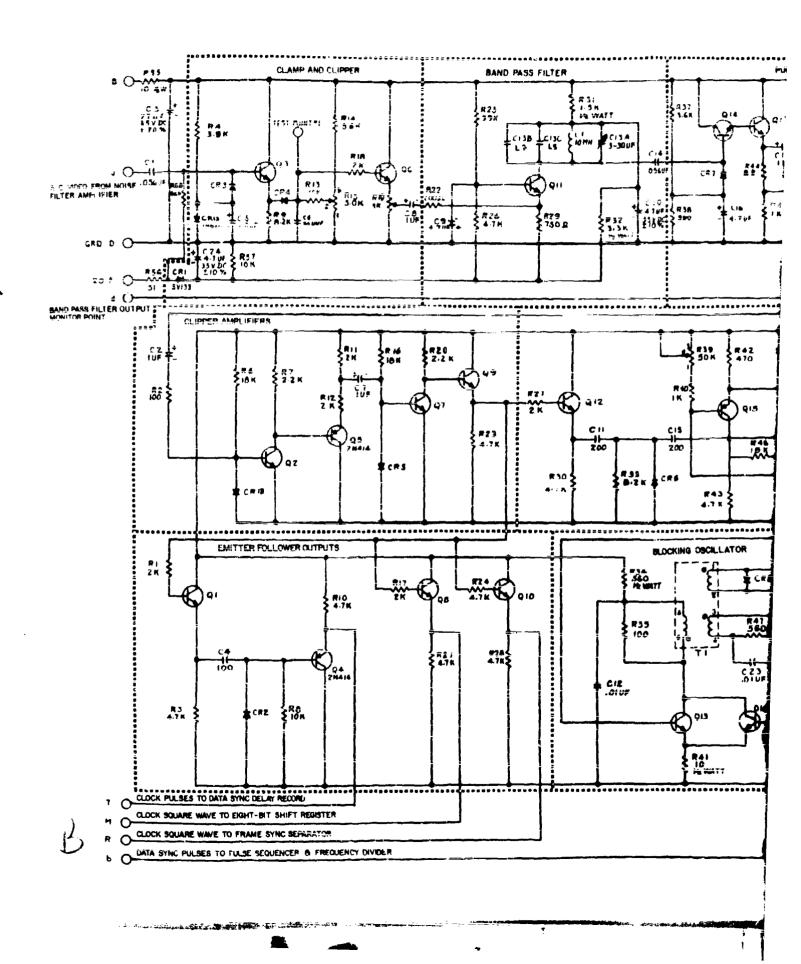

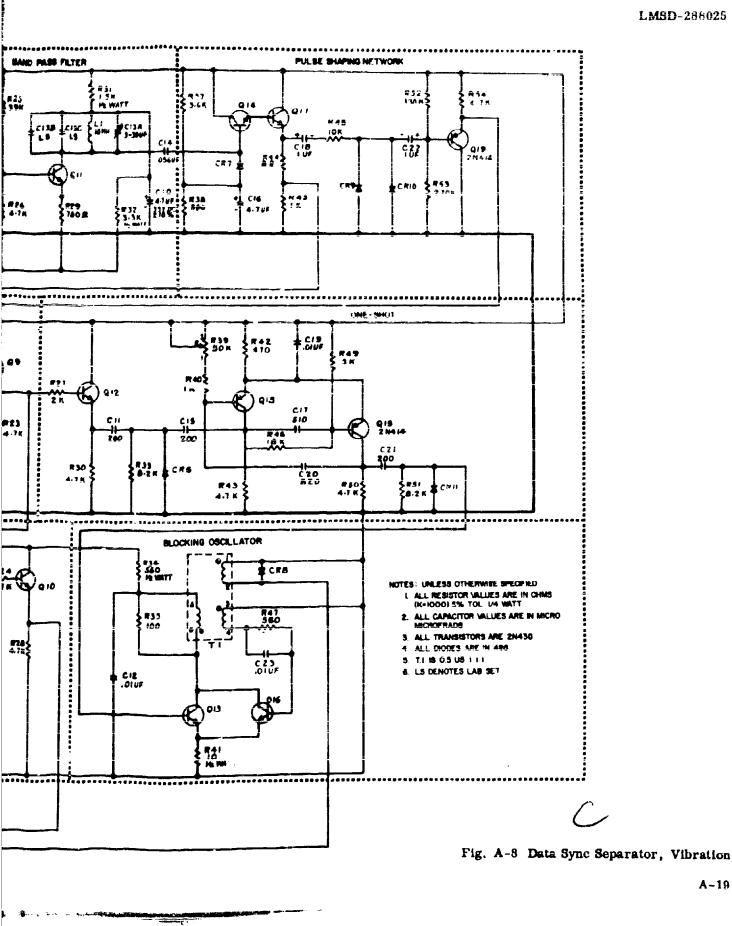

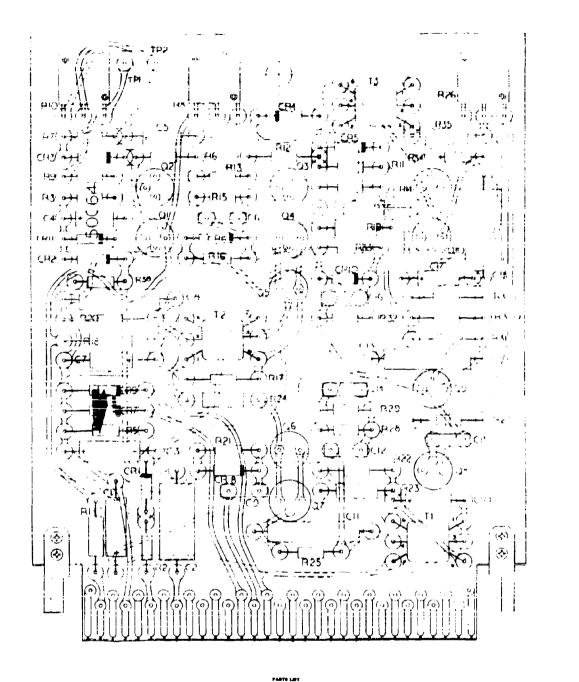

| <b>A-</b> 8  | Data Sync Separator, Vibration                                            | <b>A-19</b>  |

| A-9          | Frame Sync Separator, Vibration                                           | <b>A-2</b> 1 |

| <b>A-10</b>  | Eight-Bit Shift Register, Vibration                                       | A-23         |

| <b>A-11</b>  | Programmer                                                                | <b>A-25</b>  |

| 1-12         | Sync Selector, Vibration                                                  | <b>A-27</b>  |

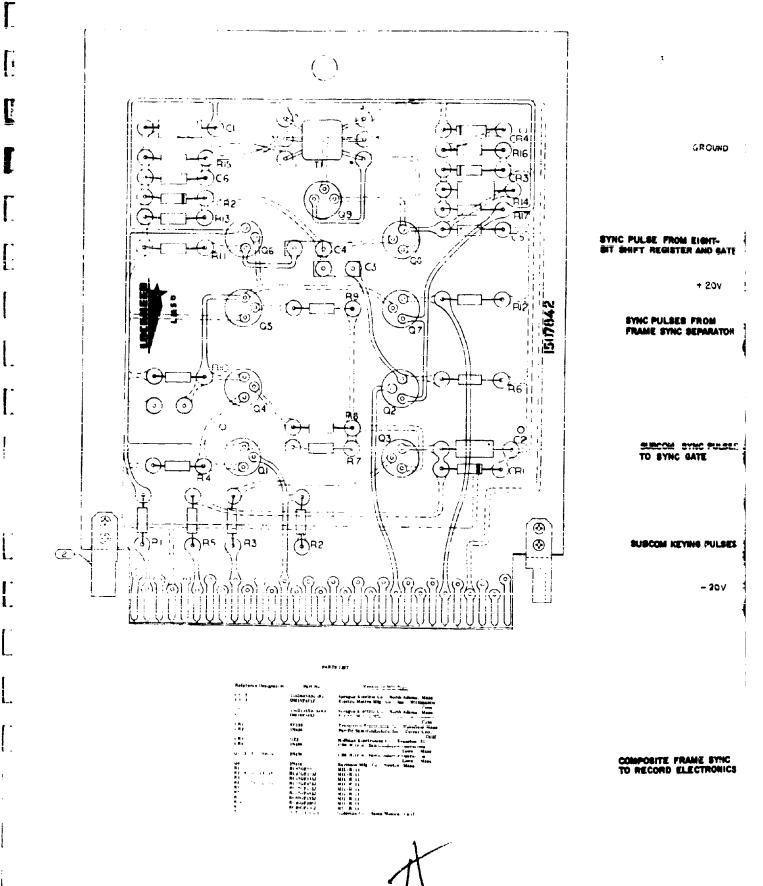

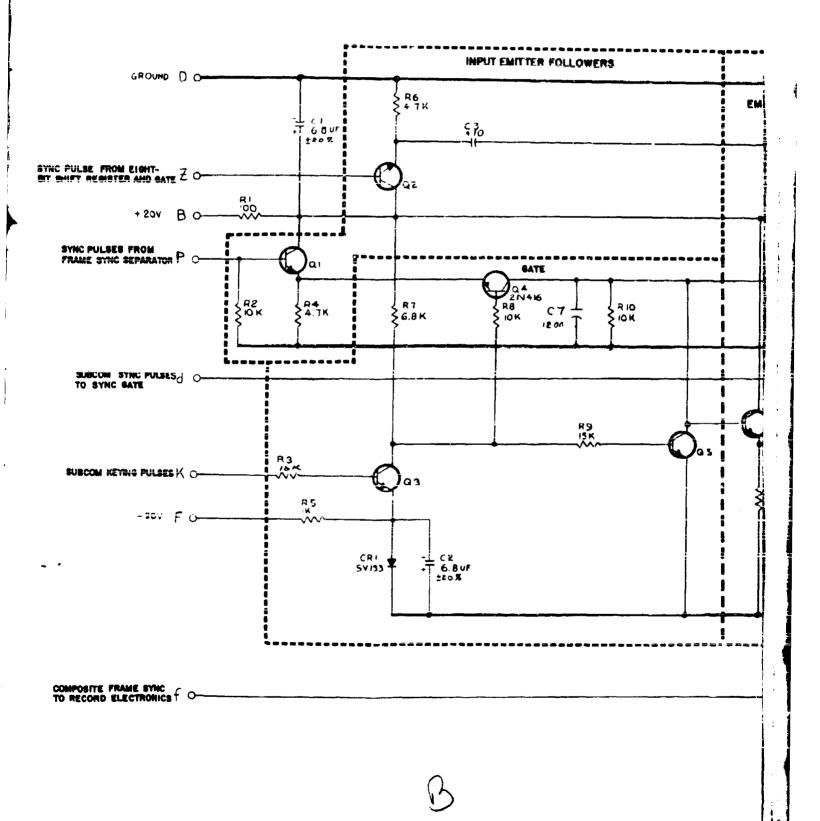

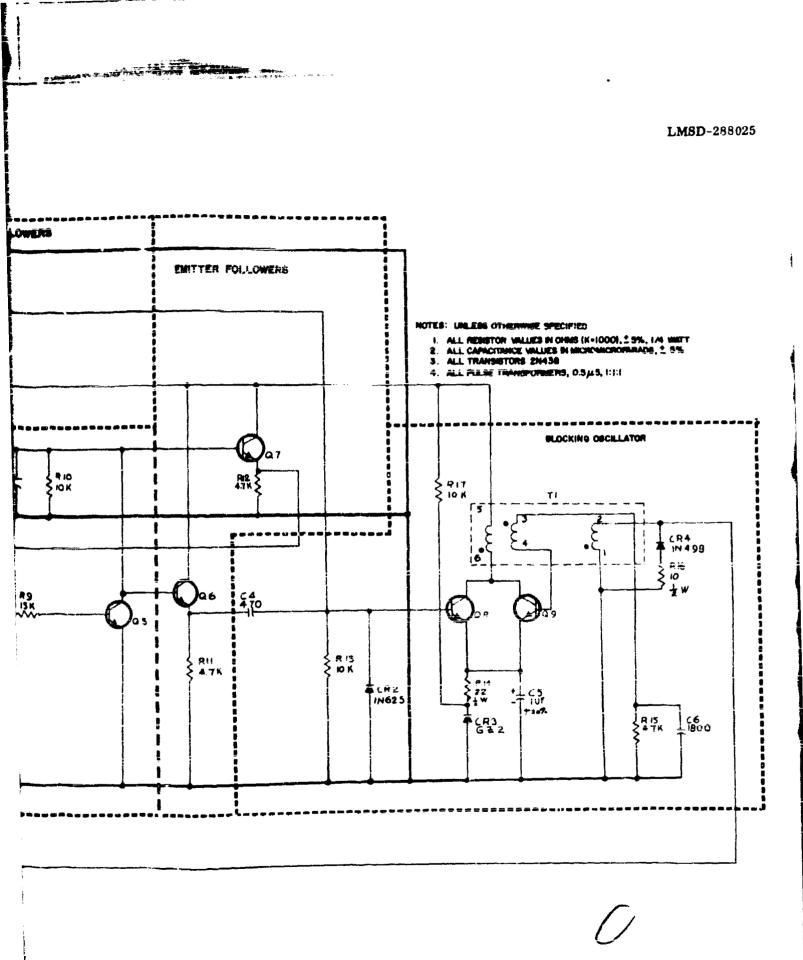

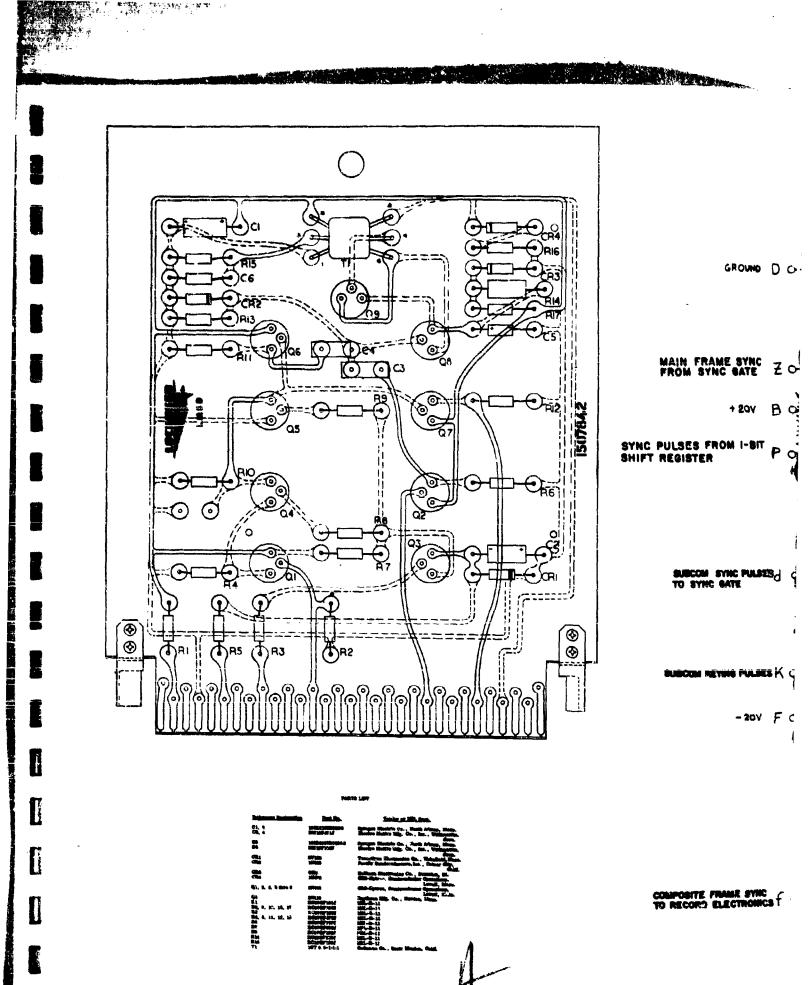

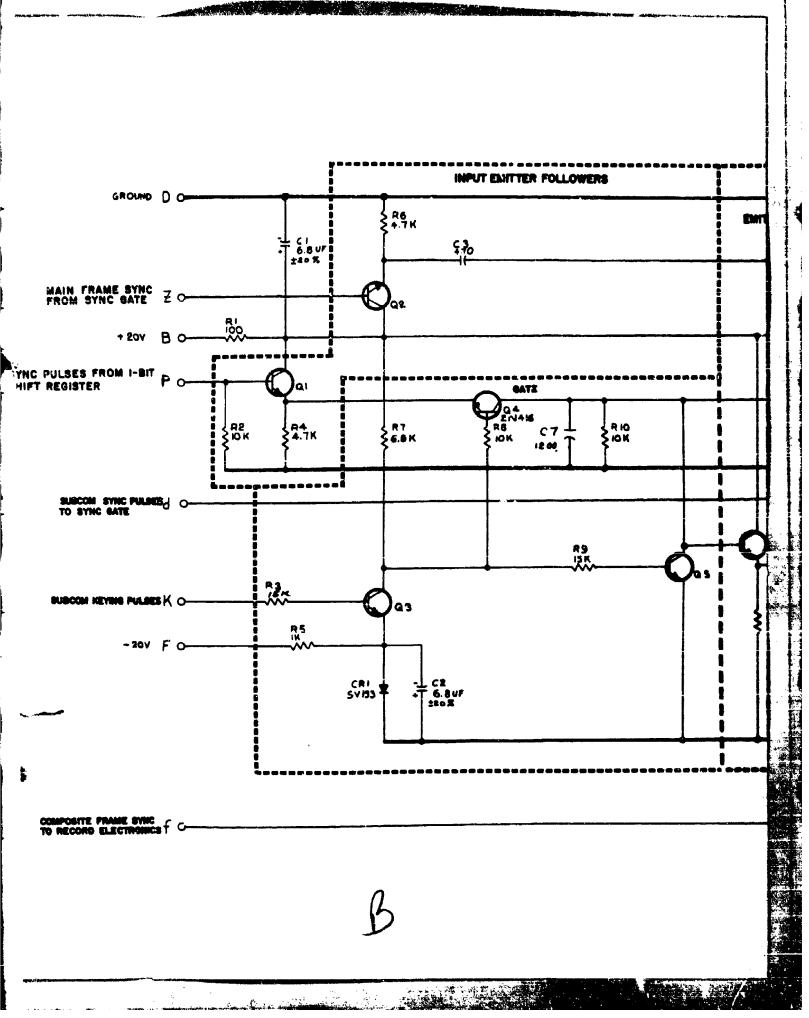

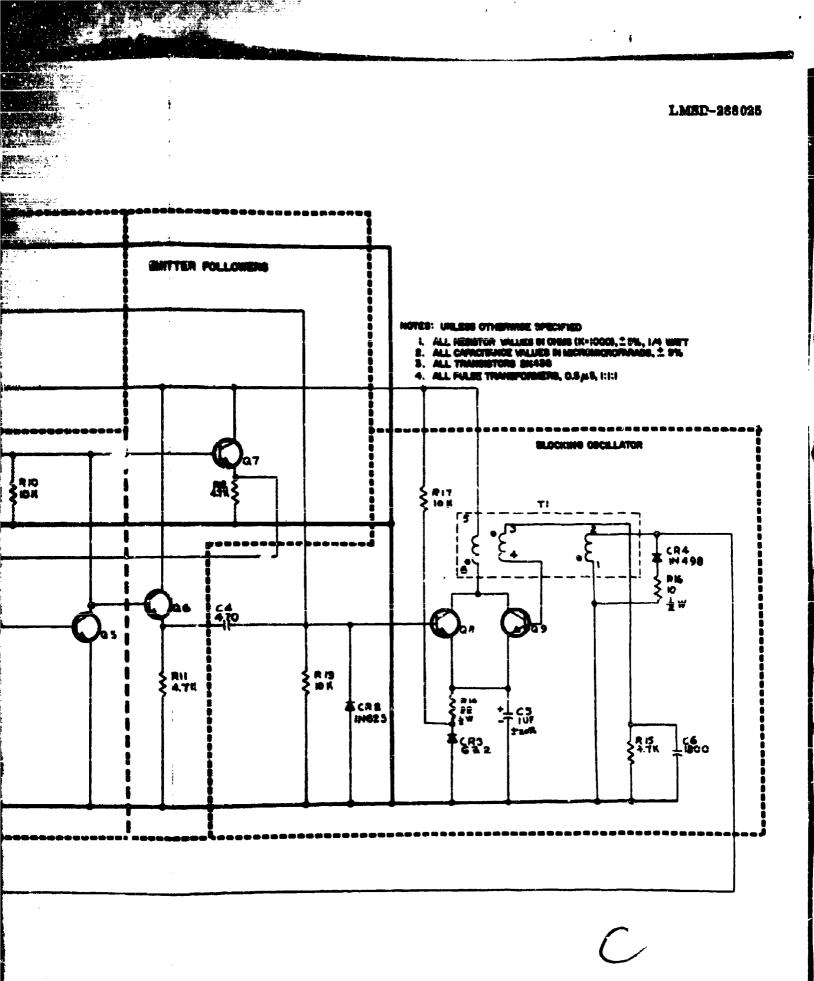

| <b>A-13</b>  | Sync Gate, Vibration                                                      | <b>A-29</b>  |

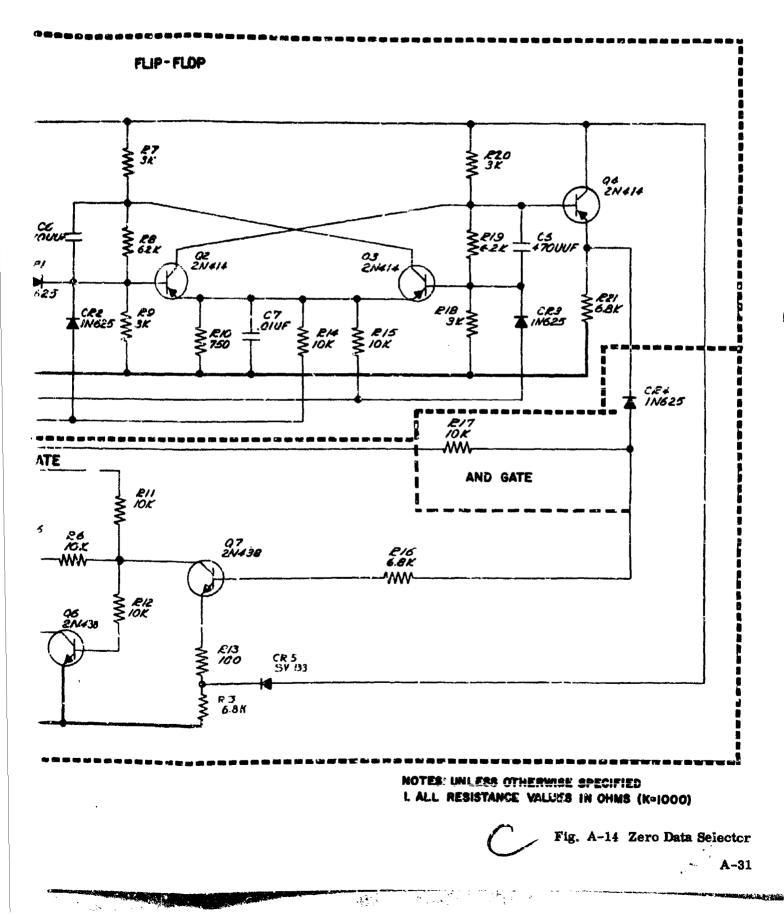

| <b>A-14</b>  | Zero Data Selector                                                        | <b>A-31</b>  |

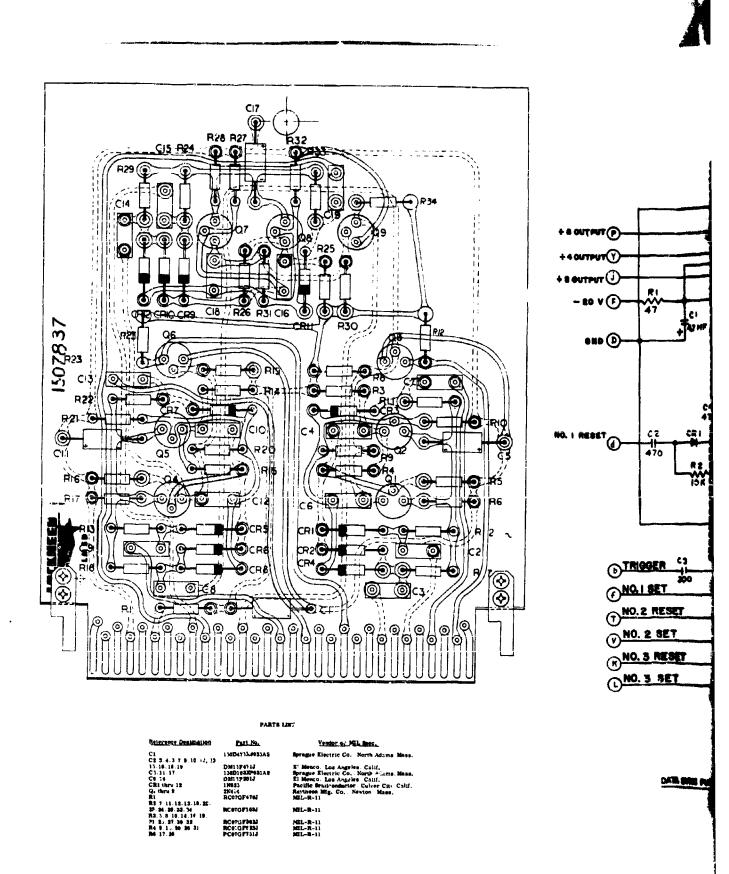

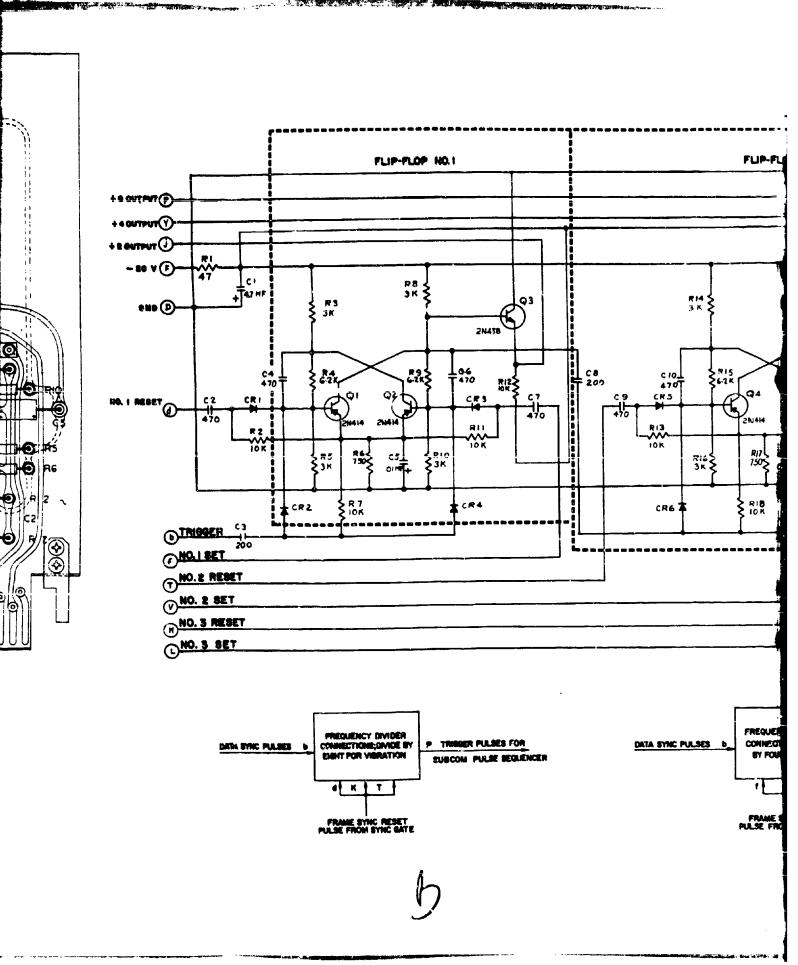

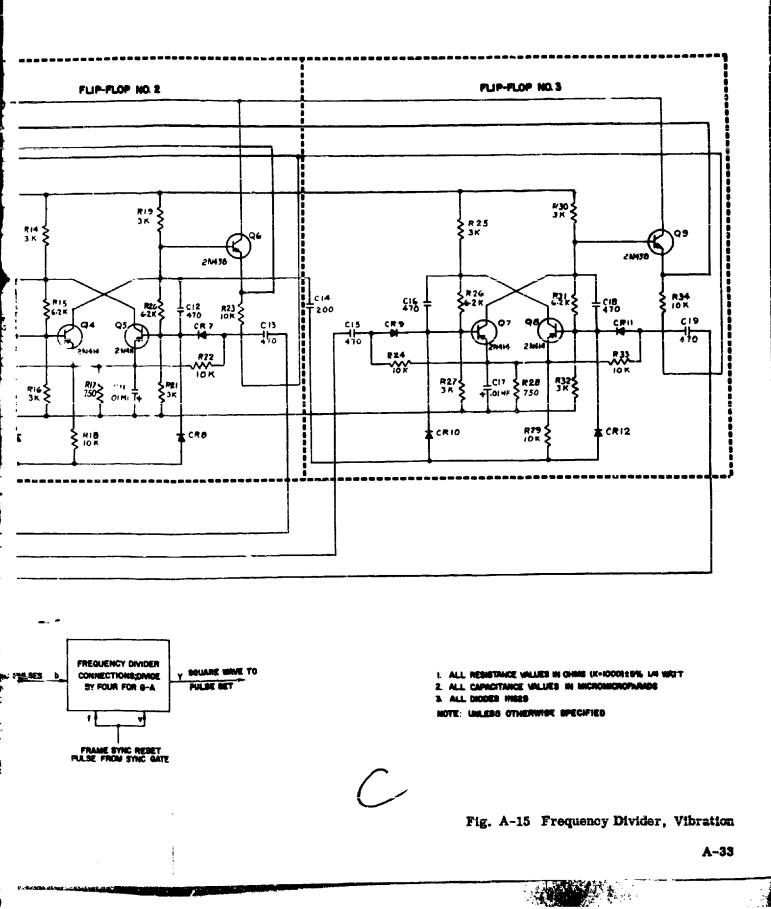

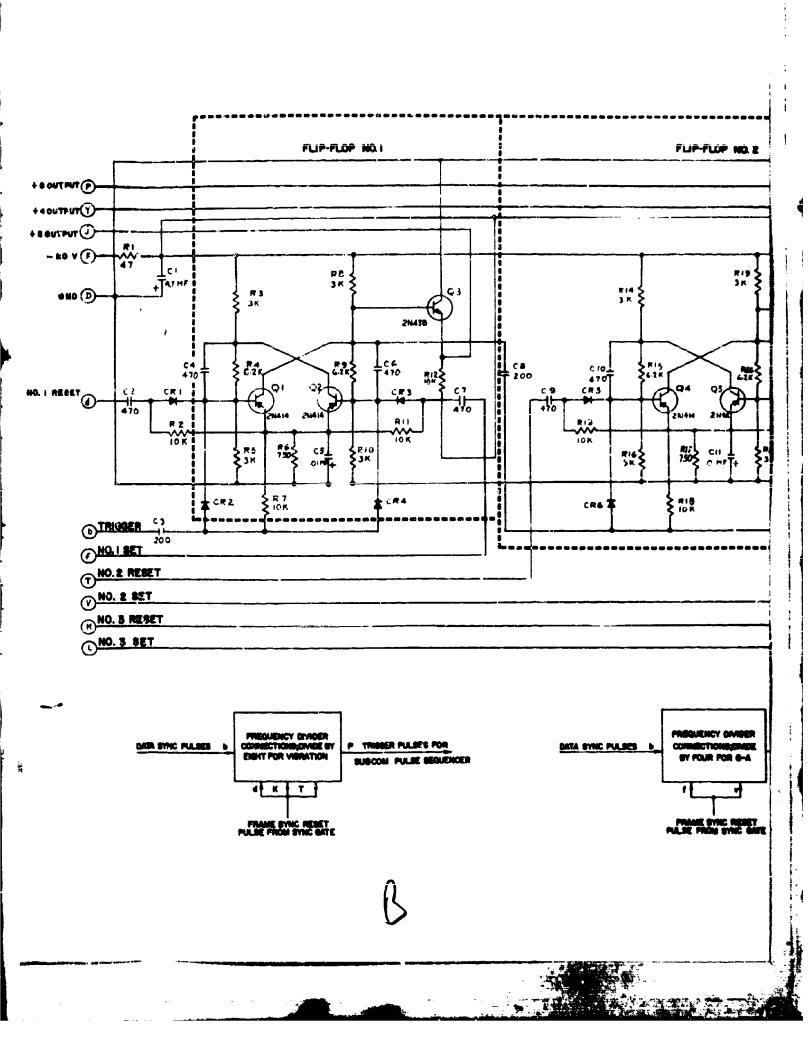

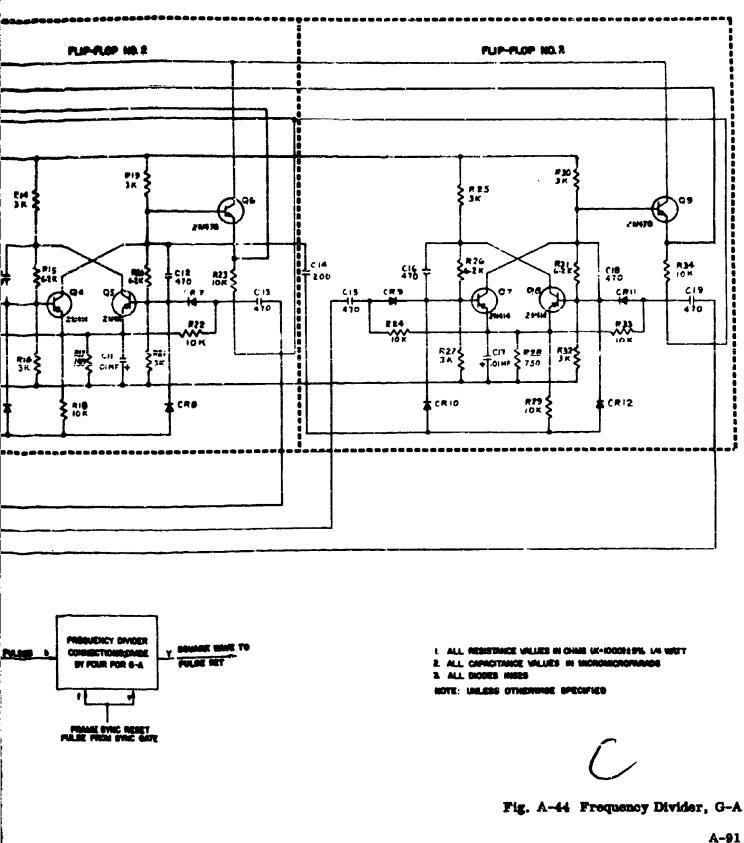

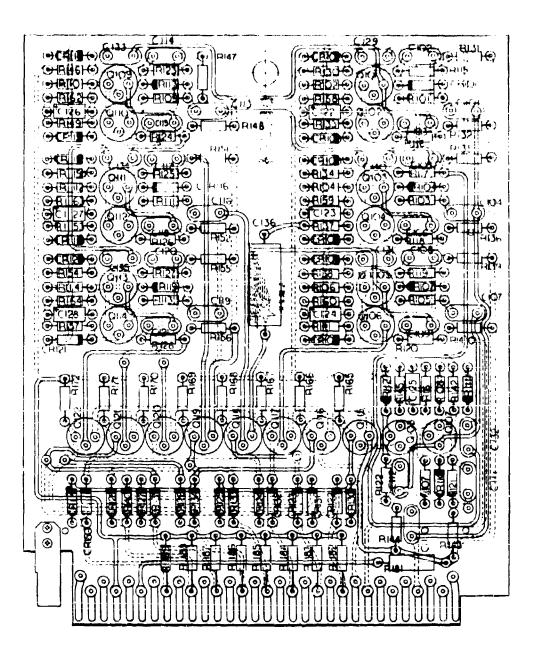

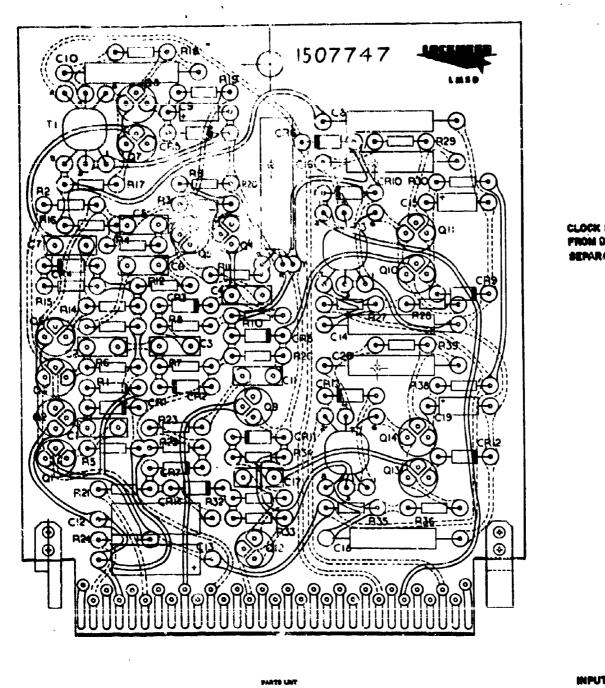

| <b>A-15</b>  | Frequency Divider, Vibration                                              | <u>A-33</u>  |

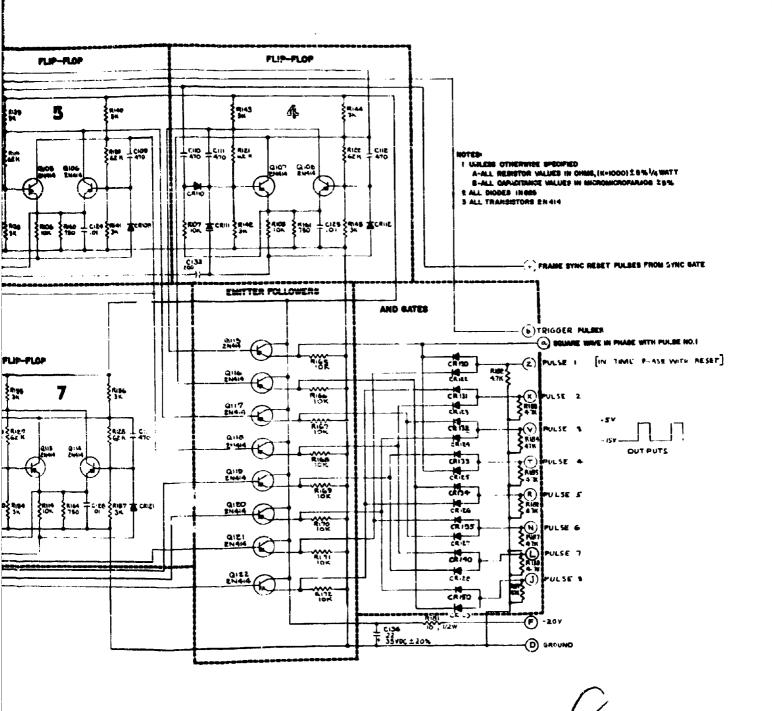

| A-16         | Eight-Channel Pulse Sequencer, Vibration                                  | <b>A-35</b>  |

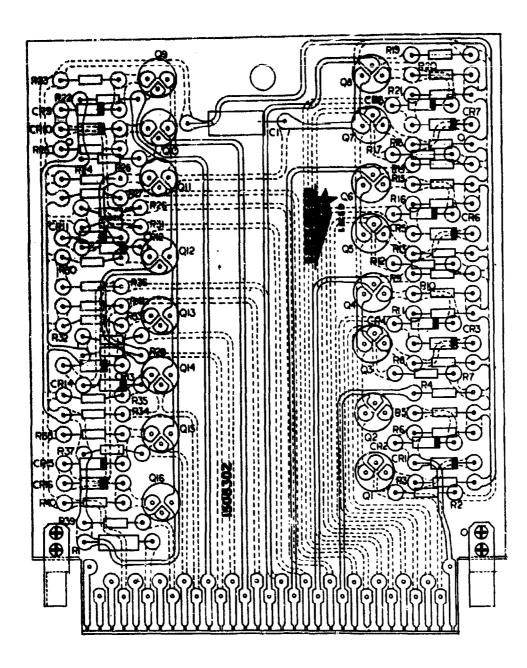

| <b>A-17</b>  | Data Gates, Vibration                                                     | <b>A-3</b> 7 |

| A-18         | Data Sync Delay Record, Vibration                                         | A-39         |

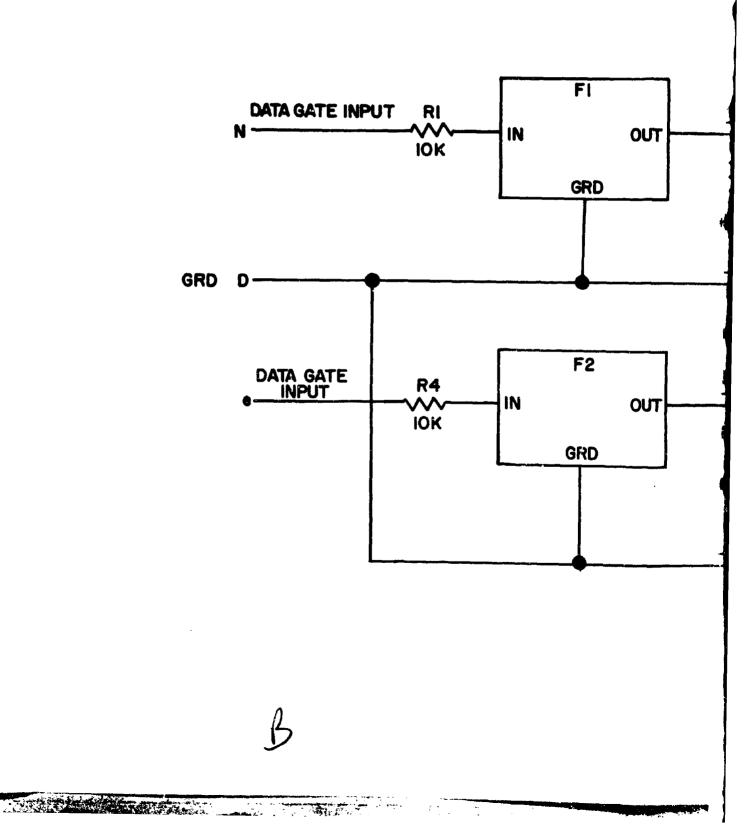

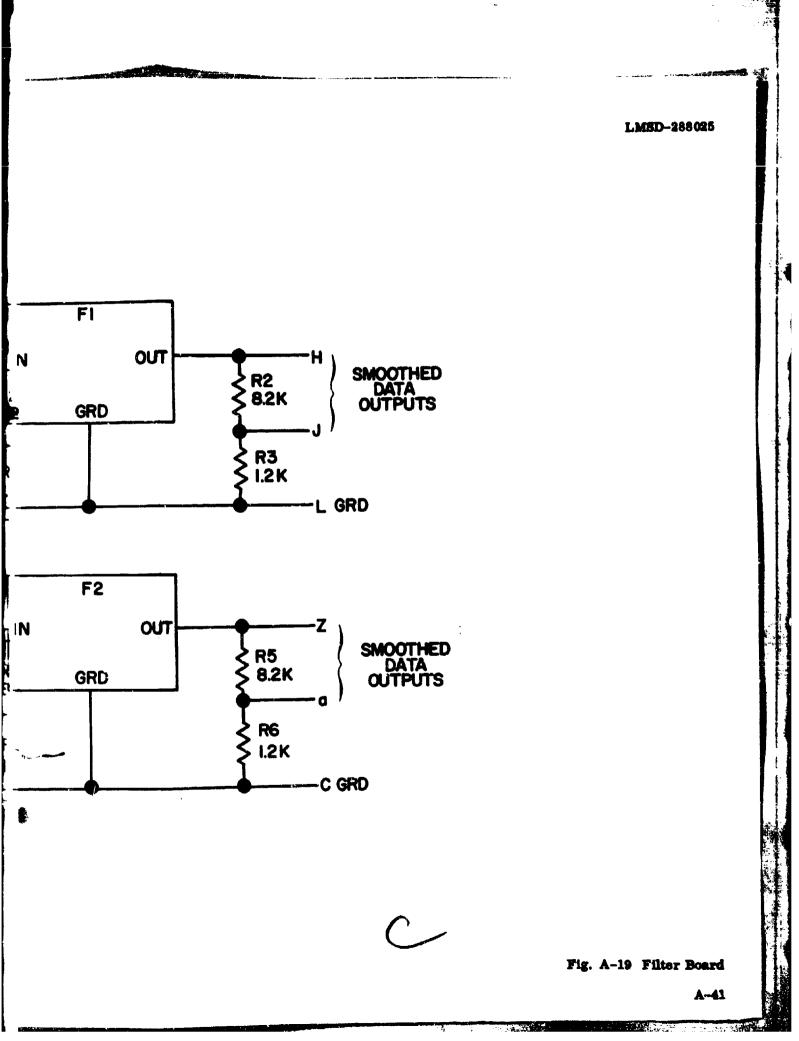

| A19          | Filter Board                                                              | <b>A-4</b> 1 |

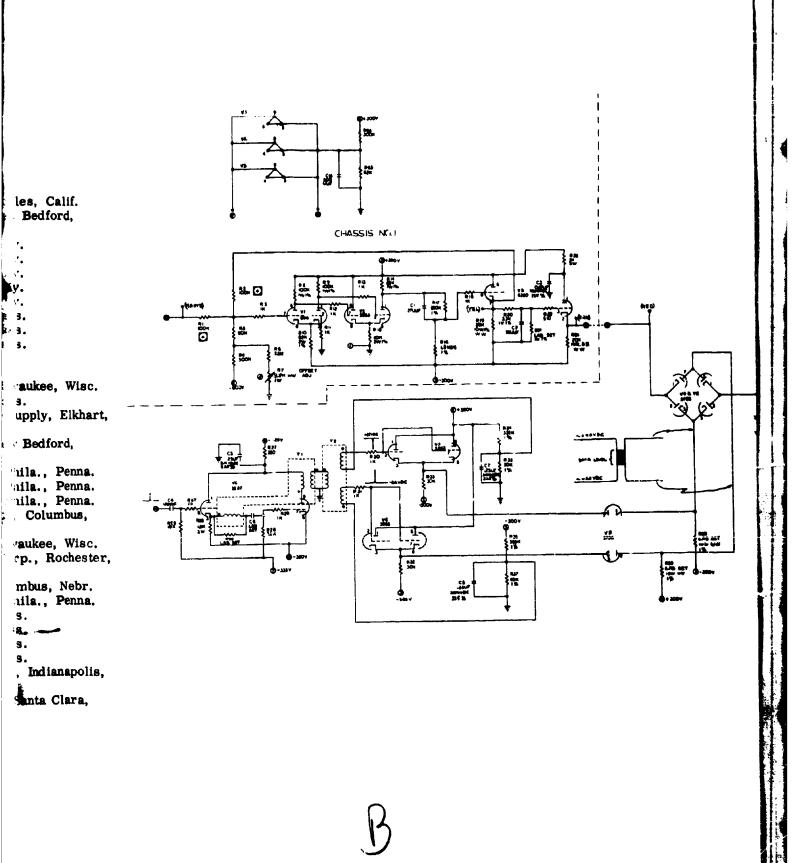

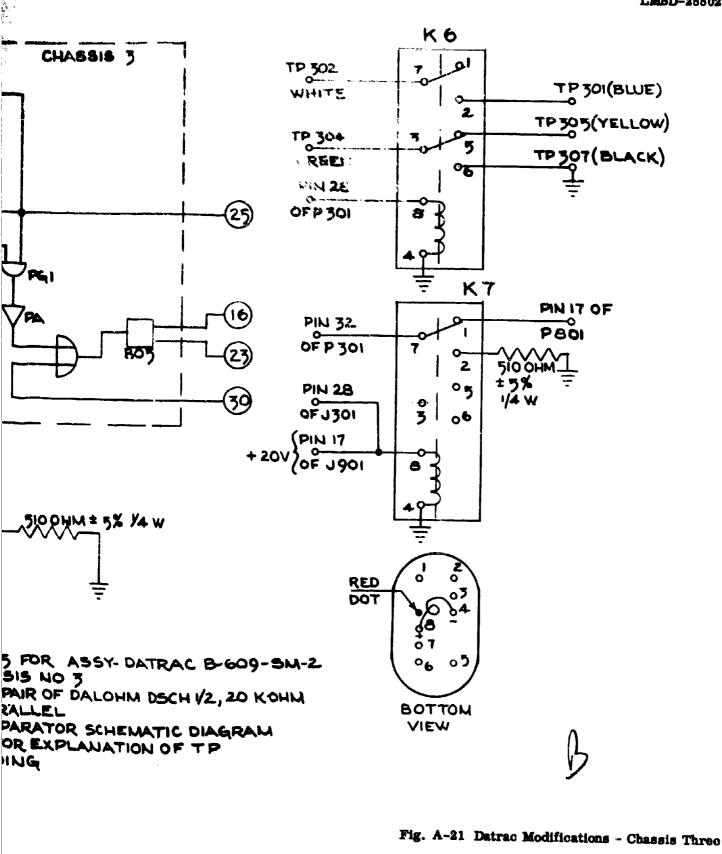

| A-20         | Datrae Modifications - Chassis One and Two                                | <b>A-4</b> 3 |

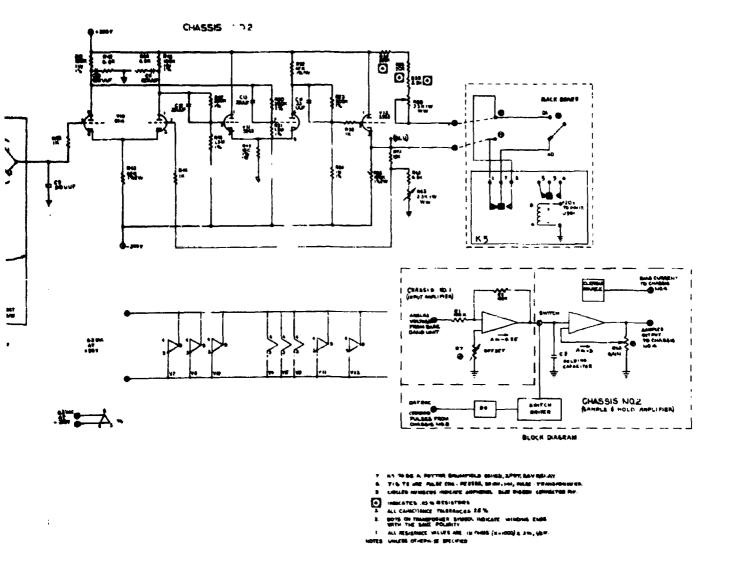

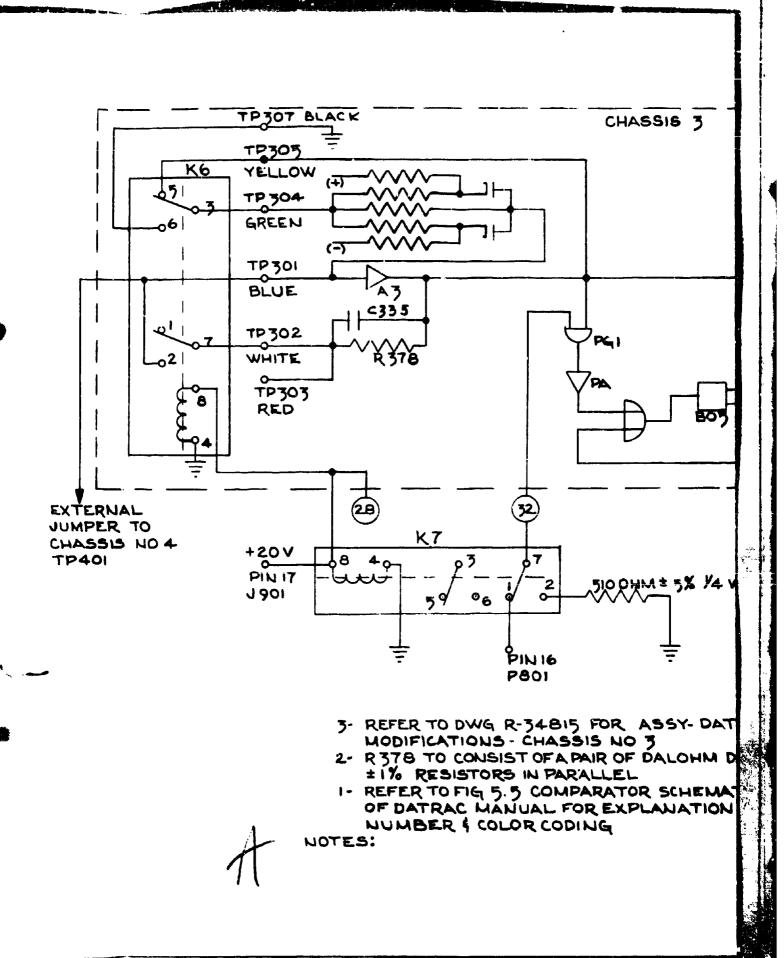

| <b>A-2</b> 1 | Datrac Modifications - Chassis Three                                      | <b>A-4</b> 5 |

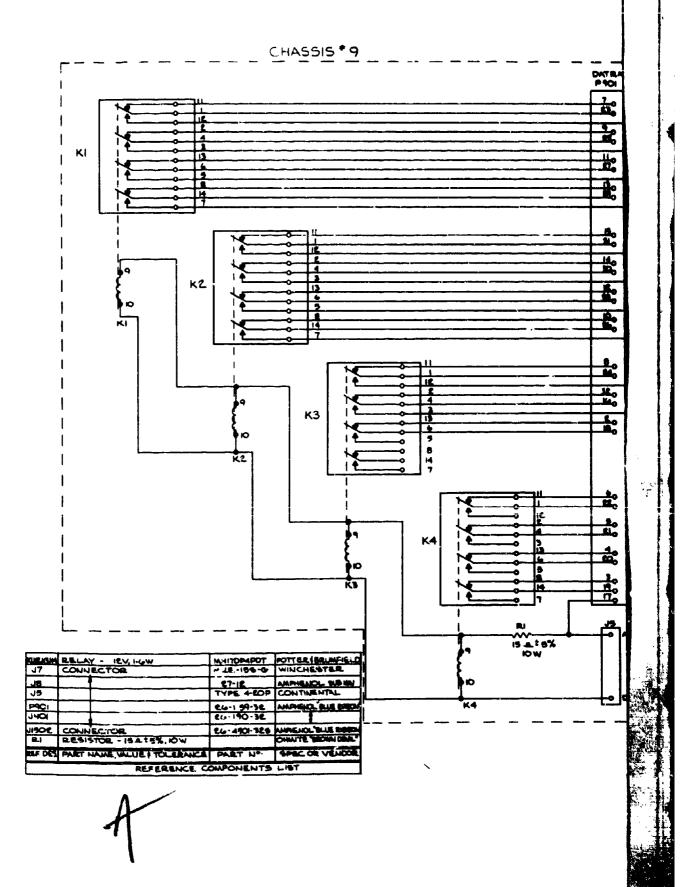

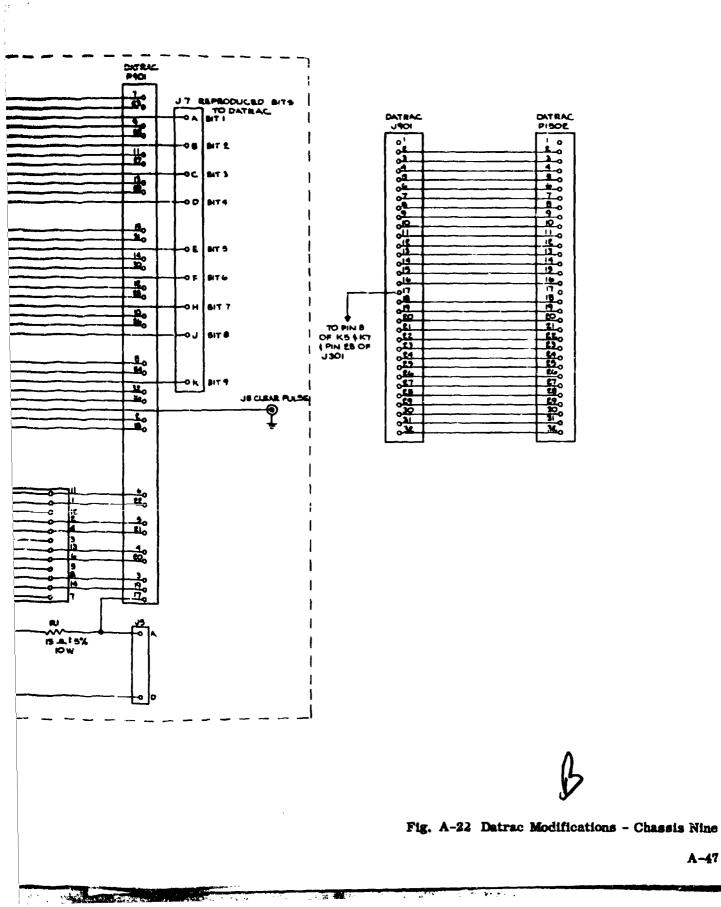

| A-22         | Datrac Modifications - Chassis Nine                                       | <b>A-4</b> 7 |

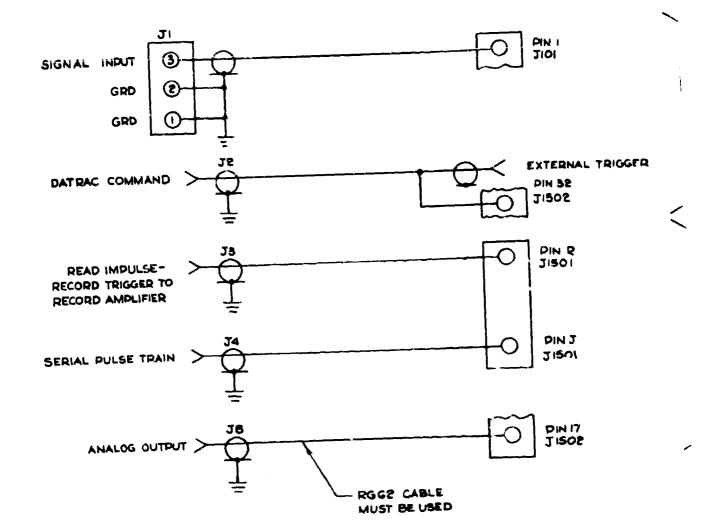

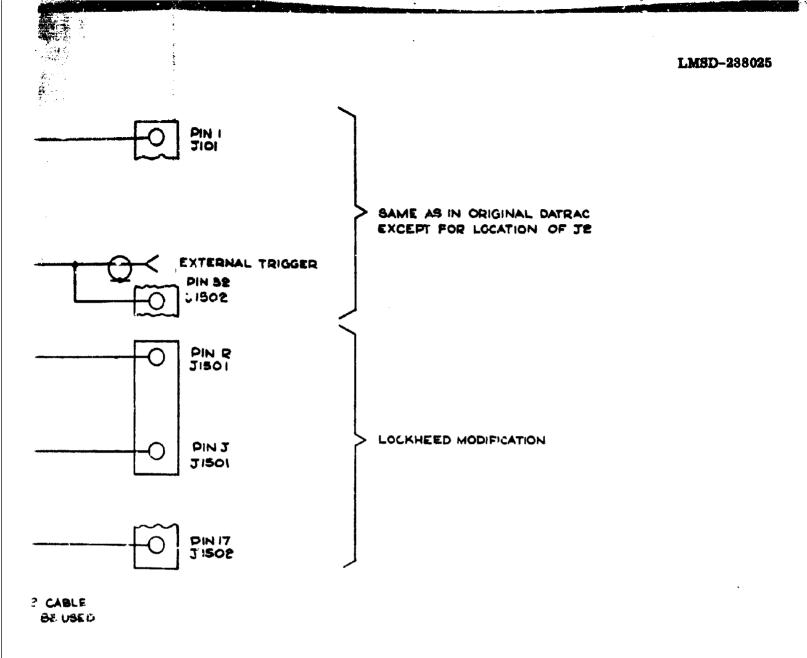

| A-23         | Datrac External Modifications                                             | A-49         |

| <b>A-24</b>  | Datrac Modifications - Record Outputs and Output Signal<br>Monitor Points | <b>A</b> -51 |

(inter-

Ĩ

T

1

ł

ł

MISSILES and SPACE DIVISION

an an an the state of the state

XŸ

I

E

Ē

E

[]

Ŀ

ĺ

Ľ.

Ľ

U

ij

ř

| Figure       |                                                        | Page          |

|--------------|--------------------------------------------------------|---------------|

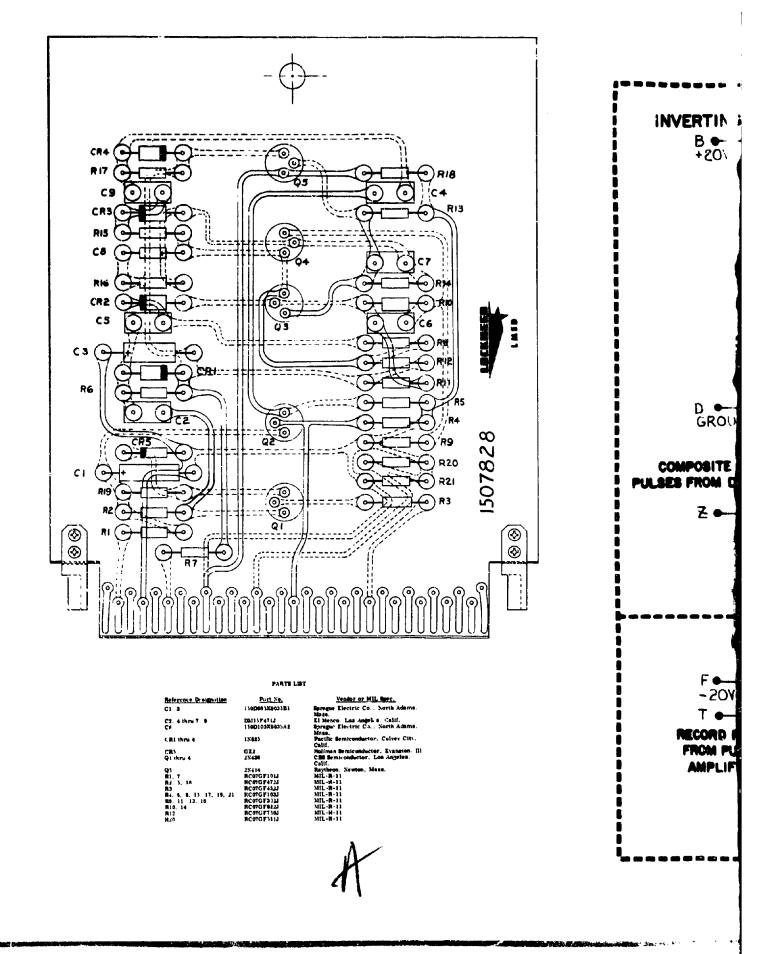

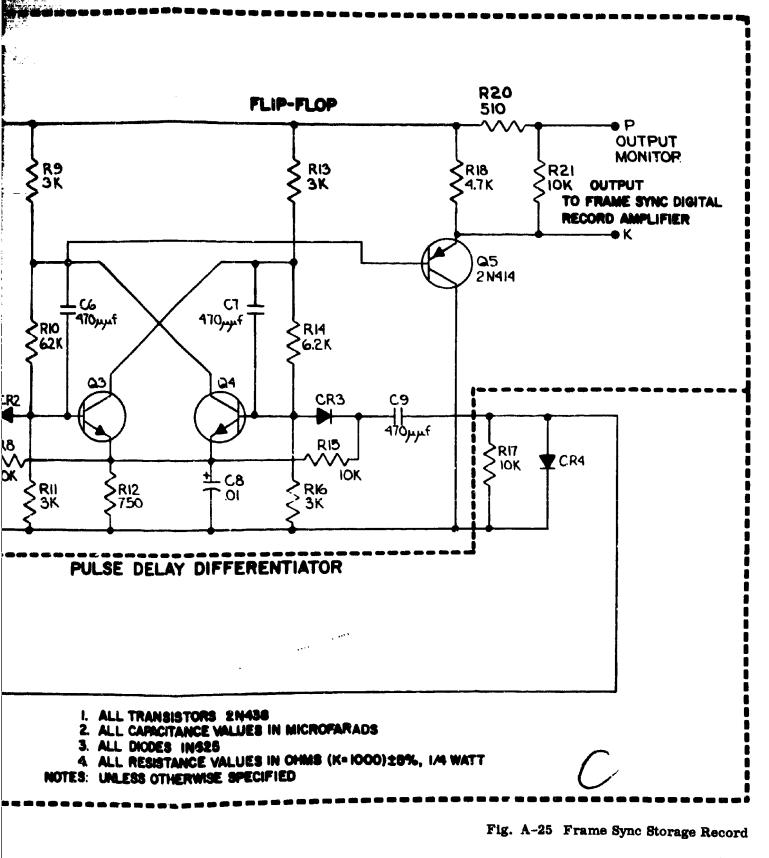

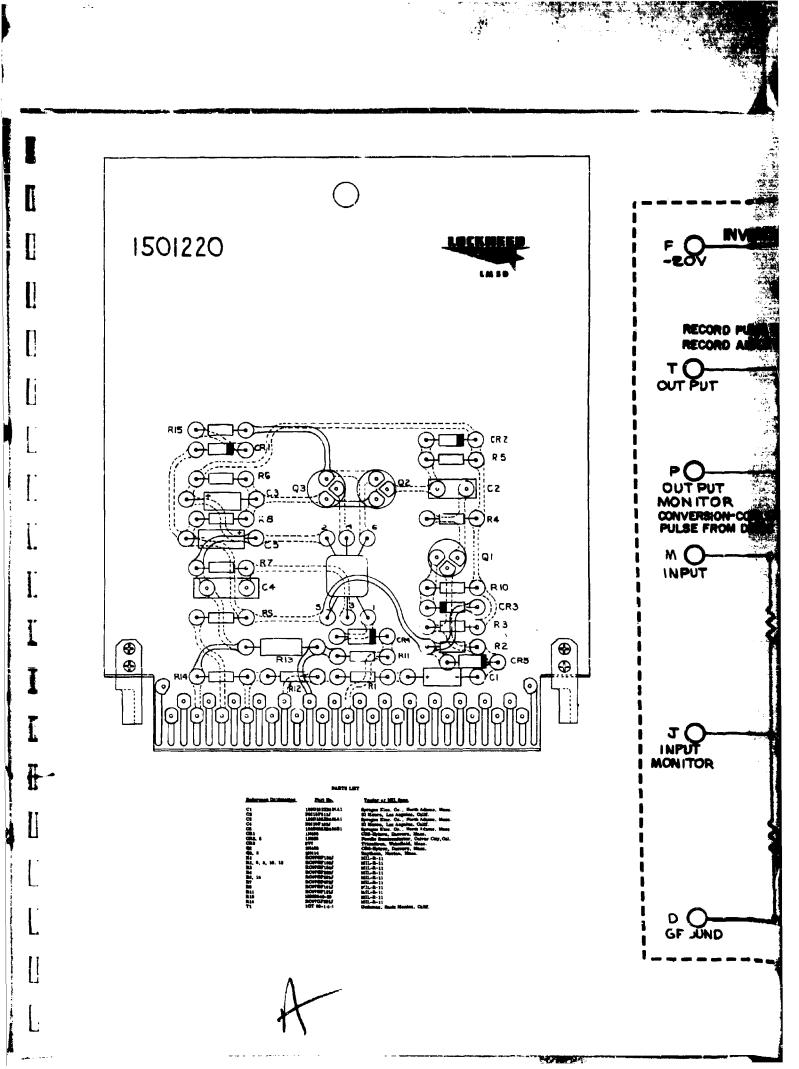

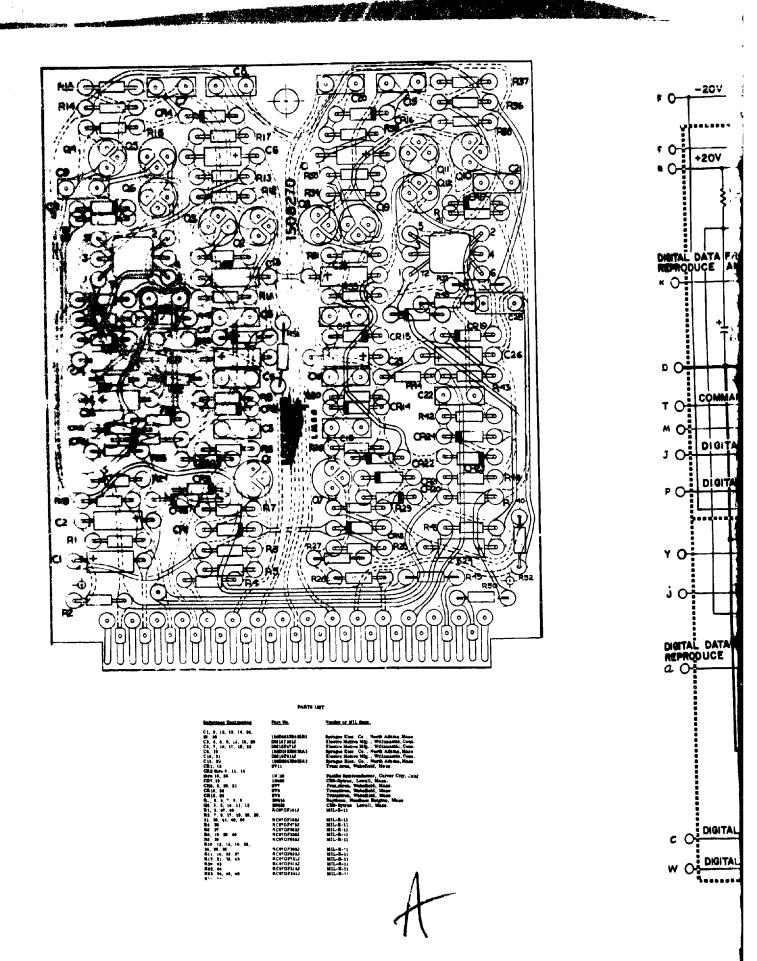

| A=25         | Frame Sync Storage Record                              | <b>A-</b> 53  |

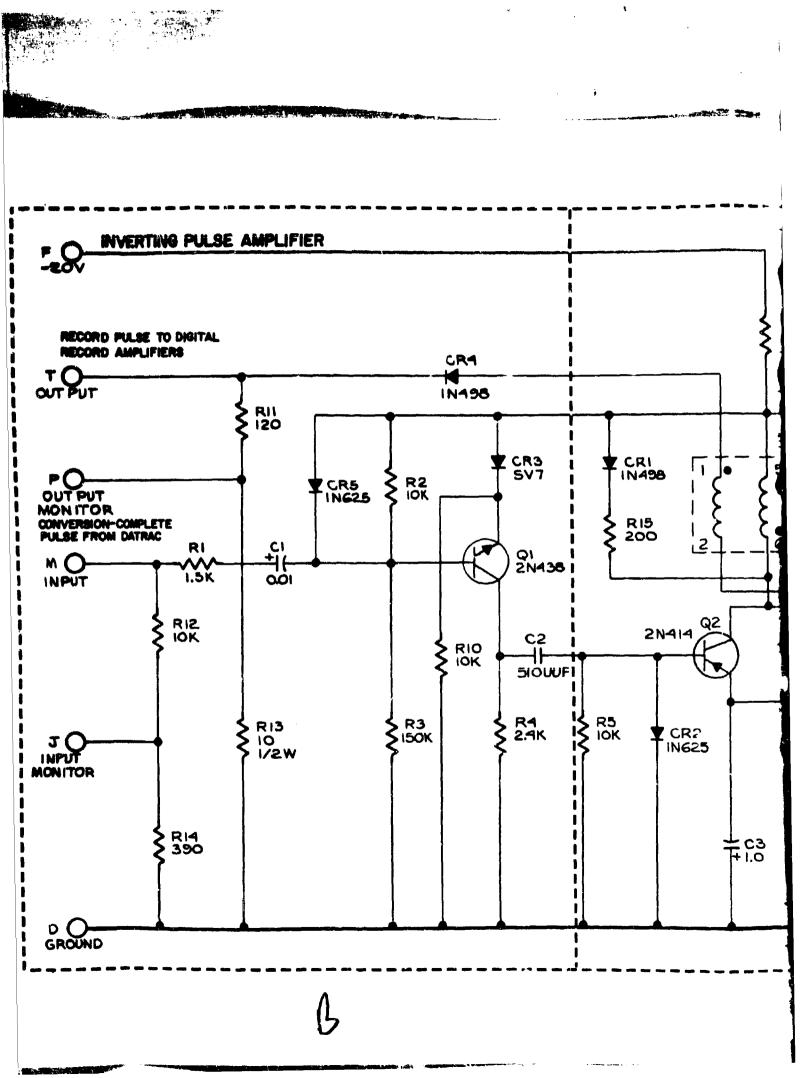

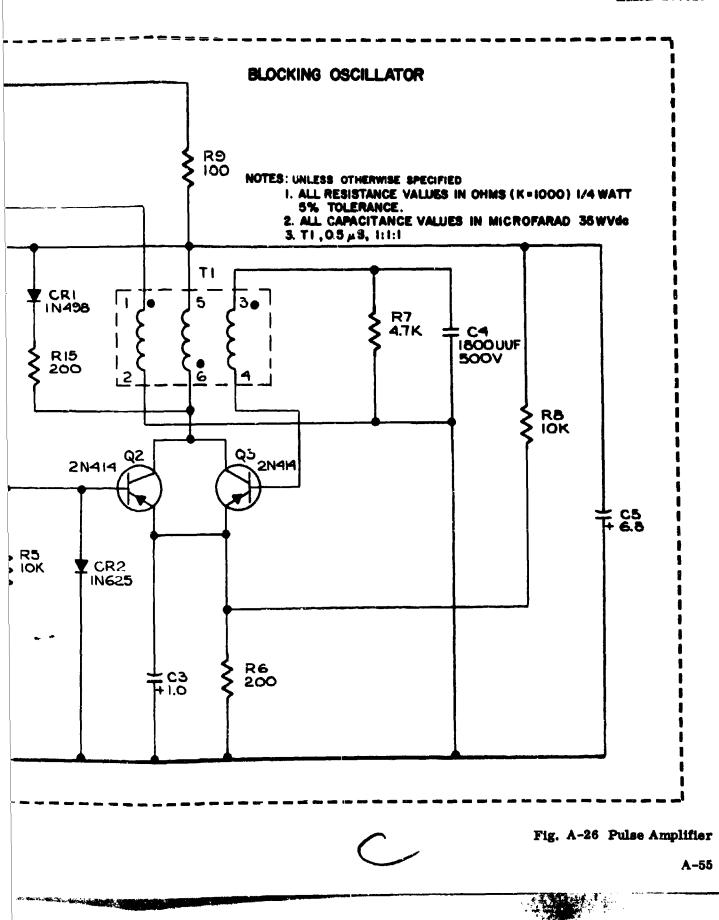

| A-26         | Pulse Amplifier                                        | A-55          |

| A-27         | Digital Record Amplifier                               | A-57          |

| A-28         | Digital Reproduce Amplifier                            | A-59          |

| A-29         | Data Storage and Gate                                  | <b>A</b> -61  |

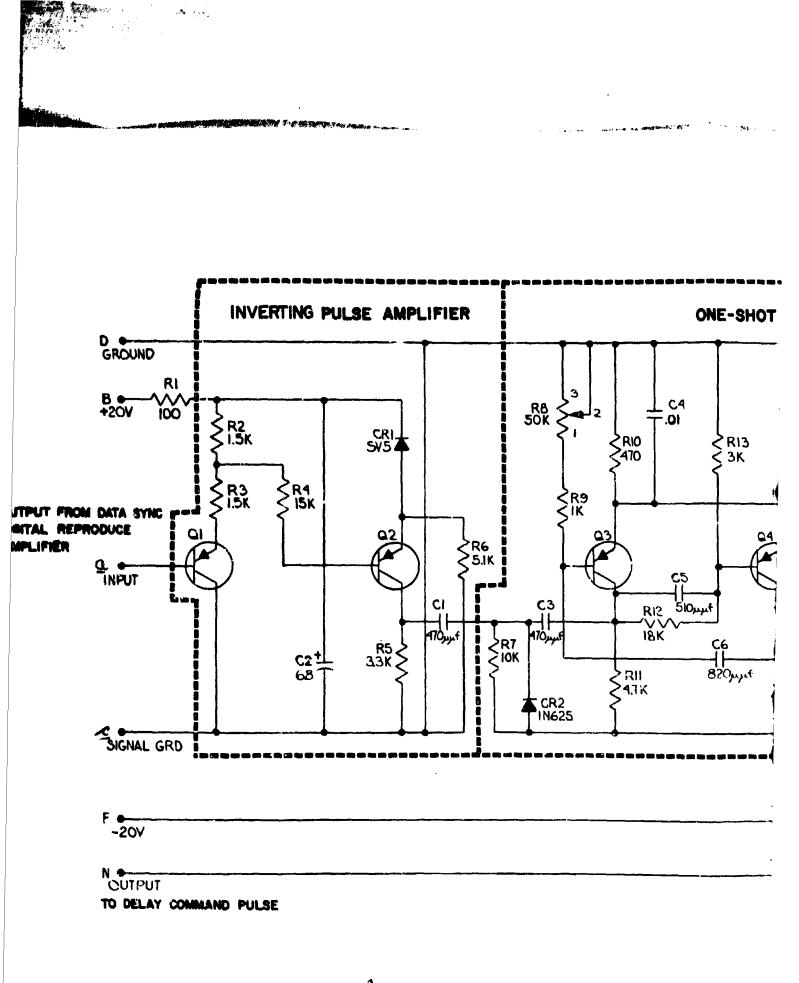

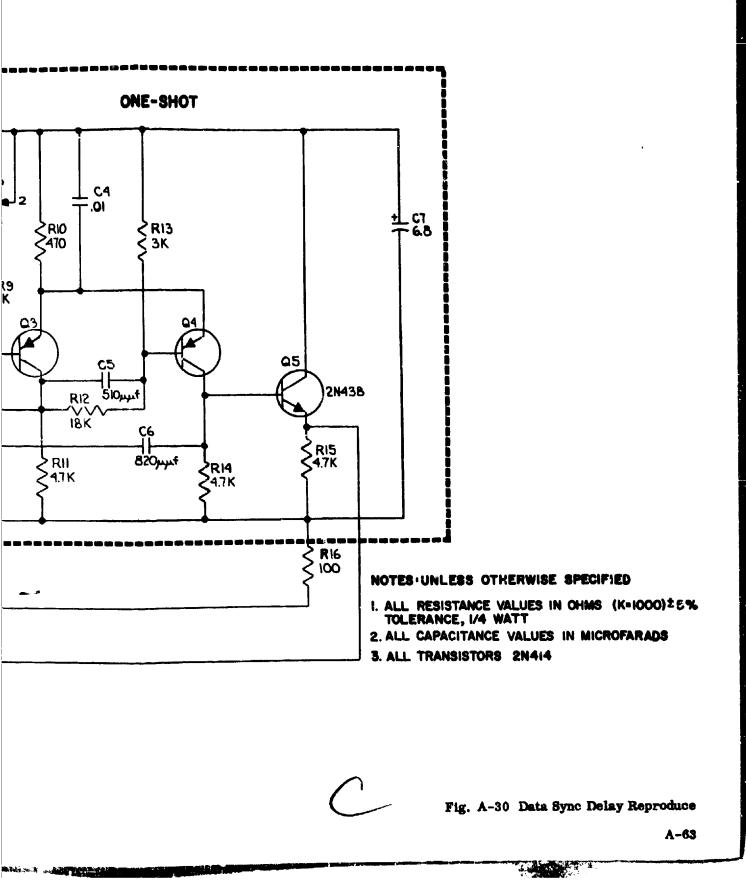

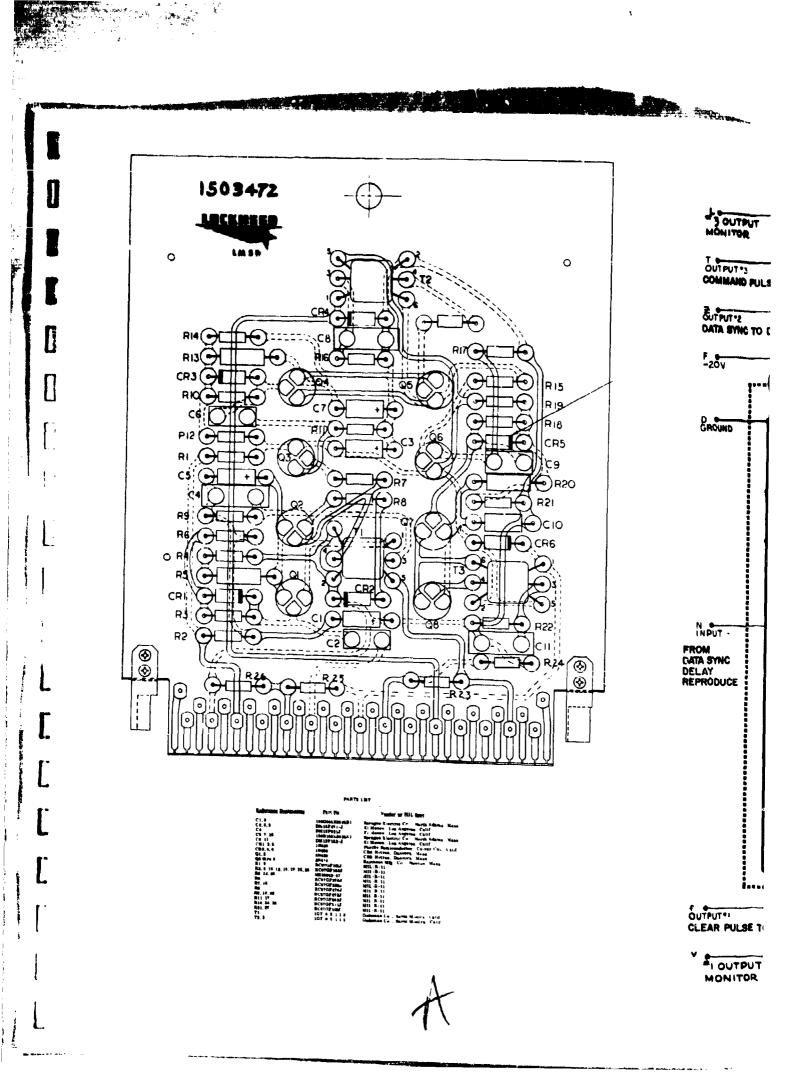

| A-30         | Data Sync Delay Reproduce                              | <b>A</b> 63   |

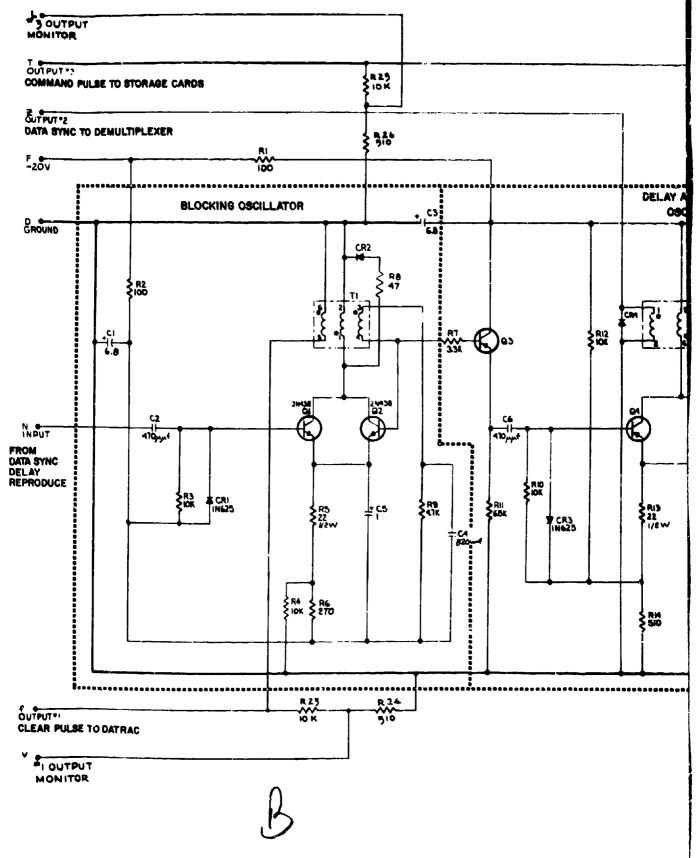

| A-31         | Delay Command Pulse                                    | A-65          |

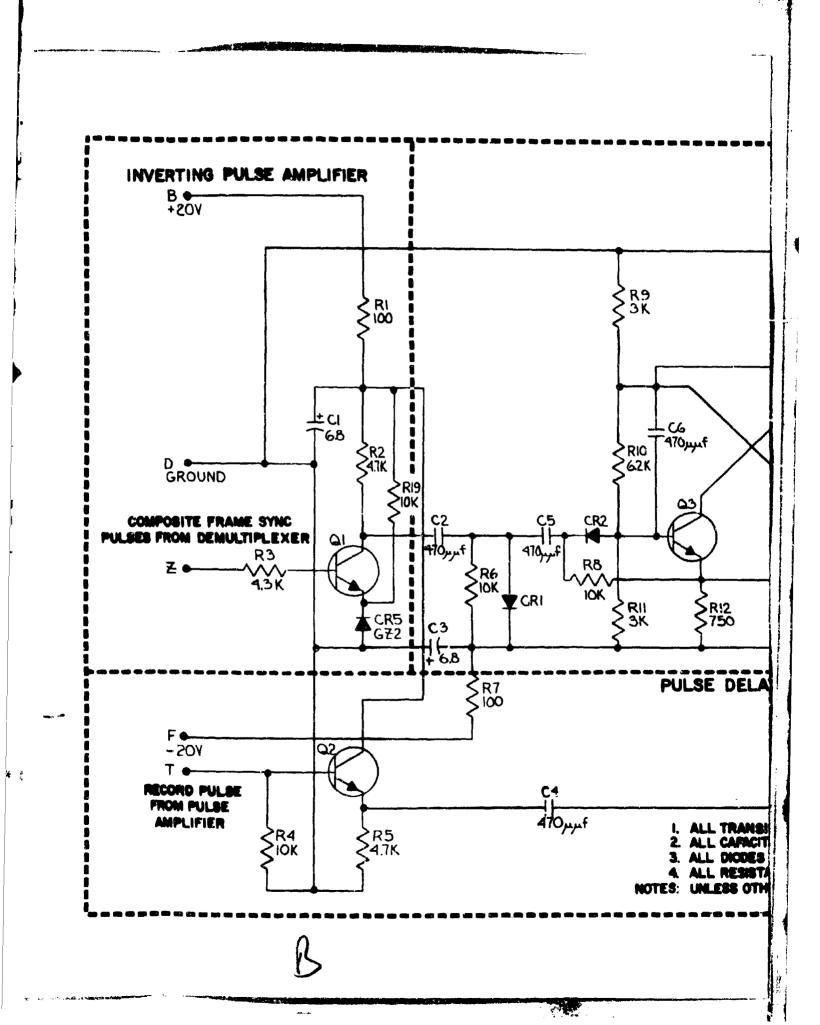

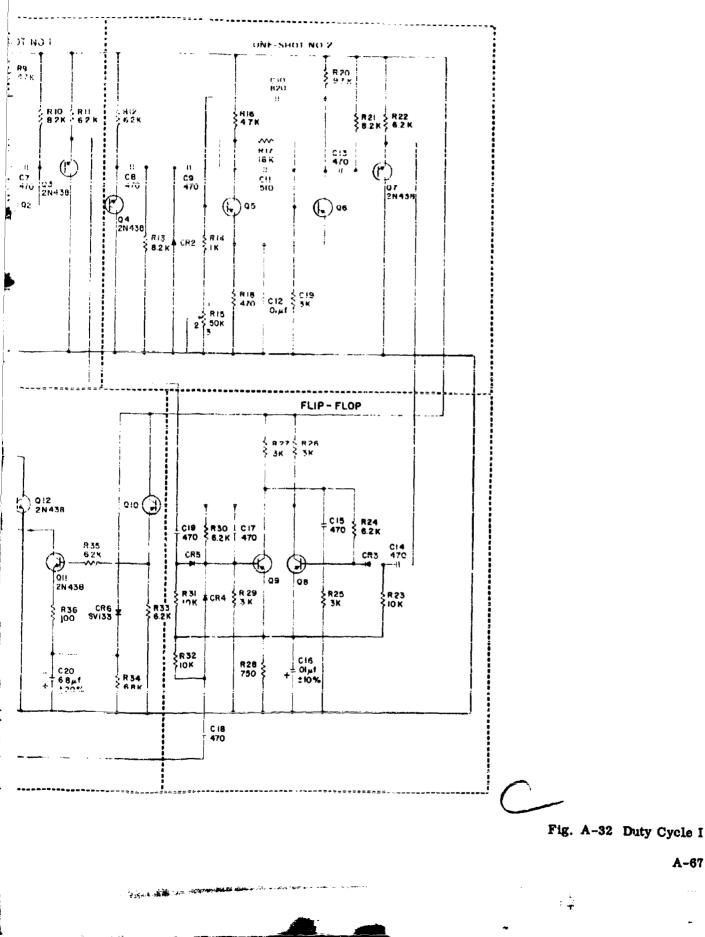

| A-32         | Duty Cycle I                                           | A-67          |

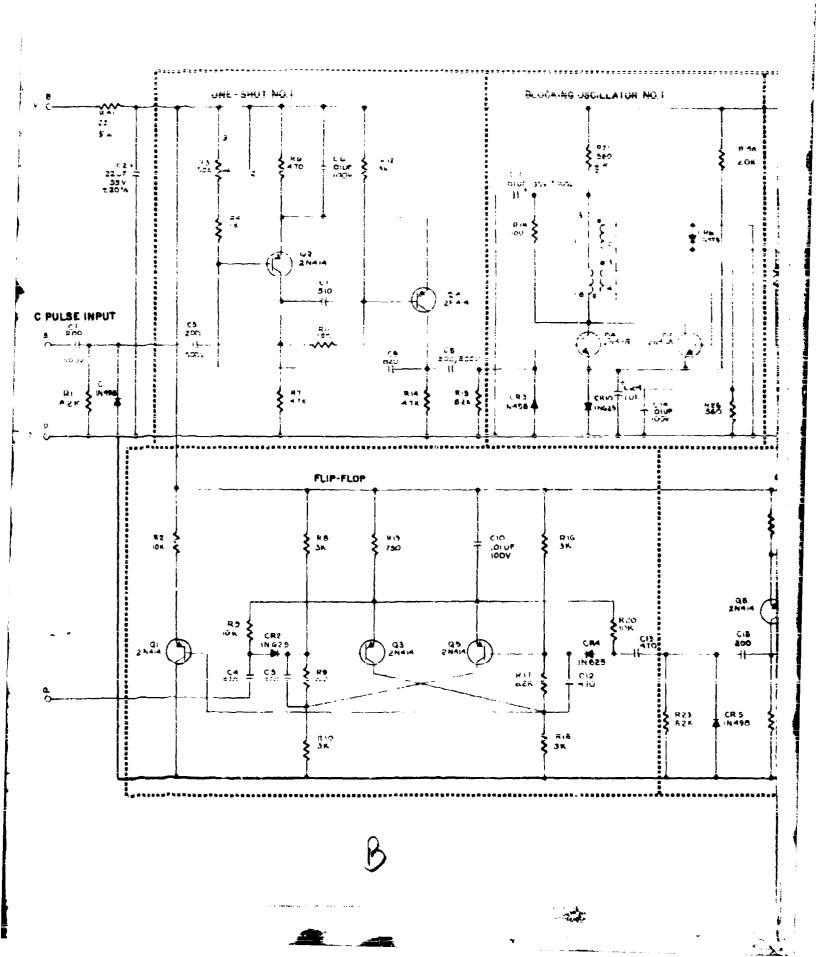

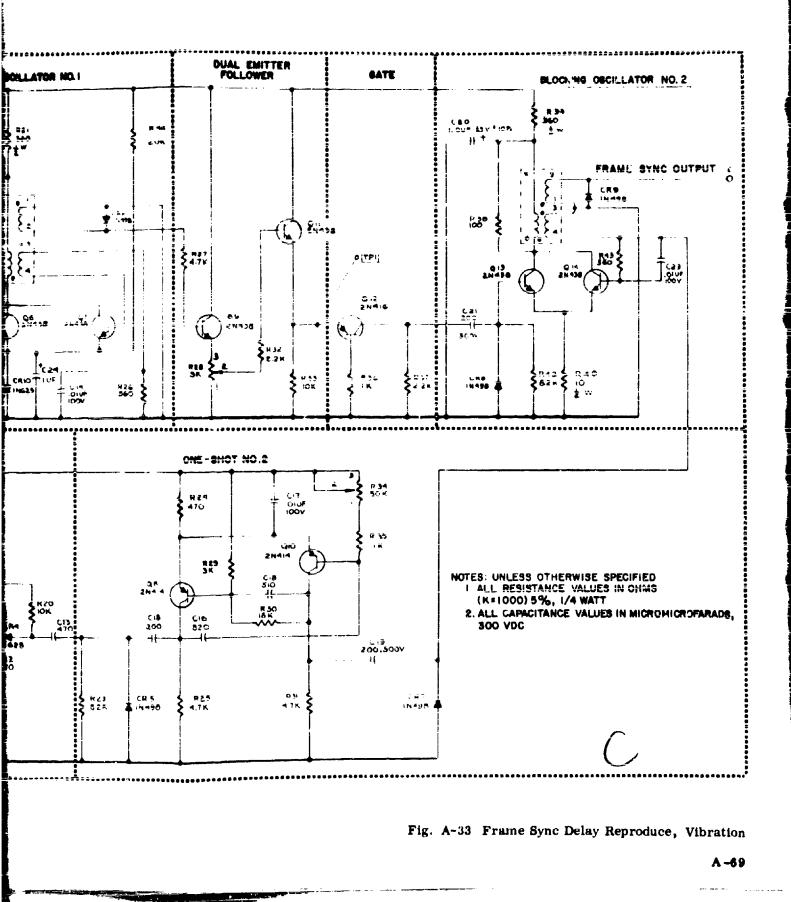

| A-33         | Frame Sync Delay Reproduce, Vibration                  | <b>A</b> -69  |

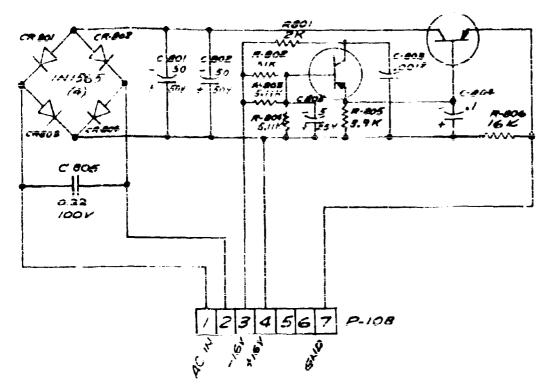

| A-34         | Power Supply Interlock                                 | <b>A-7</b> 1  |

| <b>A-3</b> 5 | Relay Board                                            | <b>A-7</b> 3  |

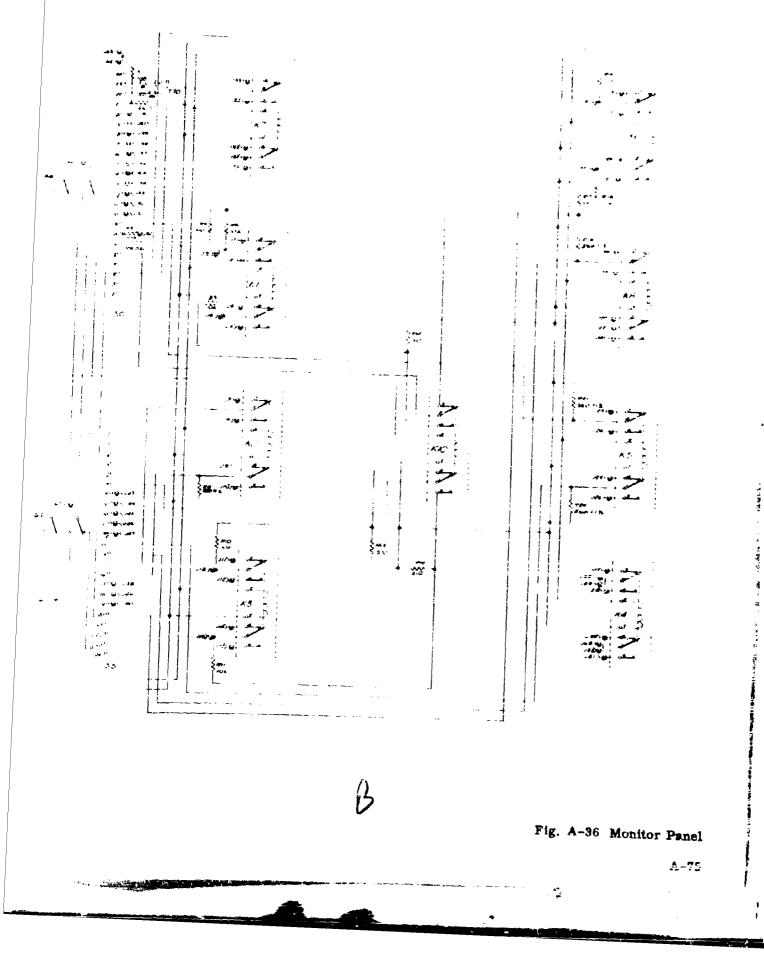

| A-36         | Monitor Panel                                          | <b>A</b> -75  |

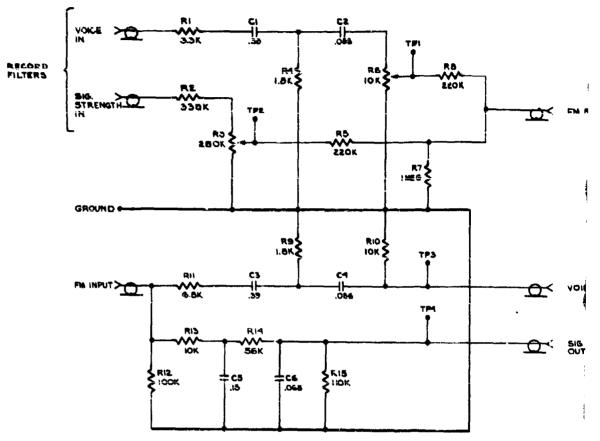

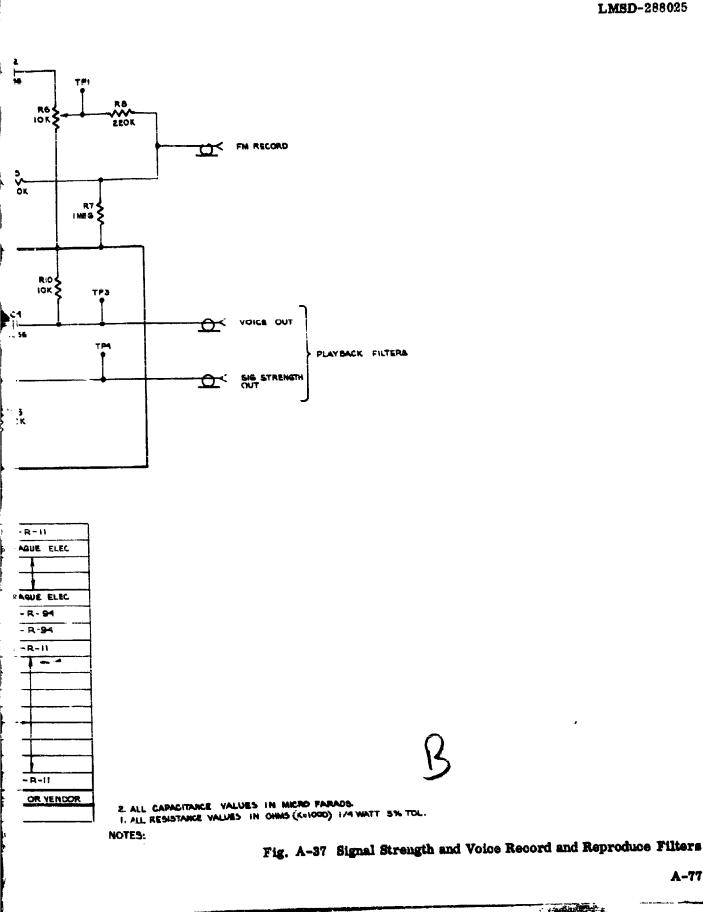

| -37          | Signal Strength and Voice Record and Reproduce Filters | <b>A</b> -77  |

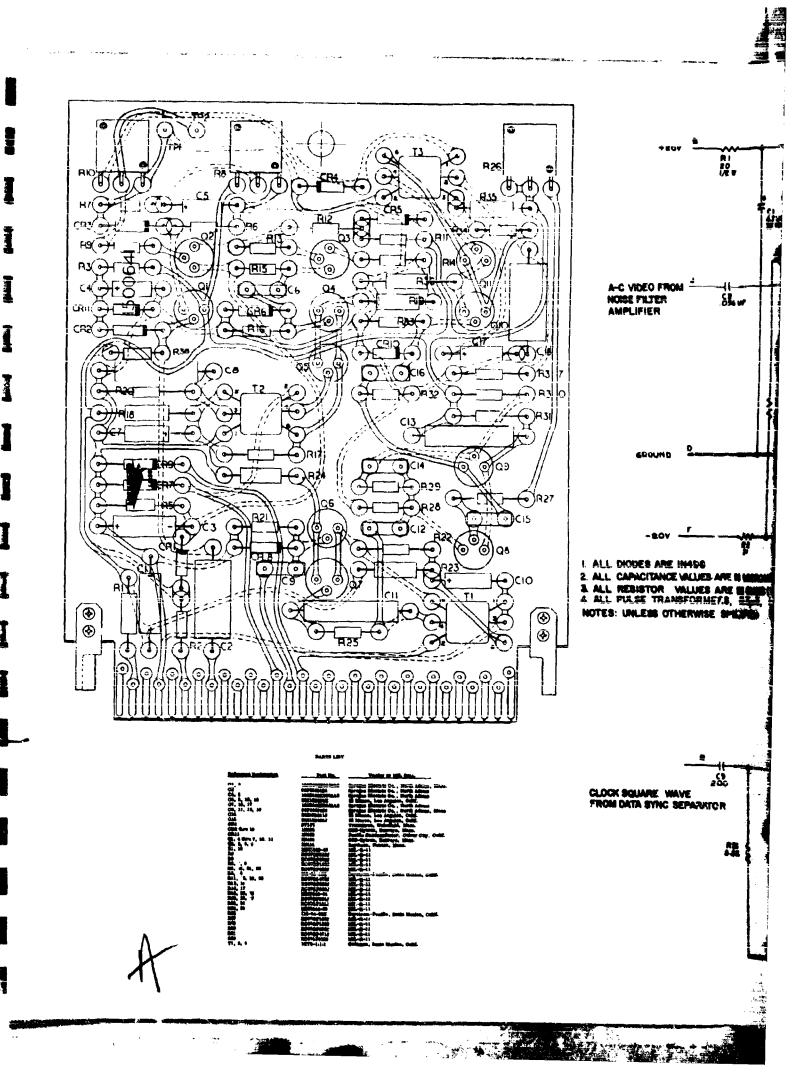

| A-38         | Data Sync Separator, G-A                               | A-79          |

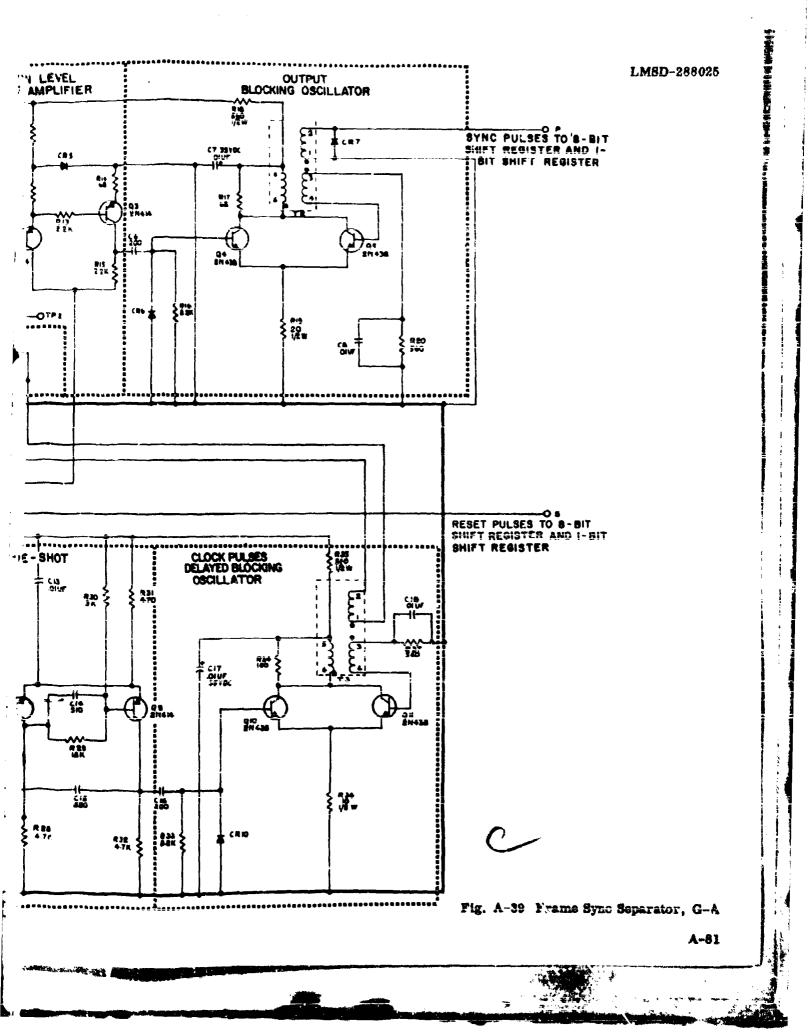

| A-39         | Frame Sync Separator, G-A                              | A-81          |

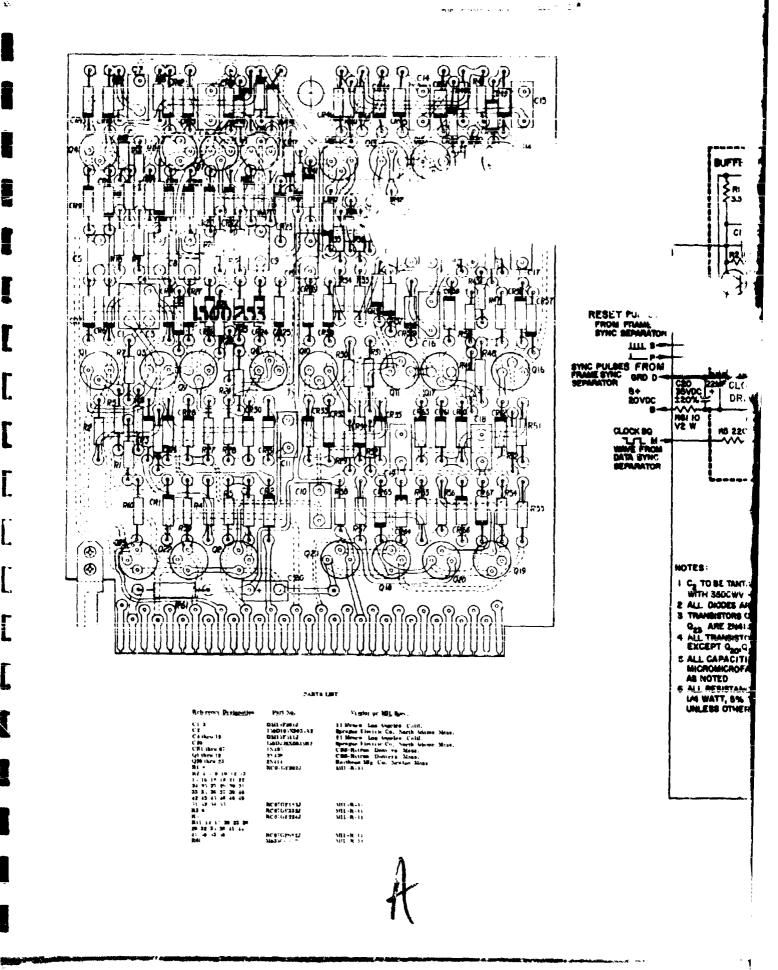

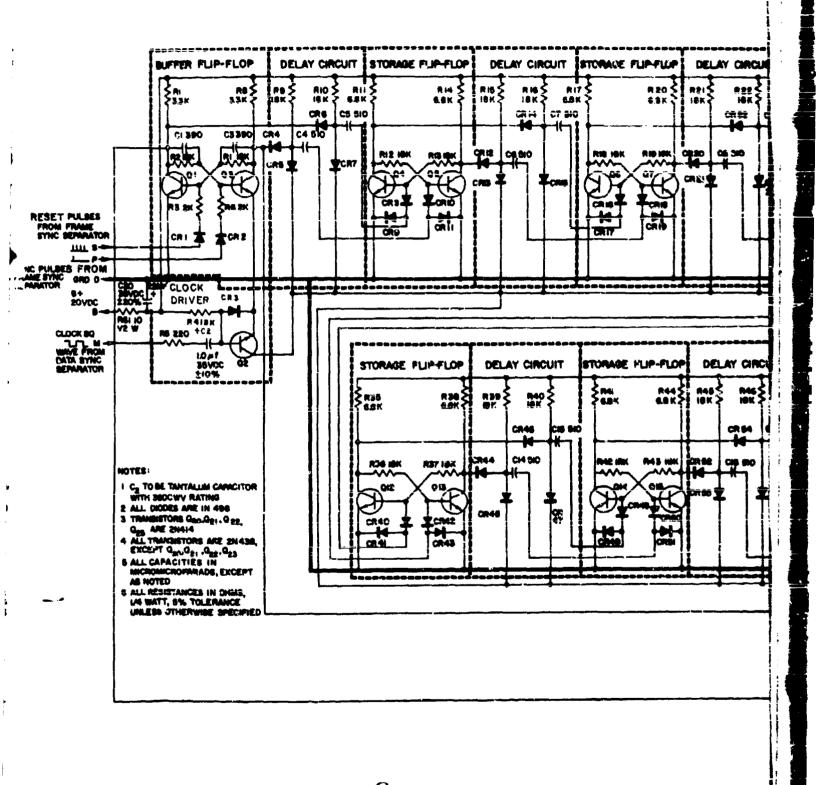

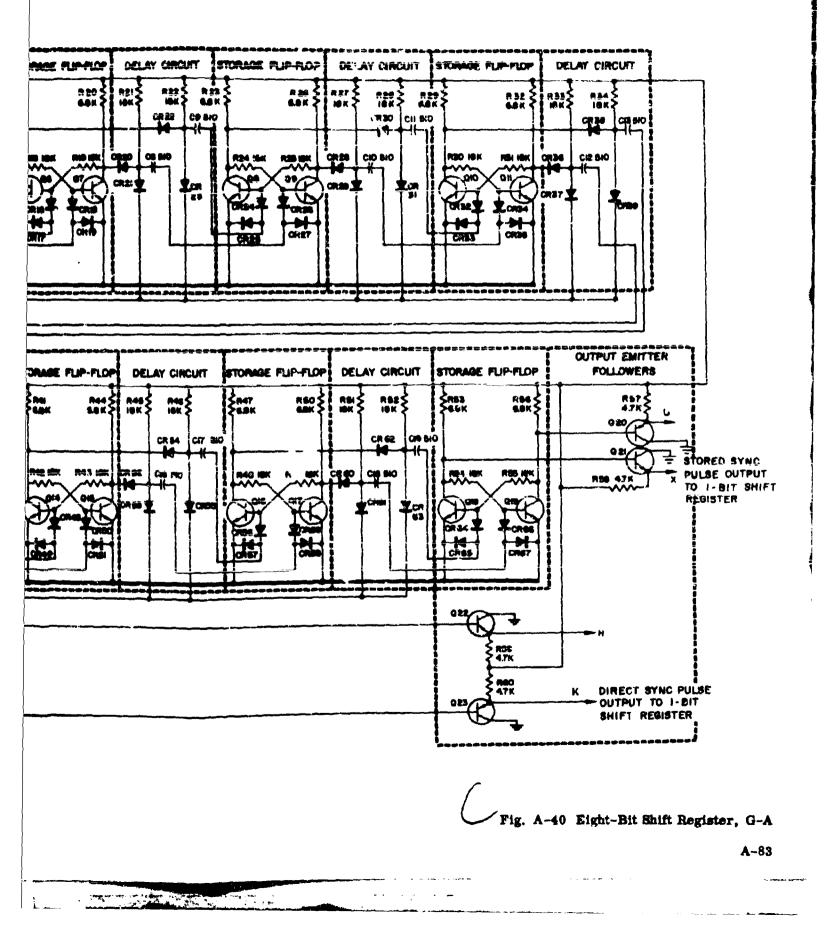

| A-40         | Eight-Bit Shift Register, G-A                          | A-83          |

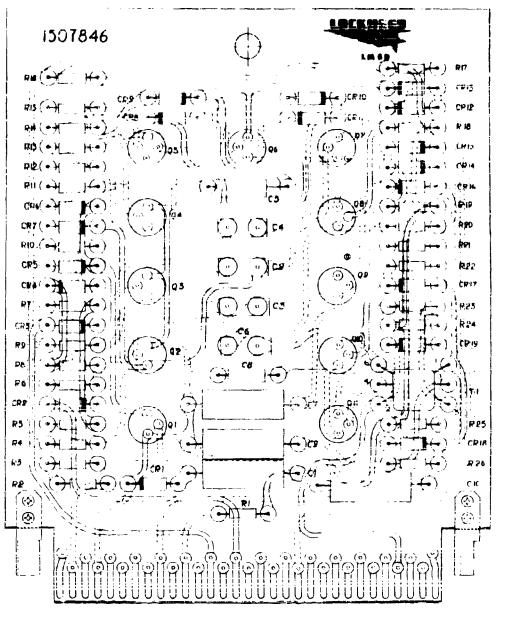

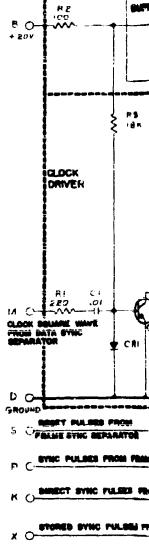

| A-41         | One-Bit Shift Register                                 | A-85          |

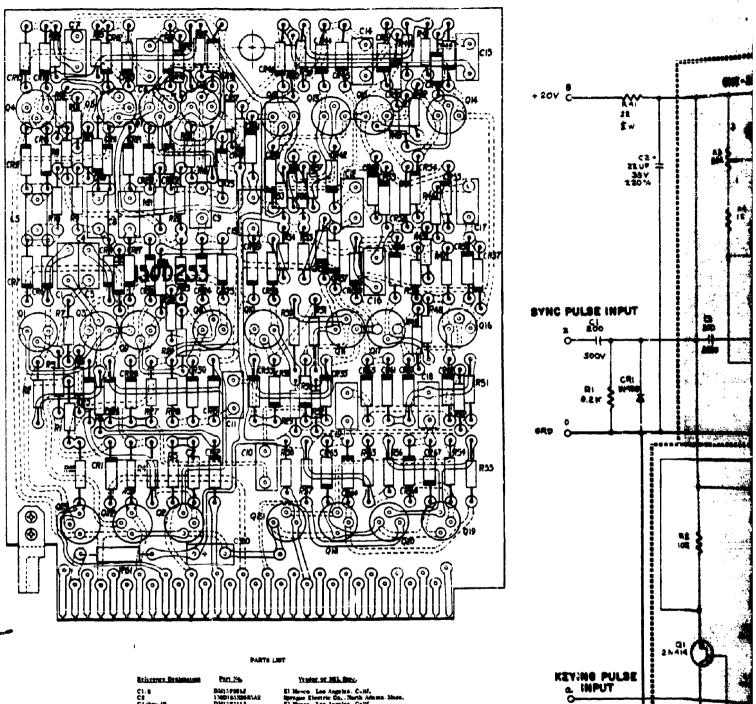

| A-42         | Sync Selector, G-A                                     | A-87          |

| A-43         | Sync Gate, G-A                                         | A-89          |

| A-44         | Frequency Divider, G-A                                 | <b>A-9</b> 1  |

| A-45         | Eight-Channel Pulse Sequencer, G-A                     | <b>A-93</b>   |

| A-46         | Matrix                                                 | <b>A-9</b> 5  |

| A-47         | Data Gates, G-A                                        | <b>A</b> -97  |

| A-48         | Pulse Set                                              | <b>A-99</b>   |

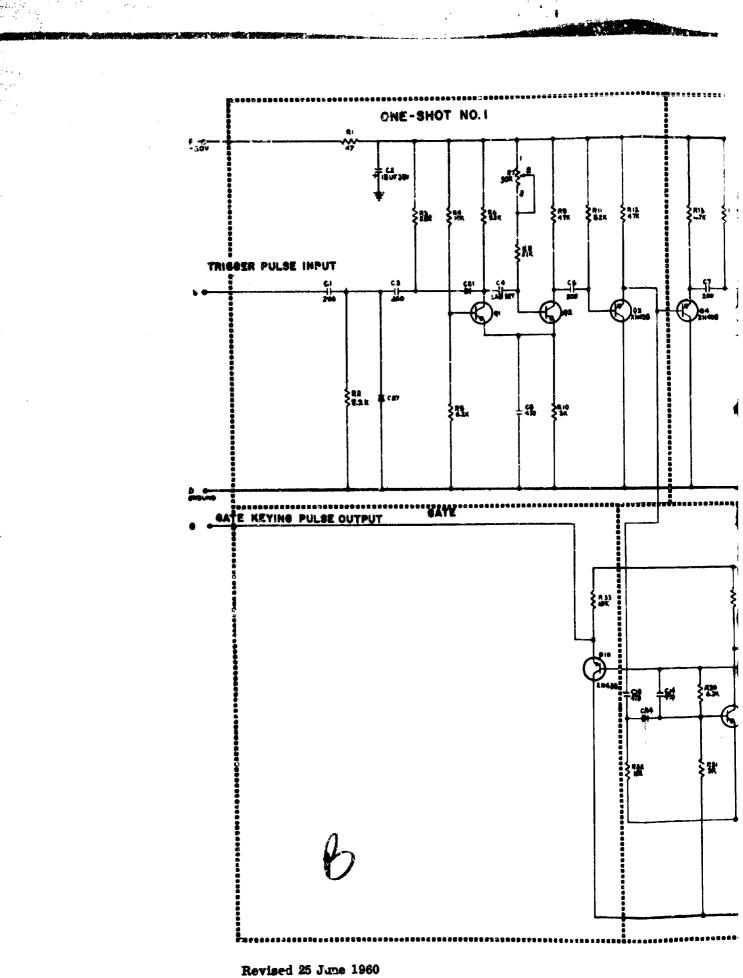

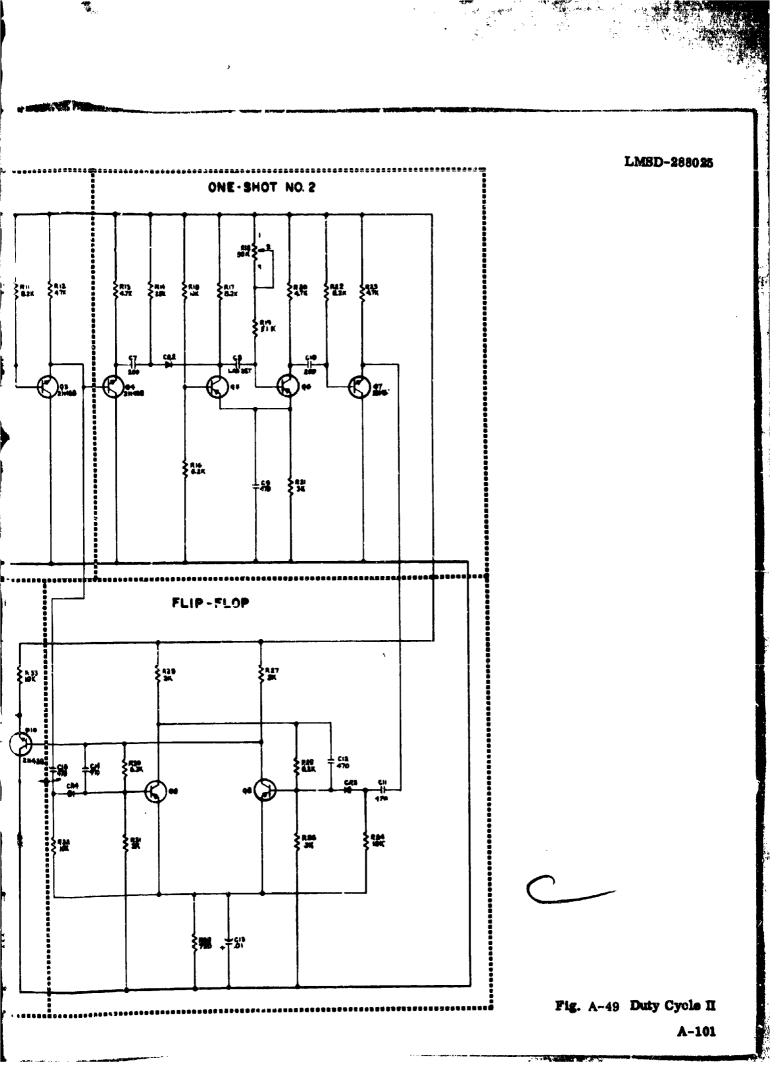

| A-49         | Duty Cycle II                                          | A-101         |

| A-50         | Data Sync Delay Record, G-A                            | A-103         |

| <b>A-5</b> 1 | DC Reference Filter                                    | A-105         |

| A-5 ?        | Sample and Hold                                        | <b>A</b> -107 |

| A-53         | Plus/Minus 10-Volt Regulator                           | <b>A</b> -109 |

| A-54         | Frame Sync Delay Reproduce, G-A                        | <b>A-111</b>  |

| A-55         | Test Signal Generator                                  | A-113         |

xvi

LOCKHEED AIRCRAFT CORPORATION

tite tos -i an atis.

I.MSD-288025

# Section 7 THEORY OF O<sup>¬</sup>ERATION

### 7.1 INTRODUCTION

1. 1

ĮĮ

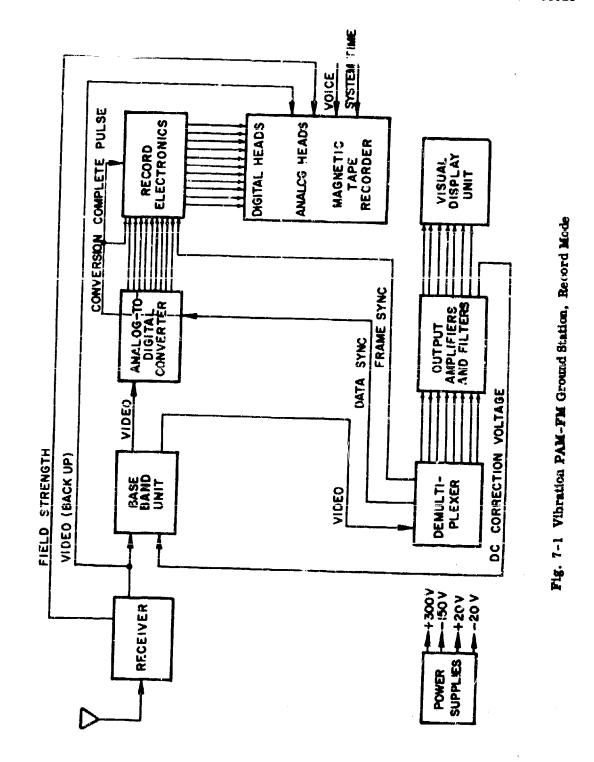

The purpose of the PAM-FM Ground Station is to receive, process, record, and present for on-line, real-time readout PAM-FM telemetered information from a vehicle. Certain Ground Station installations are capable of reproducing the recorded information for delayed readout on visual-display equipment. The Ground Station consists of a Receiver, Base Band Unit, Demultiplexer, Digitizer (Datrac), Record and Reproduce Electronics, a Magnetic Tape Recorder, Sample and Hold Output circuitry, and in the case of Vibration operation, a Visual Display Unit (Visicorder).

The input to the receiver of the Ground Station is a PAM-FM signal. The receiver output is an amplitude-modulated pulse train proportional to the pulse train delivered to the vehicle transmitter by the vehicle multiplexer. This pulse train is amplified, band-limited, and delivered to the Datrac for digitization. Each pulse of the pulse train, including the sync intervals, is digitized into a nine-bit binary word and dalivered to the Magnetic Tape Recorder for parallel recording in Non-Return-to-Zero (NRZ) form. The pulse train is also delivered to the Demultiplexer for separation into individual channels corresponding to the channels of the vehicle multiplexer. The information from the Demultiplexer is used for real-time readout on visual display equipment.

In the reproduce mode of operation, the recorded binary words are delivered to the Datrac for conversion to analog form. This analog pulse train is delivered to the Demultiplexer for separation into individual channels corresponding to the channels of the vehicle multiplexer. The information from the Demultiplexer is then used for delayed readout on visual display equipment. The Visual Display Unit (Visicorder)

7-1

LOCKHEED AIRCRAFT CORPORATION

1.

li

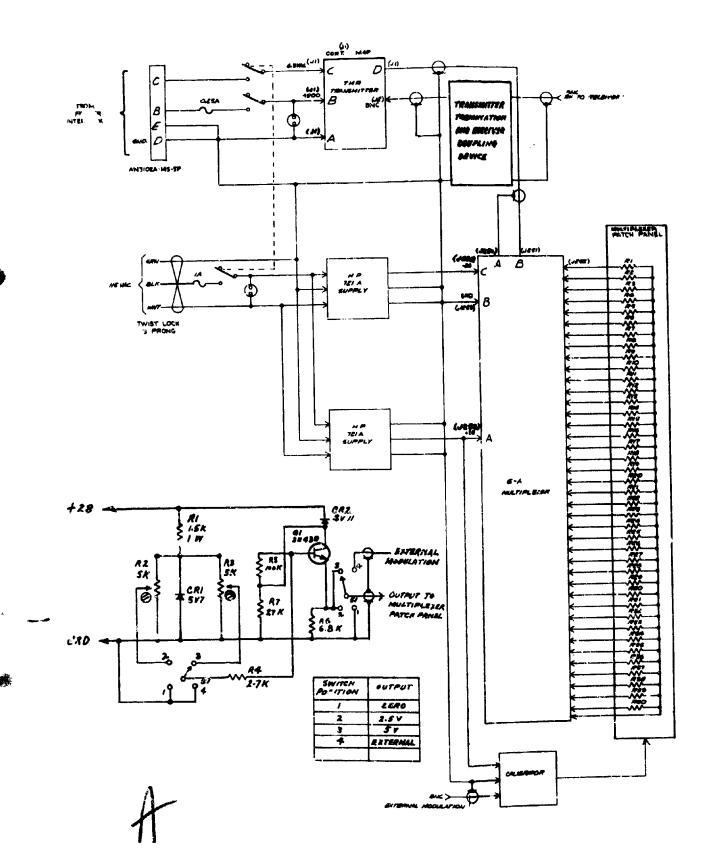

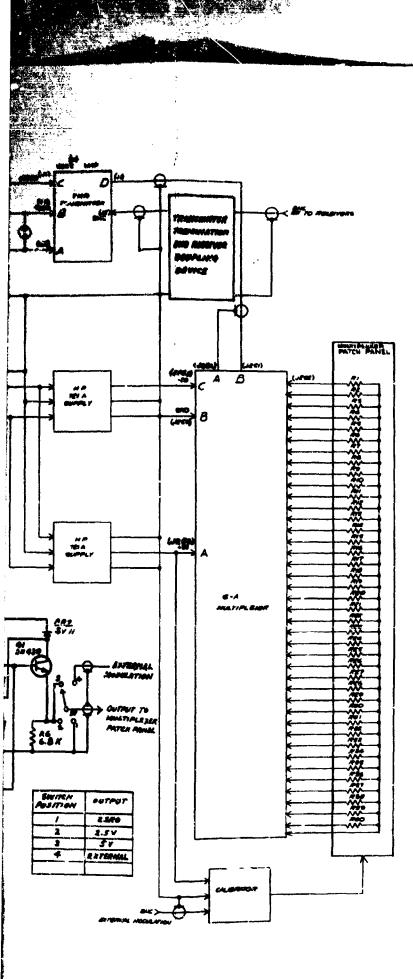

for Vibration is included at certain installations as a part of the Ground Station. Visual display equipment for G-A is not included as a part of the Ground Station and is not discussed in this manual. Block diagrams illustrating the signal flow in record and reproduce modes of operation for the Vibration and G-A systems are shown in Figs. 7-1, 7-2, 7-3, and 7-4.

Since two data links, Vibration and G-A, are included in this Ground Station manual, characteristics peculiar to each are described briefly in paragraphs 7.1.1 and 7.1.2. The theory of operation for Vibration is described in detail in paragraph 7.2, and for G-A in paragraph 7.3. Procedural instructions for maintenance are detailed in Section 8.

### 7.1.1 Vibration

The Vibration data link is a PAM-FM communication system so arranged that it can operate with seven high-frequency data channels with a bandwidth of 2000 cps each or with six high-frequency data channels with a bandwidth of 2000 cps each and seven subcommutated data channels with a bandwidth of 250 cps each. This system has a sampling rate of 40,000 samples per second and a 50 percent duty cycle. In addition to the data channels, there is a subframe sync channel and an alternating frame sync. This alternating frame sync channel provides additional reliability as well as zero data alibrate.

Channel 8 operates as a high-frequency information channel without a sync interval.

With a basic clock rate of 40 kc, an information pulse occurs every 25 microseconds. A complete cycle, going through eight permutations of the subcommutated channel, requires 1600 microseconds. During this 0.0016-second period, each subcommutated

7-2

#### LOCKHEED AIRCRAFT CORPORATION

7-3

s,

LOCKHEED AIRCRAFT CORPORATION

2

i

Ţ

1

17 1 1

E

L

U

Ĺ

1

ì

MISSILES and SPACE DIVISION

Sec. 1

LOCKHEED AIRCRAFT CORPORATION

(i,j)

ц. "<sub>Ха</sub>

I

H.

1 40472

Ŀ

1

MISSILES and SPACE DIVISION

AND AND A

LMSD~288025

مه ۱۹۹۲

å .,

2

I

|.

ł

Ľ

Ĩ

Fig. 7-4 C.-A PAM-FM Ground Station, Rep. oduce Mode

7 - e

LOCKHEED AIRCRAFT CORPORATION

篦

Ž

<del>ي بي</del>ند در در

channel will produce one bit of information at a rate of 625 samples per second, and each high-frequency channel will produce eight bits of information at a rate of 5000 samples per second. There are eight information pulses (one frame) every 200 microseconds. Each main channel is equally spaced in time, and each subcommutated channel is equally spaced in time.

A typical Vibration pulse train (Fig. 7-5) has these characteristics with respect to Demultiplexer input:

- Refe ence level of 0 volts (sync interval)

- Minimum data level of 1.5 volts (corresponding to -2.5-volt input to the vehicle multiplexer)

- Calibrate pulse level of 4, 0 volts (corresponding to 0-volt input to the vehicle multiplexer)

- Maximum data level of 6.5 volts (corresponding to +2.5 volt input to the vehicle multiplexer)

### 7.1.2 G-A

The G-A data link is a PAM-FM communication system arranged to have 29 channels with a bandwidth of 200 cps each and seven channels with a bandwidth of 25 cps each. Two additional 200-cps channels and an additional 25-cps channel are used for ~, achronization. This PAM information has a composite sampling rate of 16,000 samples per second and a 50-percent duty cycle. By the use of a subcommutated channel, the G-A system handles 36 channels of information. Of these, 29 are highfrequency, or direct data channels, and seven are low-frequency, or subcommutated data channels.

With the basic clock rate of 16 kc, an information pulse occurs every 62.5 microseconds. A complete cycle, going through the eight permutations of the subchannel, requires 16,000 microseconds. During this 3.016-second period, each subcommutated channel will produce one bit of information. the rate of 62.5 stimples per second,

7-8

MISSILES and SPACE DIVISION

LOCKHEED AIRCRAFT CORPORATION

LM8D-288025

and each high-frequency channel will produce eight bits of information at a rate of 500 samples per second. There are 32 information pulses (one frame) every 2000 microseconds. Each main channel is equally spaced in time, and each subcommutated channel is equally spaced in time.

The 0- to 5-volt data is superimposed on a 1.5-volt pedestal. Thus, the peak data amplitude is approximately three-quarters of the peak PAM signal amplitude. Synchronization channels have no pedestal, but appear at the baseline level.

Channels 1 and 9 are reserved for main channel sync intervals. Channel 32 is subcommutated into eight channels. Of these, Channel 32.1 is the subcommutated sync interval and Channels 32.2 through 32.8 are subcommutated data channels.

The composite pulse train is band-limited in the vehicle equipment to 35.2 kc by a single-pole filter and is further band-limited on the ground (in the Noise Filter) by another single-pole filter with a cutoff frequency of 35.2 kc.

A typical G-A composite pulse train (Fig. 7-6) has these characteristics with respect to Demultiplexer input:

- Reference level of 0 volts (sync interval)

- Minimum data level of 1.5 volts (corresponding to 0-volt input to the vehicle multiplexer)

- Maximum data level of 6.5 volts (corresponding to a +5-volt input to the vehicle multiplexer)

7-9

[]

0

LOCKHEED AIRCRAFT CORPORATION

### 7.2 VIBRATION

\$

1

1

Ņ

V

T

I

1

### 7.2.1 Receiver

Input to the Vibration Ground Station is received at a modified Nems-Clarke 1412 Telemetry Receiver as a PAM-FM signal. After the FM signal has been demodulated, three signals are delivered to other equipment at the station. A dc-coupled PAM signal is delivered to the Base Band Unit at an average level of approximately +6 volts. A field strength signal is delivered directly from the receiver to the FM electronics of the Magnetic Tape Recorder for recording on analog track 14. An ac-coupled signal, to be used as a backup for the digital recording, is delivered through an auxiliary jack to the analog electronics of the Magnetic Tape Recorder for recording on analog track 11. The modifications to the Nems-Clarke 1412 Telemetry Receiver provide a dc-coupled output near ground potential and were made to achieve compatibility with the PAM-FM Ground Station in the following manner:

- To provide dc-coupled and ac-coupled video with the phase opposite to that provided by the unmodified receiver

- To provide video with a level independent of any readily accessible adjustment

This modification was accomplished by bypassing the video amplifier and obtaining an output signal directly from the cathode of the FM discriminator amplifier (V101). A schematic diagram of the modifications is shown in Fig. A-1. Theory of operation and operating and maintenance procedures are described in <u>Instruction Manual for</u> <u>Model 1412 Telemetry Receiver</u>, Nems-Clarke, Inc., Silver Spring, Maryland.

7.2.2 Base Band Unit, Record Mode

The purpose of the Base Band Unit is to

• Amplify the signal from the receiver and provide three separate output signals, each of a different level and isolated from one another

7-11

LOCKHEED AIRCRAFT CORPORATION

[]

li

5

D

Π

$\Box$

Π

E

Ľ

I

[]

IJ

D

C

U

- Insert correct d-c reference level into two of the three output signals

- Limit the bandwidth of the PAM output signals without introducing excessive crosstalk

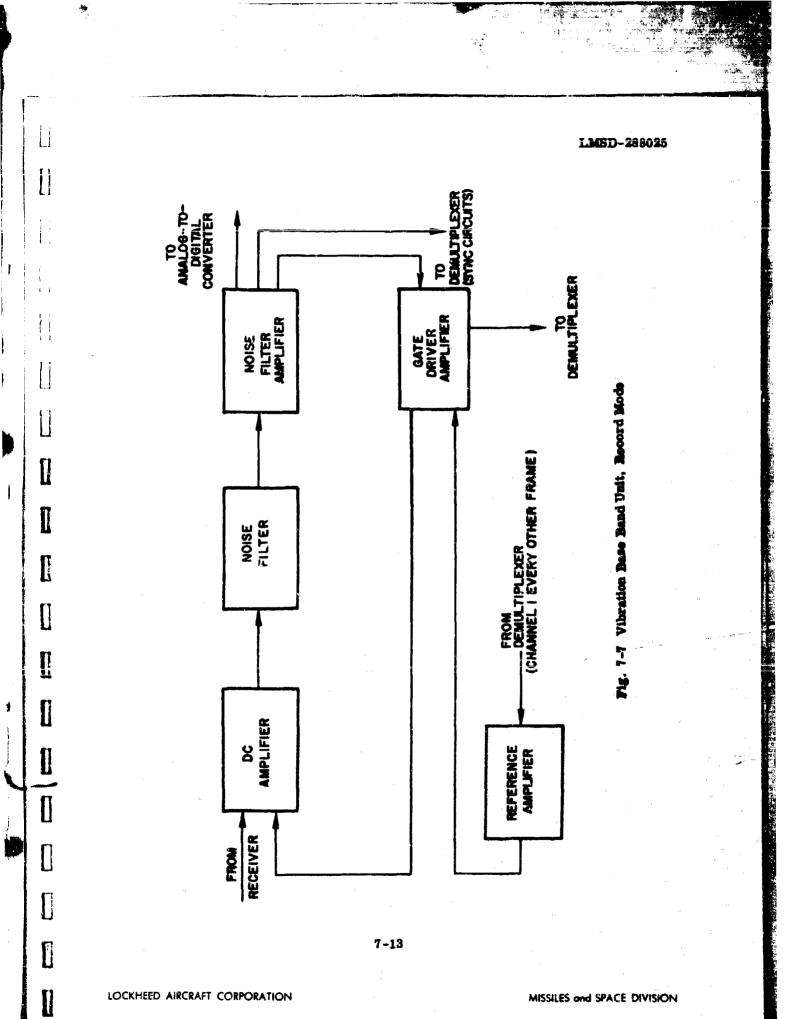

A block diagram of the Vibration Base Band Unit in the record mode is shown in Fig. 7-7.

The three output signals of the Base Band Unit are (1) a 19-volt peak-to-peak signal for the Analog-to-Digital Converter (Datrac), (2) a 7-volt peak-to-peak signal for the Demultiplexer data gates, and (3) a 15-volt peak-to-peak signal for the Demultiplexer sync circuits.

The 19-volt peak-to-peak signal for the Datrac must be referenced so that the minimum peak is -9.5 volts. The 7-volt peak-to-peak signal for the data gates is referenced so that zero output of the interpolation filters of the display circuitry corresponds to zero data, i.e., the minimum peak is approximately -1.5 volts. The 15-volt peak-to-peak signal for the sync circuits is not referenced and is a-c coupled.

Since the Vibration PAM signal has a 40-kc pulse repetition rate, it must be considered a high-speed system. Accuracy requirements approach two percent. The high repetition rate and accuracy requirements dictate the use of a finite memory type of filter. Finite memory filters can be adjusted so that practically zero crosstalk is introduced into the system. The filter is adjusted so that the output reaches full amplitude of the input pulse during the time of the pulse and decays to zero by the time the peak value of the succeeding pulse is reached. The accuracy of the adjustment determines the amount of crosstalk introduced by the finite memory filter.

Two signals flow through the Base Band Unit. One is the PAM pulse train, the other is the d-c reference feedback correction voltage that is derived from a portion of the pulse train.

Revised 25 May 1960

7-12

LOCKHEED AIRCRAFT CORPORATION

LOCKHEED AIRCRAFT CORPORATION

MISSILES and SPACE DIVISION

1. 30 A.C.

#### LMBD-288025

ł i

IJ

H

I

Į į

[]

Ũ

The signal from the receiver, which is approximately 1.4 volts peak-to-peak in amplitude, enters the DC Amplifier where it is amplified approximately 10 times without being inverted. This amplifier is composed of direct-coupled circuits. A suitable means of offsetting positive bias voltage from the receiver is included.

The conjust of the DC Amplifier, now at a level of approximately 14 volts peak-topeak, is fed into the Noise Filter described above. Here the signal-to-noise ratio of the FAM pule train is improved, and approximately 3 volts of negative offset voltage are added to the output signal.

This signal is definered to the Noise Filter Amplifier at approximately 4 volts peakto-peak because of attenuation in the Noise Filter. The signal is then amplified so that the Noise Filter Amplifier output to the Datrac is 19 volts peak-to-peak. An adjustment called the Overall Gain is included in this amplifier to set the desired level. An additional adjustment to correct the d-c level to -9 ( $\pm 0.25$ ) volts is also included in the Noise Filter Amplifier. This signal can be routed through the Reference Voltage Opti. Clamp circuit if the Demultiplexer should fail to deliver the correct d-c reference level voltage.

At this point the PAM pulse train is divided into three outputs. One output is the 19volt peak-to-peak signal the Datrac, another is the 15-volt peak-to-peak signal to the Demultiplexer sync circuits, and the third is the dc-coupled signal to the Gate Driver Amplifier.

The Gate Driver Amplifier is used to attenuate the 19-volt peak-to-peak signal to a 7-volt signal and supply a low source impedance to drive the data gates. A d-c offset adjustment is incorporated to adjust the minimum peak (sync interval) to approximately -1.5 volts. Incorporated in the Gate Driver Amplifier is a relay activated by the Record-Reproduce switch in the Monitor Panel so that the input to the data gates by way of the Gate Driver Amplifier can be routed from the Datrac or the Noise Filter Amplifier, depending on the mode of operation.

7-14

LOCKHEED AIRCRAFT CORPORATION

The d-c reference correction voltage originates in the Demultiplexer where the calibrate pulse is sampled by the Zero Data Selector and smoothed through a 1-kc low-pass filter. This signal is then delivered to the Reference Amplifier of the Base Band Unit where the d-c error voltage is amplified approximately 2500 times and delivered to a single-pole, R-C section, low-pass filter with a cutoff frequency of 2 cps. This filter is physically located in the Gate Driver Amplifier. The d-c correction voltage is switched by a relay in the Gate Driver Amplifier to a differential input of the DC Amplifier in the record mode or to a differential input of the Gate Driver Amplifier in the reproduce mode.

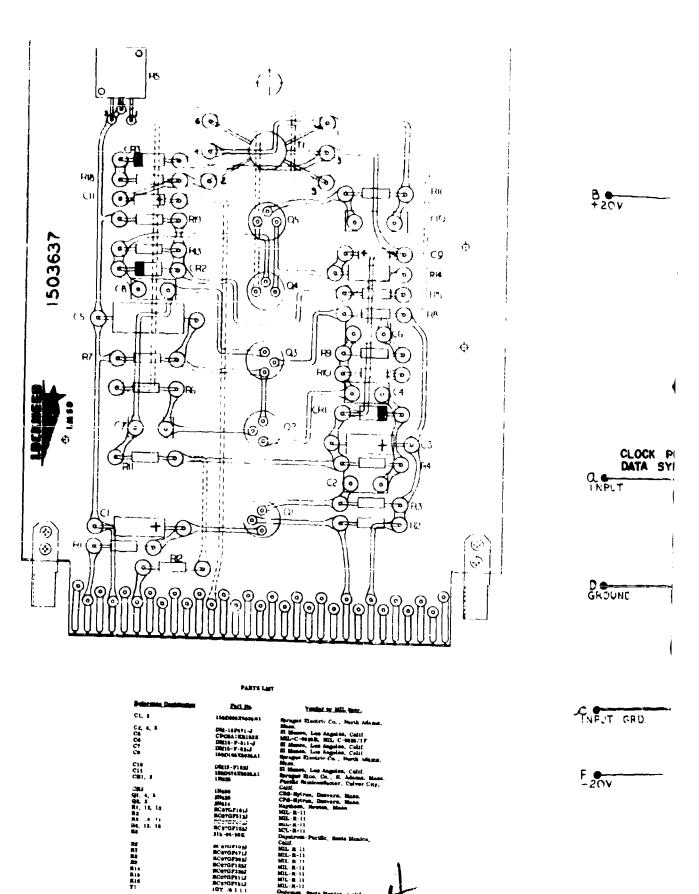

7.2.2.1 DC Amplifier

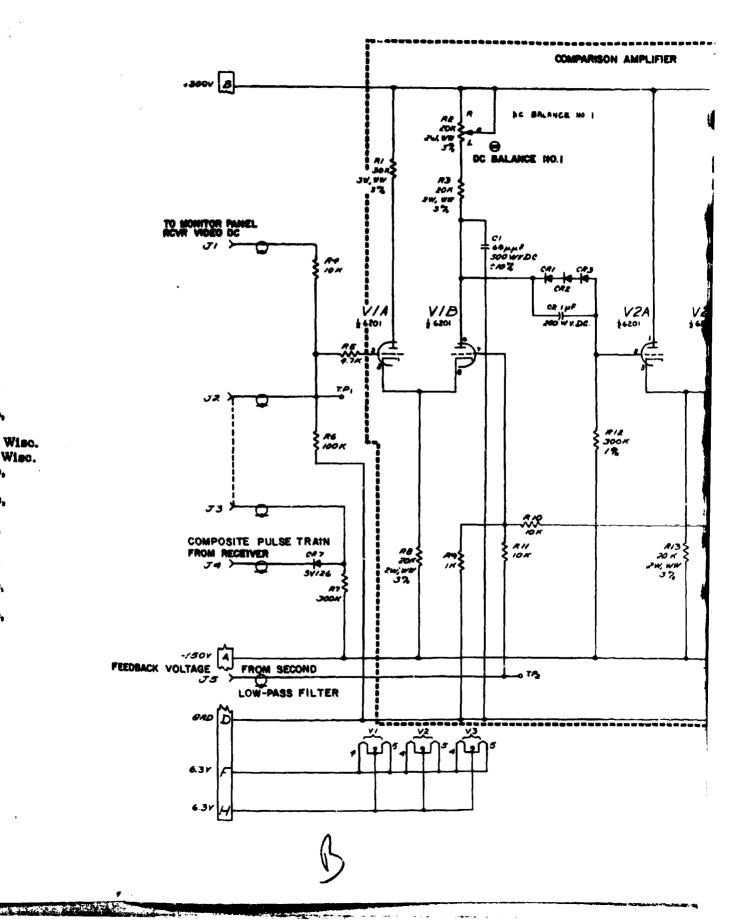

The purpose of the DC Amplifier is to amplify the incoming PAM signal approximately 10 times and establish a d-c reference level of approximately -2 ( $\pm$  2) volts. These functions are performed by using three dual-triode (6201) vacuum tubes and their associated components. The first two cathode-coupled triodes (V1 and V2) act as a comparison amplifier that amplifies the difference of the signals appearing on grids 2 and 7 of tube V1. The third cathode-coupled dual triode (V3) acts as a parallel cathode follower and furnishes a low output impedance to the Noise Filter. Zener diodes are used to correct the d-c offset throughout the amplifier. A schematic diagram of the DC Amplifier is shown in Fig. A-2.

Two inputs to the DC Amplifier are provided. One input is the PAM pulse train from the receiver; the second is the d-c reference level from the second low-pass filter in the d-c reference feedback loop.

The PAM signal from the receiver is picked up at jack J4 at a level of approximately +6 volts dc. It is passed through Zener coupling diode CR7 where the level is reduced to approximately zero volts dc. This signal is then applied to grid 2 of tube V1A. At the same time, the signal input from the Reference Amplifier, via the second low-pass filter, is applied to grid 7 of tube V1B through a network composed of resistors R9, R10, and R11.

7-15

LOCKHEED AIRCRAFT CORPORATION

I

Π

In order to exercise adequate control over the d-c offset voltage, it is necessary to balance the plate current being applied to VIA and VIB, the first stage of the amplifier. This is accomplished by means of potentiometer R2 (DC Balance no. 1). While this adjustment is being made at R2, the input from the Reference Amplifier is disconnected at jack J5. Resistor R2 is adjusted so that the sync interval (absence of a data pulse) is approximately -2 (\* 2) volta do as observed at test point TP3.

The output of V1B is passed wrough an offest voltage control network composed of diodes CR1, CR2, and CR3 that reduces the d-c voltage by 180 volts ( $\pm$  10 percent). The signal is then applied to grid 2 of V2A. The cathode of V2A is coupled to the cathode of V2B, which is next to receive the signal. At the same time, there appears on grid 7 of V2B the signal from the output of V3, a part of the amplifier's internal feedback circuit.

The output from the plate of V2B is passed through a second offset voltage control network composed of diodes CR4, CR5, and CR6 which reduces the d-c voltage by 180 volts ( $\pm$  10 percent). Capacitors C2 and C3 are used to suppress the high-frequency noise generated in the two Zener diode strings CR1, CR2, and CR3; and CR4, CR5, and CR6.

The signal is then applied in parallel to grids 2 and 7 of V3A and V3B, the parallel cathode follower. The output of this parallel cathode follower is delivered through jack J6 to the Noise Filter. At the same time, this output is fed back to the grids of V2B and V1B by means of the feedback resistors R9, R10, R15, and R16. Feedback resistors R9 and R10 are used to control the overall gain of the DC Amplifier to approximately 10.

There are three test points in the DC Amplifier. Test point TP1 provides a sampling point for the input from the receiver after passing through the 6-volt Zener diode CR7. Test point TP2 provides a sampling point for the input from the Reference Amplifier. Test point TP3 provides a sampling point for the output of the amplifier. The input

7-16

LOCKHEED AIRCRAFT CORPORATION

from the receiver, after passing through the 6-volt Zener diode CR7, is also delivered to the Monitor Panel through jack J1 as the RCVR VIDEO DC position on Switch A and Switch B.

A jumper between jacks J2 and J3 is normally used with the DC Amplifier. Should an occasion arise when operation with the composite pulse train from some source other than the receiver is desired, however, the jumper could be removed and the input applied to jack J2, provided the d-c level is correct.

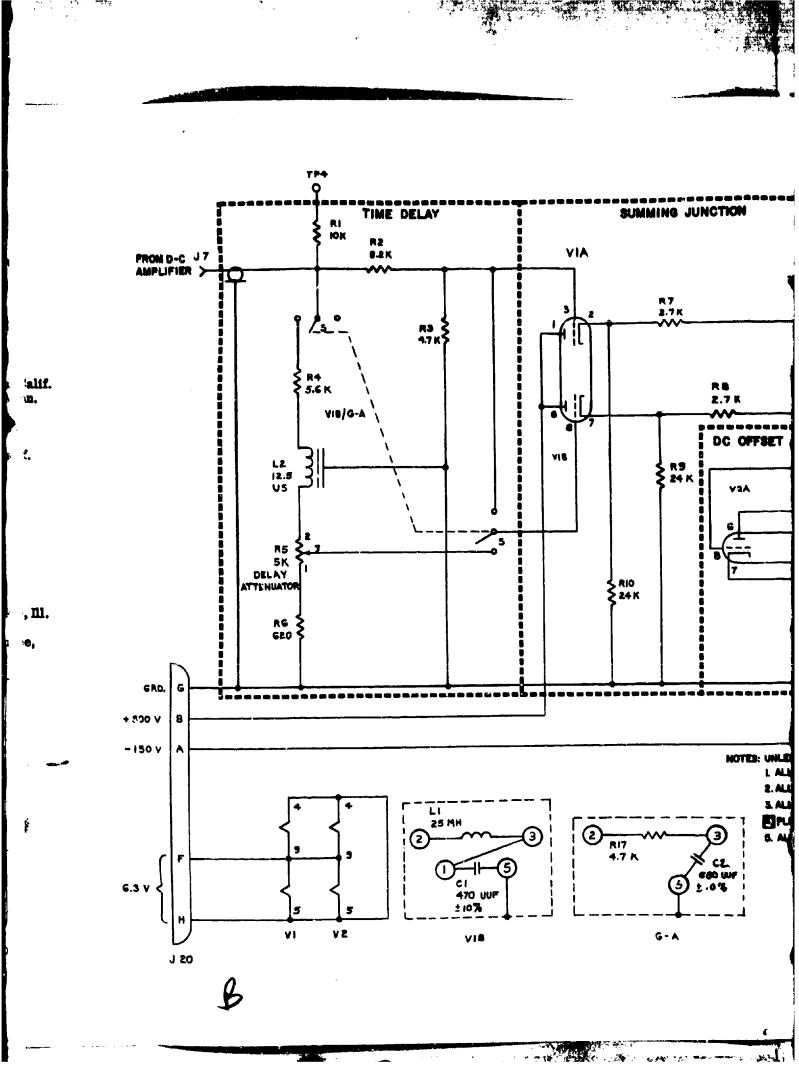

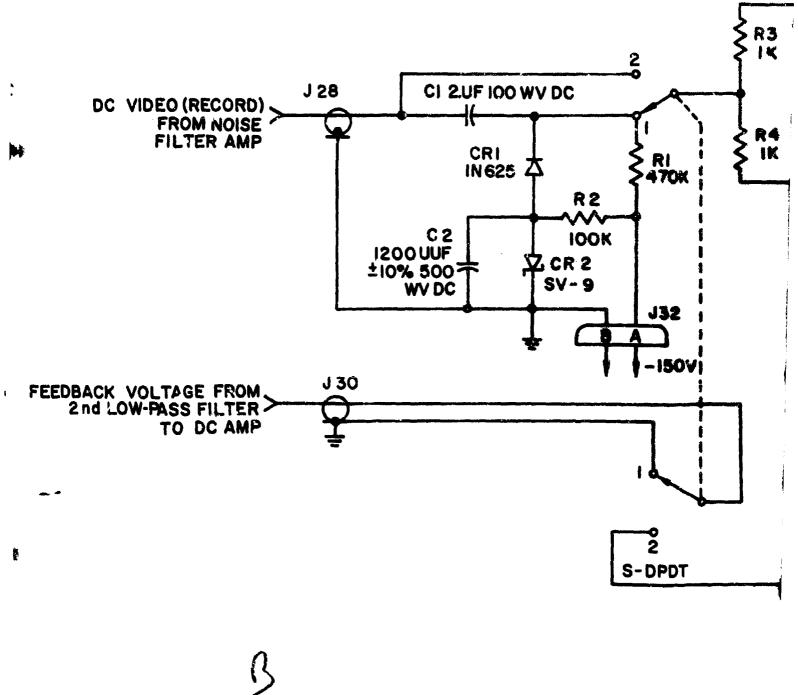

7.2.2.2 Noise Filter

The purpose of the Noise Filter is to improve the signal-to-noise ratio of the composite pulse train without introducing excessive crosstalk. It is composed of a time delay circuit, a summing junction, a d-c offset adjustment circuit, and an output circuit. Internal switching and separate plug-in output circuits permit use with both Vibration and G-A Ground Stations. Input to the Noise Filter from the DC Amplifier is at jack J7 and its output to the Noise Filter Amplifier is at jack J8. A schematic diagram of the Noise Filter, including circuits used in both Vibration and G-A operation, is shown in Fig. A-3.

With the SYSTEM switch on the Monitor Panel set at the VIB (Vibration) position, and a Vibration plug-in unit in place, all Noise Filter components are in operation. The output circuit is a single, series L-C section resonant at the composite pulse train pulse repetition frequency of 40 kc. The delay of the time-delay circuit is one-half of the repetition frequency period, or 12.5 microseconds. The filter is adjusted so that the output reaches full amplitude during the time of one pulse and decays to zero during the time the next pulse is sampled by the Datrac. The accuracy of this adjustment determines the amount of crosstalk introduced by the Noise Filter, which can approach zero.

The signal is delivered to grid 3 of a dual cathode follower composed of vacuum tube V1 and resistors R9 and R10. The signal is also applied to grid 8 of V1 after a

Revised 25 May 1960

E

It

Ł

1

12. 5-microsecond delay produced by delay line L2. Variable resistor R5 of the divider composed of resistors R5 and R6 is used to control the amplitude of the delayed signal to compensate for the attenuation of the undelayed signal introduced by resistors R2 and R3 and by the series-resonant output circuit. The signals present at grids 3 and 5 are then summed by resistors R7 and R8 and applied to the series-resonant circuit composed of L1 and the parallel combination of capacitors C1 and C3. Capacitor C3 is a small variable capacitor that is used to tune the series-resonant circuit to the pulse repetition frequency. The output of the Noise Filter is the voltage developed across capacitors C1 and C3.

D-C offset adjustment is accomplished by a circuit composed of tube V2 and associated components. By varying the operating point of tube V2 with the DC Offset no. 1 control, resistor R13, d-c current flowing out of the junction of resistors R7 and R8 can be changed, and the resulting I-R drop becomes offset voltage. This adjustment is made so that there is  $3.5 (\pm 0.5)$  volts offset between jacks J7 and J8. Offset conditions should always be checked when changing from one system (Vibration or G-A) to the other.

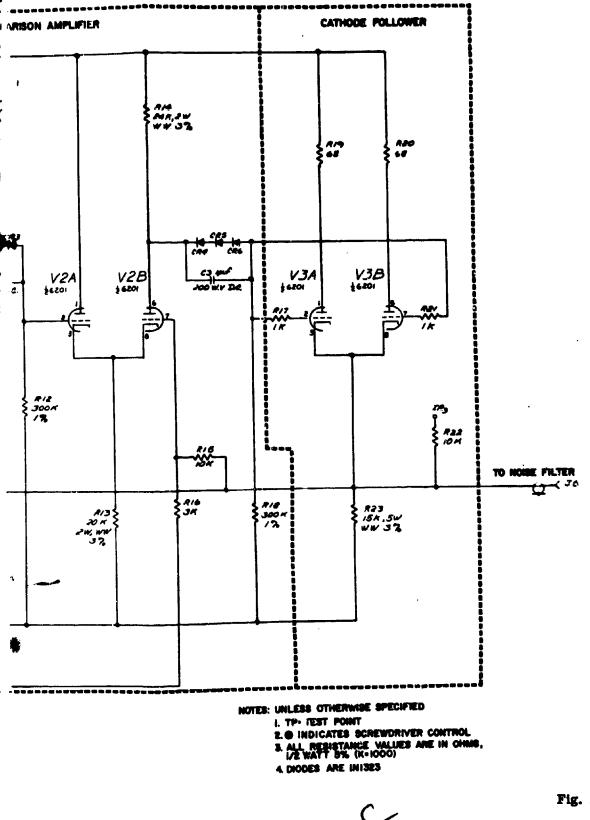

7, 2, 2, 3 Noise Filter Amplifier

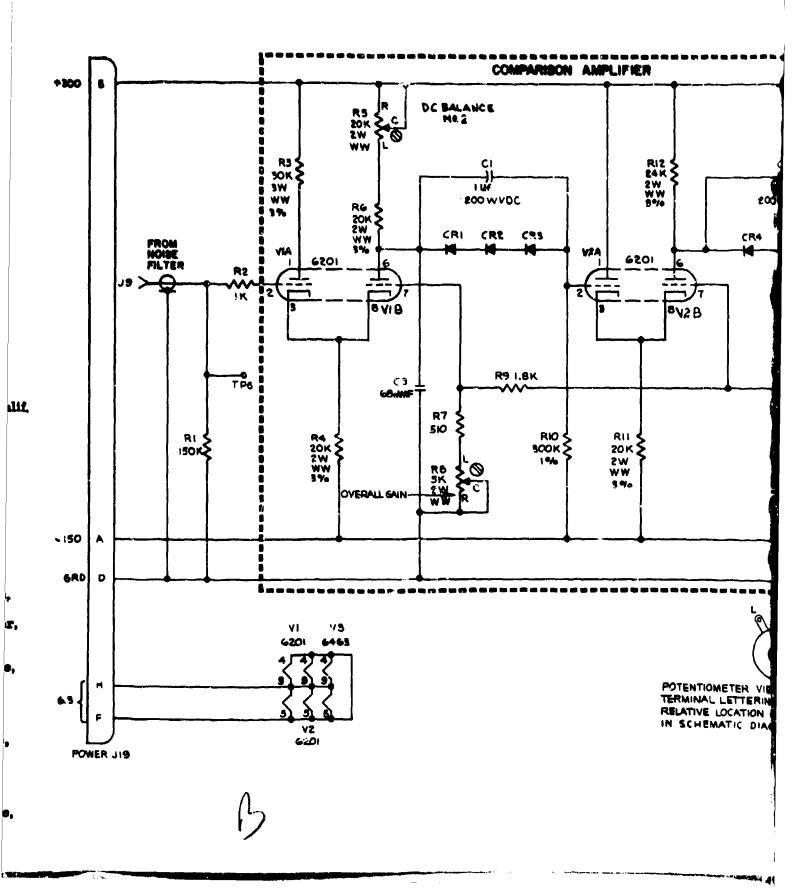

The purpose of the Noise Filter Amplifier is to amplify the signal delivered by the Noise Filter so that the peak-to-peak voltage with full modulation is  $19(\pm 1)$  volts. The signal level must be such that the sync level (absence of data pulse) is -9.5( $\pm 0.25$ ) volts. These functions are performed by using two dual-triode (6201) vacuum tubes and one dual-triode (6463) vacuum tube, and their associated components. The first two cathode-coupled triodes (V1 and V2) act as a comparison amplifier that smplifies the difference of the signals appearing on grids 2 and 7 of V1. The third cathode-coupled triode (V3) acts as a parallel cathode follower and furnishes a low output impedance. Zener diodes are used to correct the d-c offset throughout the amplifier. A schematic diagram of the Noise Filter Amplifier is shown in Fig. A-4.

The signal is delivered to the Noise Filter Amplifier at jack J9 and applied to grid 2 of V1. At the same time, the signal appears at grid 7 of V1 as feedback from cathode follower V3. Plate current to V1 is balanced by means of DC Balance no. 2. In order to make this adjustment, it is necessary to disconnect the input signal at jack J9. Test point TP8 should go to ground potential when the adjustment is properly made.

The output of plate 6 of tube V1 is delivered to grid 2 of V2, the second cathode-coupled dual triode, through an offset voltage control network composed of diodes CR1, CR2, and CR3 which reduces the d-c voltage by 180 volts ( $\pm$ 10 percent). Cathode 2 of V2 is coupled to cathode 8, which is next to receive the signal. At the same time, the signal from the output of V3, a part of the amplifier feedback circuit, appears on grid 7 of V2.

The output from plate 6 of V2 is passed through a second of set voltage control network composed of diodes CR4, CR5, and CR5 which reduces the d-c voltage by 180 volts ( $\pm$ 10 percent). Capacitors C1 and C2 are used to suppress the high-frequency noise generated in the two Zener diode strings.

The signal is then applied to grid 3 of cathode follower V3. The output of this half of V3 appears on cathode 2. This output is delivered to grid 7 of V2 and grid 7 of V1 through resistors R7, R8, R9, and R13, which act as voltage dividers of a feedback circuit within the Noise Filter Amplifier. This output is also coupled to jacks J11 and J12. At the same time, a part of this output is delivered to grid 8 of V3 through resistor R17 and variable resistor R18. The output of this half of V3 appears on cathode 7 and is ac-coupled to the Sync Separator in the Demultiplexer through jack J10. Capacitor C4 acts as a blocking capacitor to prevent high voltage from entering the Demultiplexer.

There are two adjusting points in this circuit in addition to DC Balance no. 2, which was described earlier. Both of these points, resistors R8 and R18, are adjusted with the input from the Noise Filter connected to jack J9. Resistor R8 (Overall Gain) is

7-19

Ē

Ĩ

i E L

Ŀ

1

set so that the peak-to-peak voltage with full modulation is 19  $(\pm 1)$  volts at test point **TPS.** It is advisable to recheck the adjustment of DC Balance no. 2 after resistor R8 is adjusted to assure that ground potential is present without signal input. Variable resistor R18 (a-c gain) is adjusted so that the peak-to-peak voltage with full modulation is 15  $(\pm 2)$  volts at test point TP7.

The output at jack J11 is connected to the Reference Voltage Optional Clamp where a switch either delivers the signal directly to the Datrac and Gate Driver Amplifier or clamps it to a d-c reference voltage before delivery to the Datrac and Gate Driver Amplifier.

There are three test points in the Noise Filter Amplifier. Test point TP6 furnishes a sampling point for the input from the Noise Filter; test point TP7 furnishes a sampling point to the a-c video output to the Demultiplexer; and test point TP8 furnishes a sampling point to the d-c video output to the Reference Voltage Optional Clamp.

The Noise Filter Amplifier has three outputs. One output is delivered to the d-c coupled Analog-to-Digital Converter. The signal is also fed ac-coupled to the sync circuits in the Demultiplexer. Peak-to-peak amplitude of this output is 15 ( $\pm 2$ ) volts. The third output, which is identical to the output going to the Datrac, is delivered to the Gate Driver Amplifier.

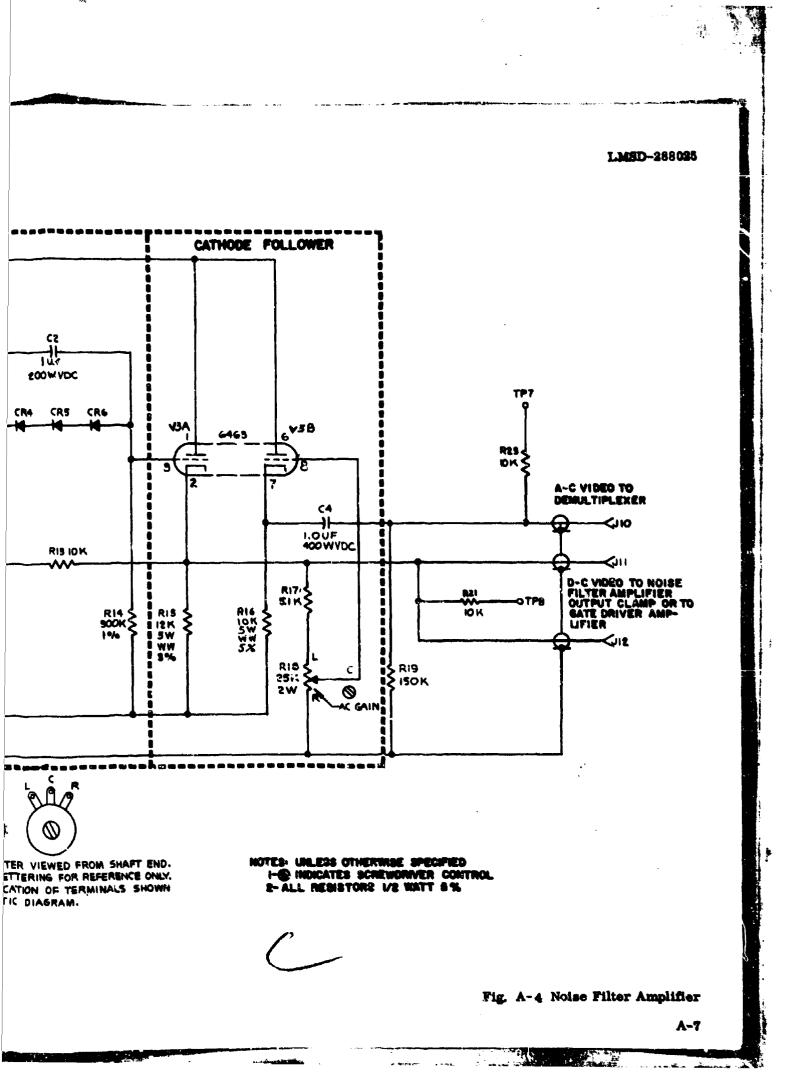

7. 2. 2. 4 Reference Voltage Optional Clamp

A Reference Voltage Optional Clamp circuit is included in all Vibration and G-A Ground Stations with record capabilities. The purpose of the clamp is to increase the reliability of the station in the record mode by allowing the operator an optional method of restoring the correct d-c record level in case the main d-c correction circuit fails. A schematic diagram of the clamp is shown in Fig. A-5.

7-20

The clamp circuit is contained in a 2-3/4 in. by 2 in. box that is mounted on top of the case containing the Reference Amplifier in the Base Band Unit. The switch positions on the clamp box are labeled CLAMP and SERVO. When the switch is in the SERVO position, the clamp is eliminated from the circuit, and the reference level is furnished by the d-c correction circuit. When the switch is in the CLAMP position, the d-c correction circuit is eliminated and the clamp furnishes the appropriate d-c correction level.

The clamp level is fixed at -9 ( $^{\pm}0.5$ ) volts by an SV-9 Zener diode. In order that the d-c record levels remain approximately the same for the CLAMP or SERVO positions, the main d-c correction circuit must be set up to match the clamp level.

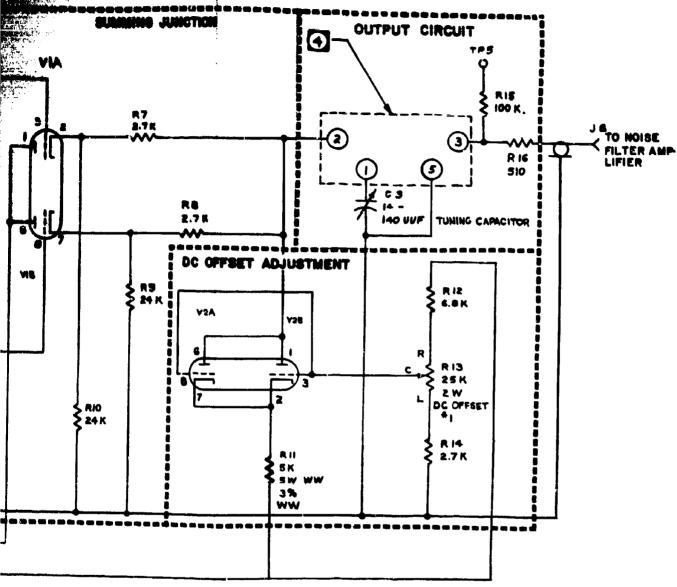

### 7. 2. 2. 5 Gate Driver Amplifier

I

The Gate Driver Amplifier furnishes a gain factor of approximately 0.33 and a d-c voltage offset so that a zero signal at the vehicle multiplexer results in a zero signal at the output of the Demultiplexer. This unit delivers the signal to the Demultiplexer.

This amplifier is made up of a comparison amplifier, a positive peak limiter, a cathode follower, an effset control, and an output clipper. To facilitate switching between the record and reproduce modes of operation, the Reference Amplifier low-pass filter is included as a part of the Gate Driver Amplifier. A schematic diagram of this circuit is shown in Fig. A-6.

In the record mode of operation, the Noise Filter Amplifier furnishes the input to the Gate Driver Amplifier. In the reproduce mode of operation, the Datrac furnishes the input to the Gate Driver Amplifer. The input signal appears at jack J13 or J14, depending on the mode of operation, and is delivered to grid 2 of V1 (a dual-triode vacuum tube. 6201, which acts as a cathode-coupled comparison amplifier) through resistors R1, R2, and R3 which serve as a voltage divider and attenuator. The output of plate 6 of V1 is passed through diode CR1 for offset voltage control, causing the

Revised 25 May 1960

7-21

LOCKHEED AIRCRAFT CORPORATION

#### LM3D-288025

Ī

١l

Π

F

į

Tes.

voltage to drop 180 volts ( $\pm$ 10 percent). Capacitor C3 suppresses the high-frequency noise generated by diode CR1. The signal is then passed through the positive peak limiter, composed of variable resistor R13 (limiter bias), diode CR2, and capacitor C4, and is delivered in parallel to grids 3 and 8 of cathodes follower V2, a dual-triode (6463) vacuum tube. The output of V2 (cathodes 2 and 7) is passed through a voltage offset adjustment network composed of diodes CR3, CR4, and resistor R18 (DC Offset no. 2). The signal is then delivered to jack J17 through an output clipper composed of diodes CR5 and CR7. This clipper prevents the output to jack J17 from going beyond +10 or -5.6 volts.

Also included in the Gate Driver Amplifier is the second low-pass filter for the d-c reference feedback loop. This filter consists of resistor R4 and capacitors C1 and C2. The input to the filter is from the Reference Amplifier. In the record mode of operation, the filter output is delivered to the differential input of the DC Amplifier. In the reproduce mode of operation the DC Amplifier is not used and the filter output is delivered to the differential input (grid 7 of V1) of the Gate Driver Amplifier through resistors R11 and R14. This unit filters out unwanted frequencies and prevents hunting.

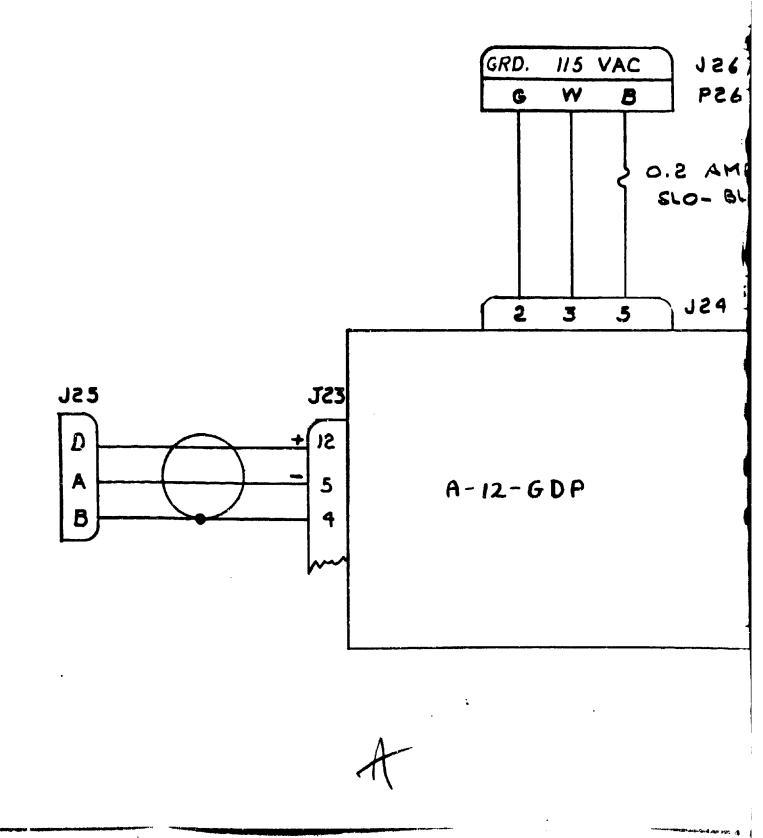

7.2.2.6 Reference Amplifier

The Reference Amplifier has a variable gain from 10 to 2500 to amplify the d-c correction voltage. A gain of 2500 is normally used during operation of the Ground Station in the Vibration mode. The output is delivered first to the second low-pass filter contained in the Gate Driver Amplifier and then to the differential input of the DC Amplifier in the record mode of operation, or to the Gate Driver Amplifier in the reproduce mode of operation.

The circuitry of this amplifier is described in detail in the <u>Handbook of Operating and</u> <u>Maintenance Instructions, A-12 DC Amplifier</u>, supplied with the Ground Station. A schematic diagram of the amplifier is shown in Fig. A-7.

7-22

### LOCKHEED AIRCRAFT CORPORATION

The input to the Reference Amplifier is of a differential type with respect to ground in order to reduce ground loop problems. This input from the 1-ke Filter card in the Demultiplexer appears at jack J25 at approximately 0 volts (within a few millivolts) when the feedback loop is closed. If instability of the video base line is noted, the gain should be reduced until stability is achieved. This instability will be noted at test point TP11 in the Gate Driver Amplifier. Random noise may be present, but it is filtered out by the second low-pass filter in the Gate Driver Amplifier. The output at jack J23 should be 0 ( $\pm 5$ ) volts and must never exceed  $\pm 10$  volts as this level would represent loss of operation of the d-c reference feedback loop. Although no damage to equipment would result with the output approaching these limits of  $\pm 10$  volts, data recovery accuracy of the Ground Station would suffer appreciably.

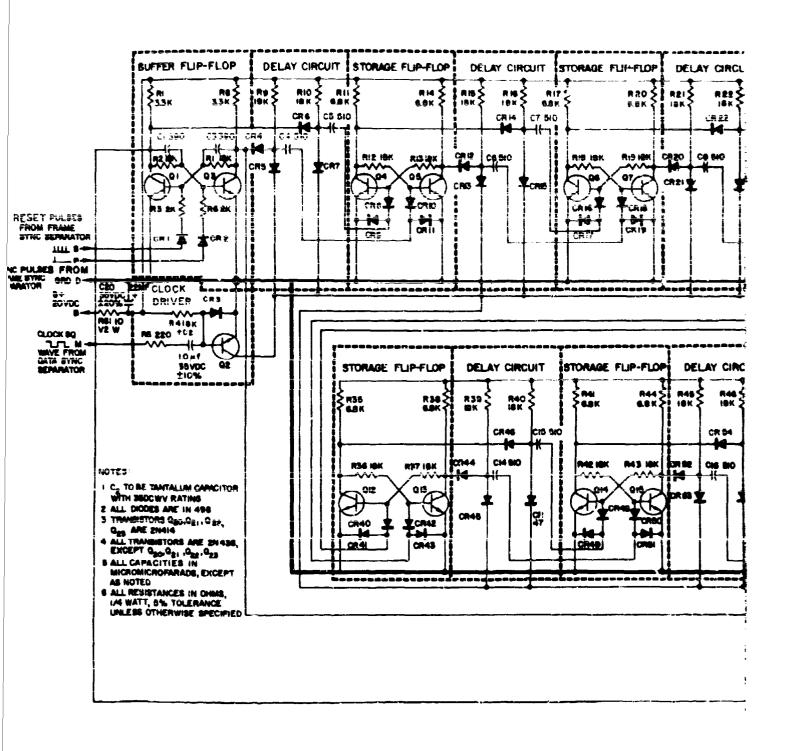

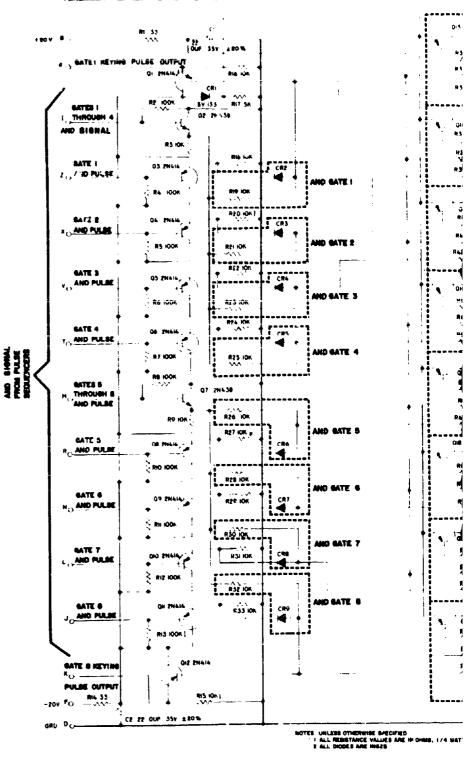

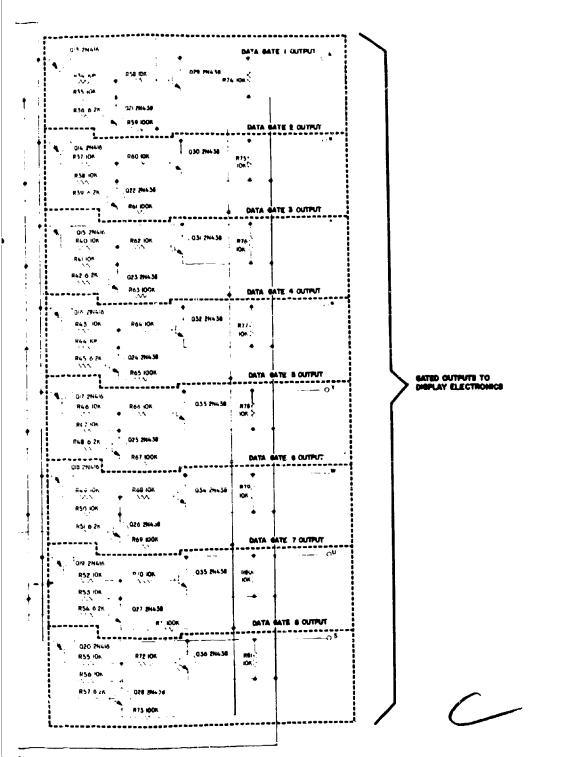

# 7.2.3 Demultiplexer, Record Mode

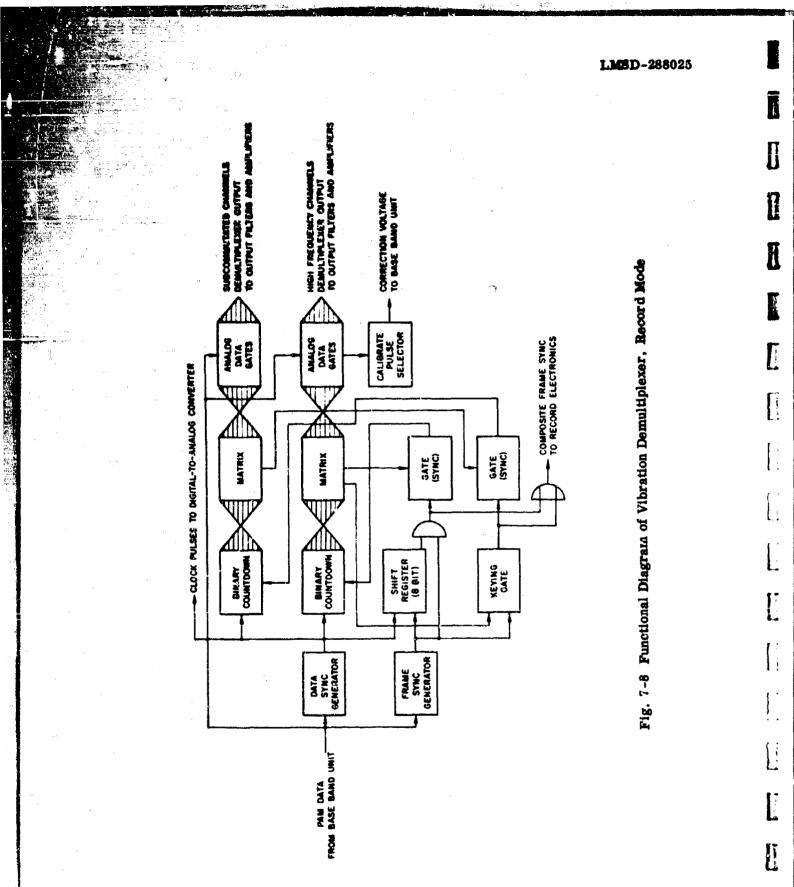

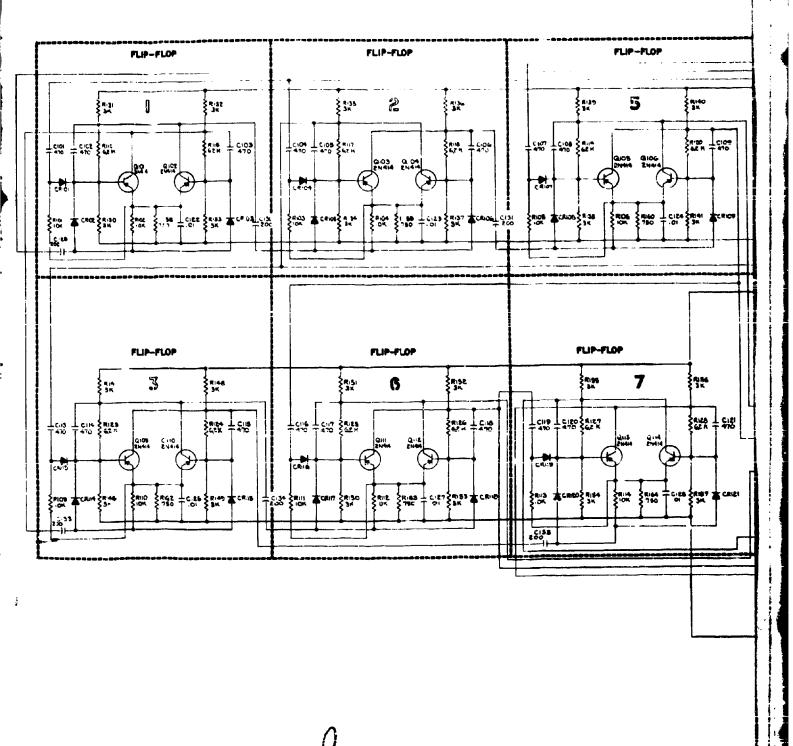

A functional diagram of the Vibration Demultiplexer in the record mode of operation is shown in Fig. 7-8. The three principal functions of the Demultiplexer are: (1) to separate the data sync pulse from the composite data signal for use as a clock pulse for the Demultiplexer and Analog-to-Digital Converter (Datrac) and to generate frame sync pulses from the composite data signal; (2) to open and close the analog gates in sequential fashion in order to separate the composite data signal into separate outputs; and (3) to sample the calibrate pulse that appears on Channel 1 alternately with the sync pulse and send it through a low-pass filter as a d-c correction voltage to the Base Band Unit.

Since the Ground Station is slaved to the vehicle clock, a clock signal must be recovered from the composite pulse train. This is done in the data sync generator where a pulse is generated for every data pulse and sync interval in the PAM pulse train. The phasing can be controlled to give the appropriate time relation between the clock signal thus generated and the analog data pulses from the Base Band Unit.

One output of the data sync generator is used to drive the biggry countdown that produces the square-wave signals used for "ANDing" purposes in the matrices. The

7-23

7-24

# LOCKHEED AIRCRAFT CORPORATION

.

à

1

\$

F

outputs of the matrices are the keying signals for the analog data gates which receive their input in the form of the PAM analog pulse train from the Gate Driver Amplifier in the Base Band Unit. These sequential keying signals to the analog data gates are on separate lines and are connected to the appropriate analog data gates which open and close in correspondence with the keying signals. The "on" time of any one highfrequency data gate is the clock period, or 25 microseconds. The "off" time is one frame minus the clock period, or 175 microseconds. The "on" time for a subcommutated data gate is the same as the "on" for a high-frequency data gate, or 25 microseconds. The "off" time of the subcommutated data gate is eight frames minus one clock period, or 1575 microseconds.

To keep the Demultiplexer in synchronization with the PAM pulse train (that is, to open the appropriate analog data gate when each channel of the PAM pulse train is delivered from the Base Band Unit), a frame synchronization pulse is used. Frame synchronization pulses are generated in the frame sync generator which produces a pulse whenever a pulse is missing in the PAM pulse train. To ensure that this pulse is a valid sync pulse and not a stray pulse as might be generated in the presence of r-f noise interference or a faulty multiplexer, a certain amount of logic is incorporated into the circuitry.

True frame sync occurs on Channel 1 alternately with a calibrate pulse. Therefore, the train of potential sync pulses is delayed exactly eight channels by means of an eight-bit shift register and compared in a logic gate with the potential frame sync pulses being generated by the frame sync generator. This will produce a frame sync pulse output only when the potential frame sync pulse appears on alternate frames. Once apparent frame sync has been established, it is fed into a rate which opens to receive a sync pulse only when one is expected as determined  $t_y$  the high-frequency binary countdown and matrix. When the sync pulse arrives, it closes the gate and blocks any spurious pulses. If the sync pulse does not arrive as expected, the sync gate remains open until sync is again established. This circuit performs the function of blocking periodic and nonperiodic false sync pulses as well as the subcommutated

7-25

1

ł

L. Salar

ayac pulse, which appears as a nonperiodic sync pulse to the high-frequency binary ecurations.

In addition, a subcommutated synchronization pulse is needed to control the subcommutated binary countdown and matrix. This pulse is derived by sampling the output of the frame sync generator only during Channel-8 time by way of a keyed gate that is controlled by the high-frequency binary countdown and matrix. The output of the keyed gate is delivered to a subcommutated sync gate which operat s in the same fashion as the high-frequency gate except that it is controlled by the subcommutated countdown and matrix.

The two signals appearing at the output of the high-frequency and subcommutated sync gates are delivered to the Digital Record Electronics for recording on a single digital track. These signals are combined onto one line by means of an OR gate.

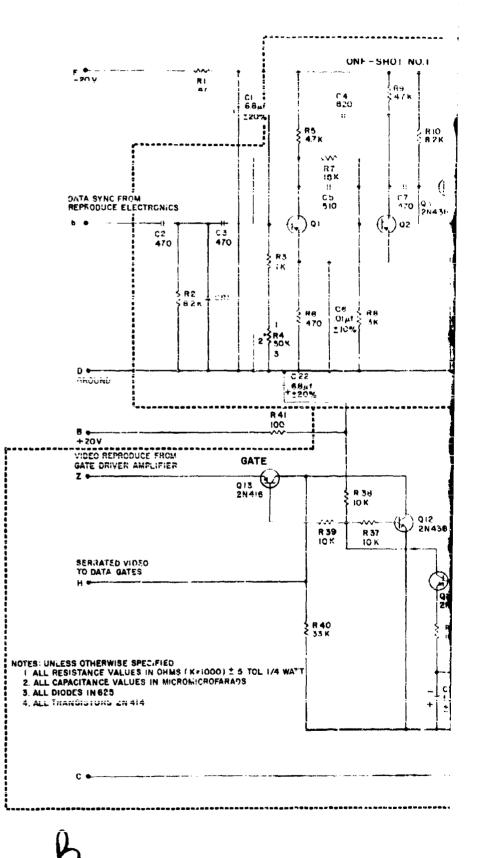

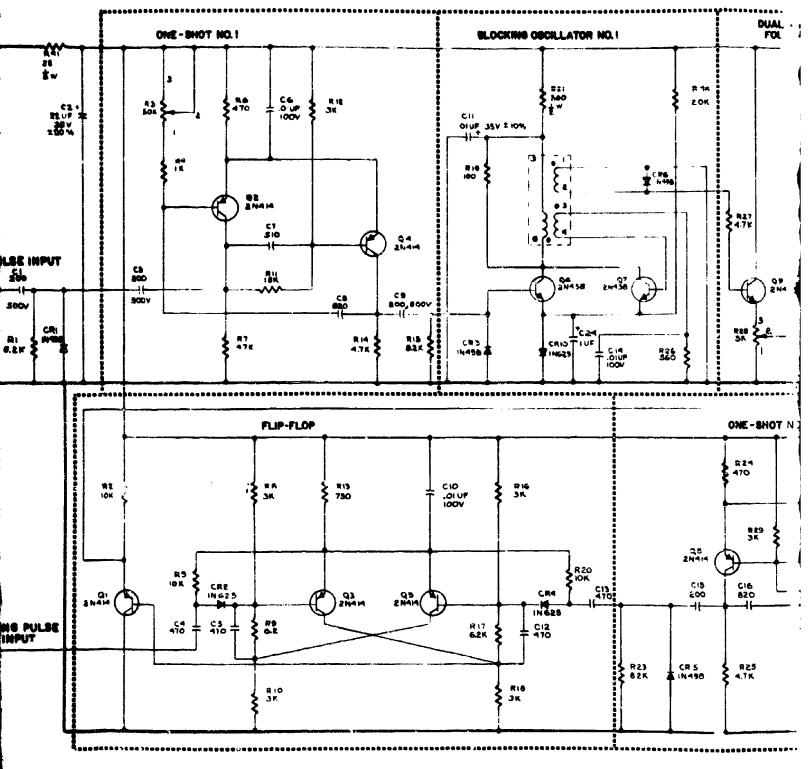

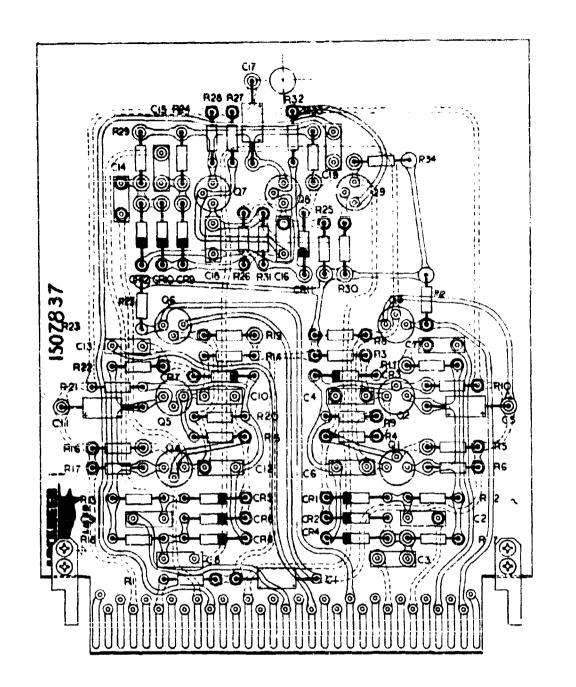

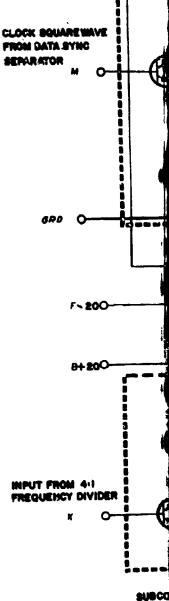

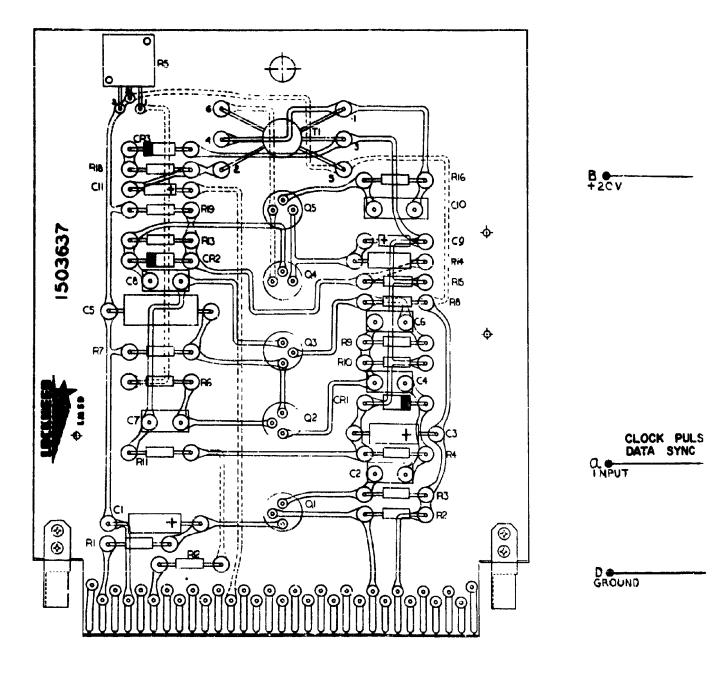

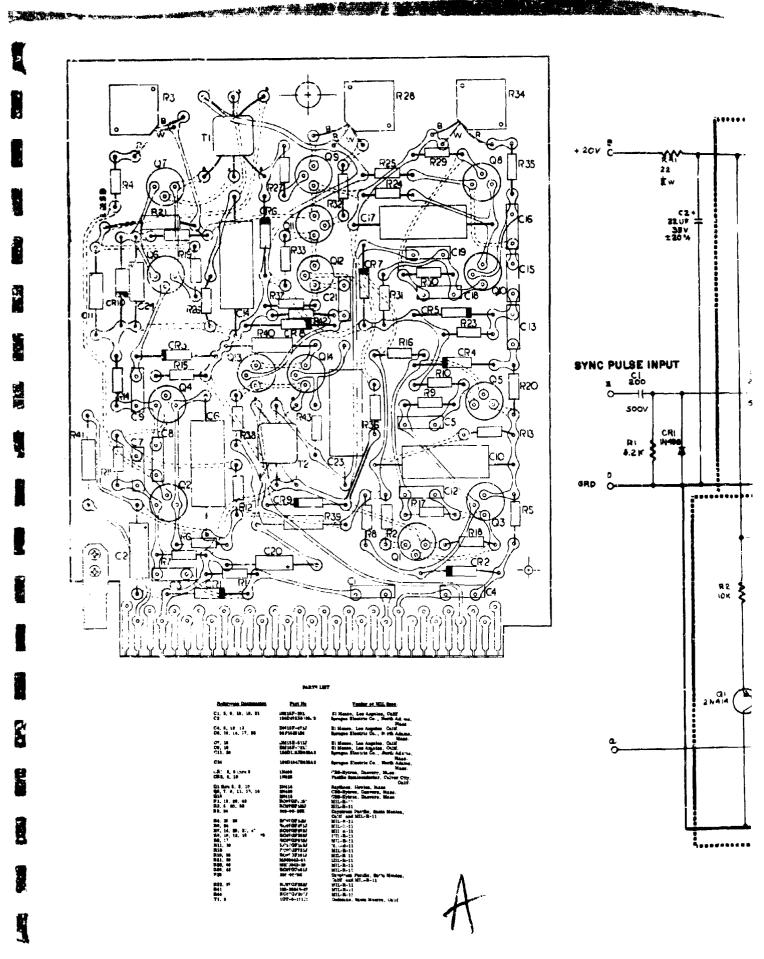

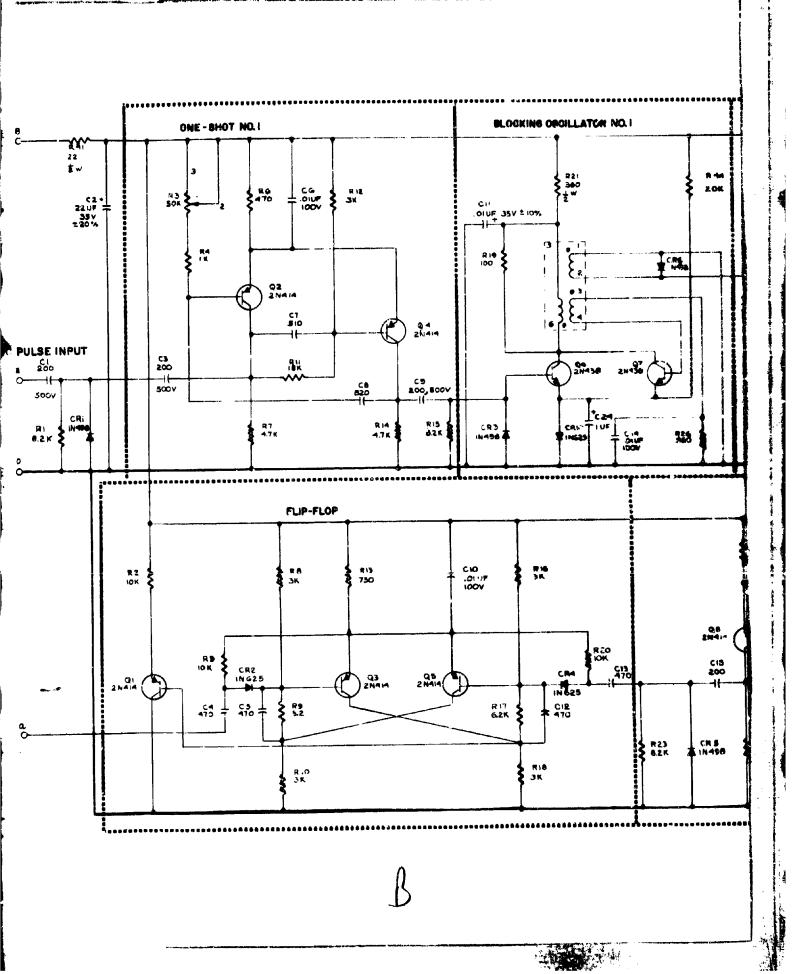

7.2.3.1 Data Sync Separator

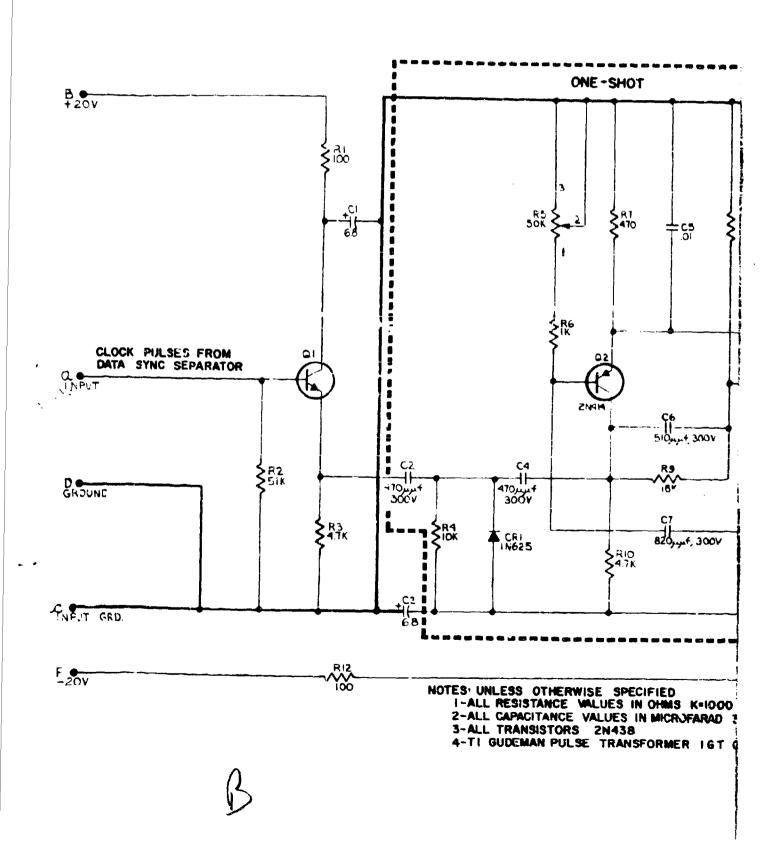

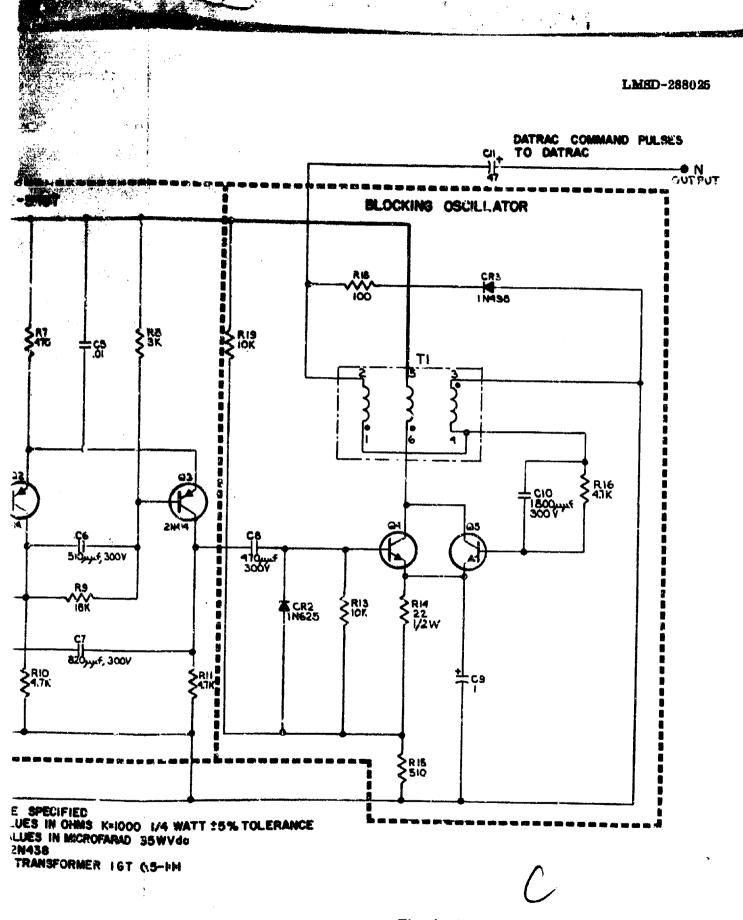

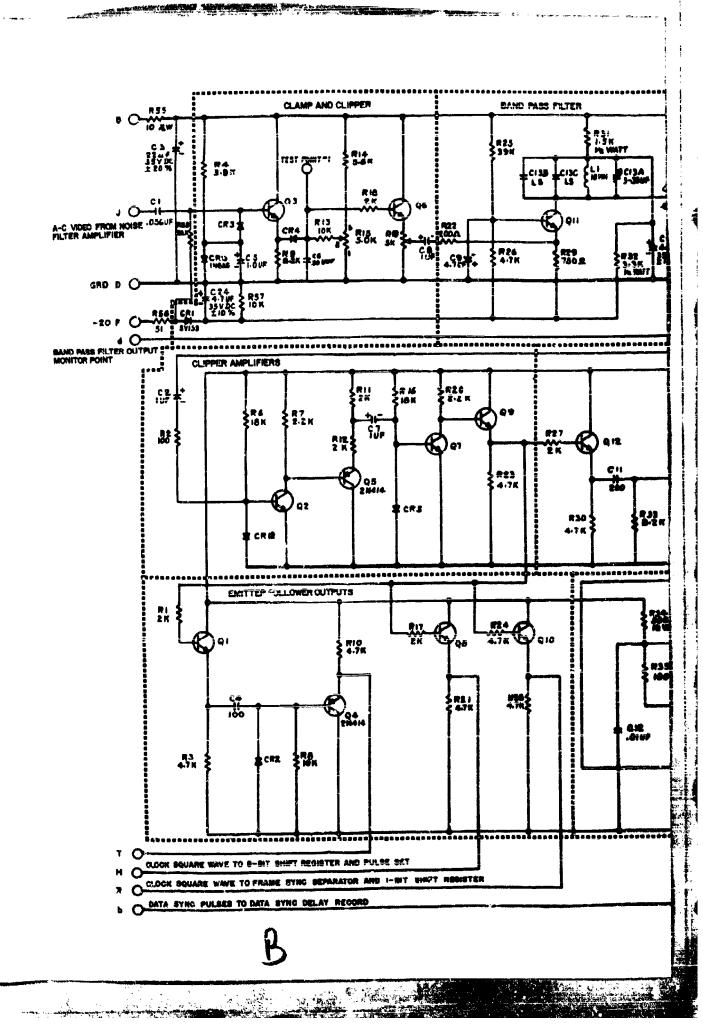

The purpose of the Data Sync Separator is to extract the data sync or clock information from the composite pulse train (a-c video). The Data Sync Separator is composed of the following circuits: clamp and clipper, band-pass filter, pulse shaper, clipper amplifiers, one-shot, emitter follower, and blocking oscillator. A schematic diagram of the Data Sync Separator is shown in Fig. A-8.

Clock output occurs in the form of a square wave or pulse; data sync is in the form of a pulse only. Clock information is in time phase with data sync information. Data sync output is actually clock information which has been delayed so that keying pulses for the data gates occur at a time when interchannel crosstalk is at a minimum. The Q of the band-pass filter is such that clock and data sync outputs are present when as many as approximately 30 consecutive data pulses are missing. Operation of the Data Sync Separator ceases whenever more than approximately 30 consecutive data pulses are missing.

The composite pulse train input (a-c video) from the Noise Filter Amplifier appears at pin J. It then enters the clamp and clipper circuit, which is composed of diodes CR3 and CR4, transistors Q3 and Q6, and associated components. This circuit restores the d-c level to the a-c video and clips below minimum data level. Resistor R13 is adjusted so that positive peak clipping occurs at 1.5 ( $\pm 0.2$ ) volts. Test point TP1 - the junction of diode CR4 and resistor R13 - should be observed when this adjustment is being made.

The output from the clamp and clipper circuit passes through the emitter follower, composed of transistor Q6 and resistor R19, into the band-pass filter. This bandpass filter is a ringing, oscillator-type circuit in which the resonant frequency is that of the sampling rate of the composite pulse train. The output level control of the clampand-clipper circuit, resistor R19, is adjusted so that the peak-to-peak amplitude of the output sine wave at the junction of capacitor C14 and diode CR7 is 15 ( $\pm 1$ ) volts. Fine tuning of the tank circuit is made by adjusting capacitor C13A,

The signal is coupled into the pulse shaping network through capacitor C14. Transistors Q14 and Q17, diode CR7, and associated components act as a dual emitter follower and clamp circuit. Its output is fed into the clipper circuit composed of dicdes CR9 and CR10, transistor Q19, and associated components. Silicon diodes CR9 and CR10 change the sine wave from the dual emitter follower into an approximately square wave.

This square wave is coupled into the clipper amplifiers through the emitter follower composed of transistor Q19 and resistor R52. There are two saturating-type amplifier stages and two emitter follower stages in the clipper amplifier circuitry. The two amplifiers are transistors Q2 and Q7 with their associated components; the two emitter follower stages are transistors Q5 and Q9 with their associated components. The signal is amplified but not inverted, and the output is fed into four succeeding emitter followers in parallel. Output of the clipper amplifiers, which is now a square wave, passes through the emitter follower composed of transistor Q8 and associated components to pin M and through the emitter follower transistor composed of transistor Q10 and associated

Revised 25 May 1960

Ľ

R

U

R

I

Π

Π

H

E

П

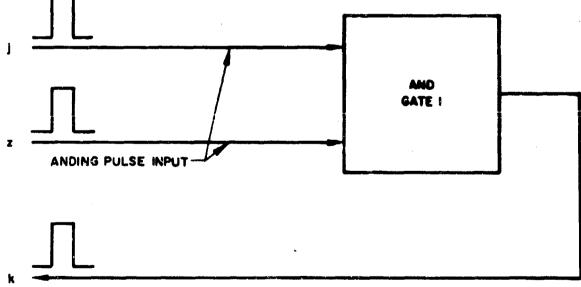

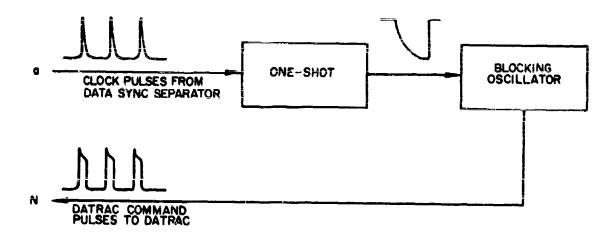

ponents to pin R. These two olipper amplifier outputs are then delivered as clock summer waves to the Sight-Bit Shift Register at pin M and to the Frame Sync Separator if pin R. Output of the clipper amplifiers is also fed to the one-shot through the emitter follower composed of transistor Q12 and associated components. Positivegoing portions of the square wave trigger the one-shot, which is composed of transistors Q15 and Q18 and their associated components. The variable delay of 4 to 25 microseconds is adjusted by resistor R39 in such a manner that the data gates are keyed when minimum interchannel crosstalk occurs. The one-shot output (monitored at the junction of capacitor C21 and resistor R51) is a series of positive pulses. These pulses fire a blocking oscillator composed of transistors Q13 and Q16, transformer T1, and associated components. The output of the blocking oscillator consists of data sync pulses which are fed to the Pulse Sequencer and Frequency Divider at pin b. Finally, the output from the clipper amplifiers passes through an emitter follower composed of transistor Q1 and its associated components; a differentiating circuit composed of capacitor C4, diode CR2, and resistor R8; and an emitter follower composed of transistor Q4 and associated components to pin T for delivery as a series of positive clock pulses to the Data Sync Delay Record.

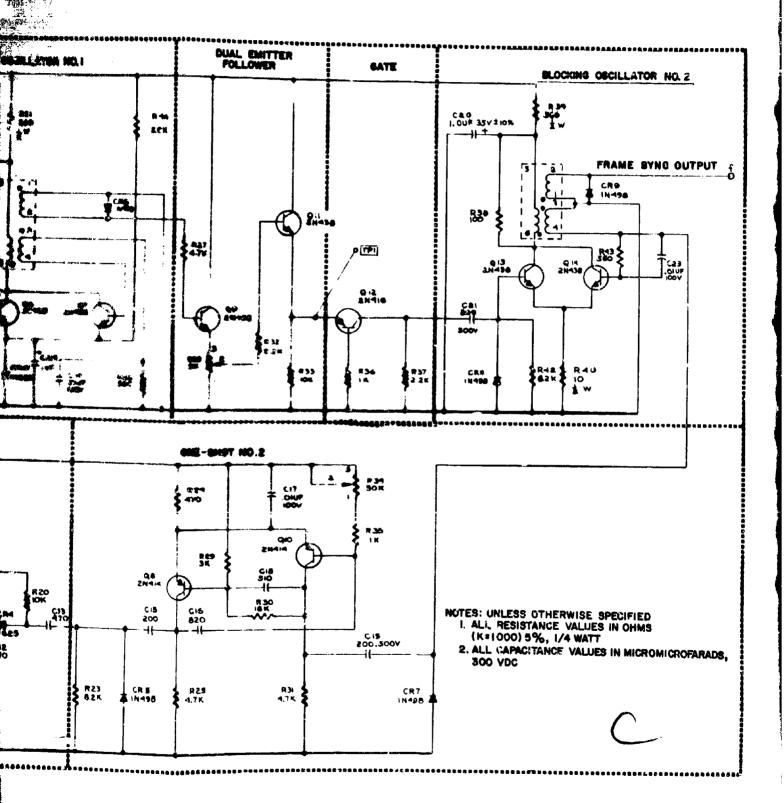

7. 2. 3. 2 Frame Sync Separator

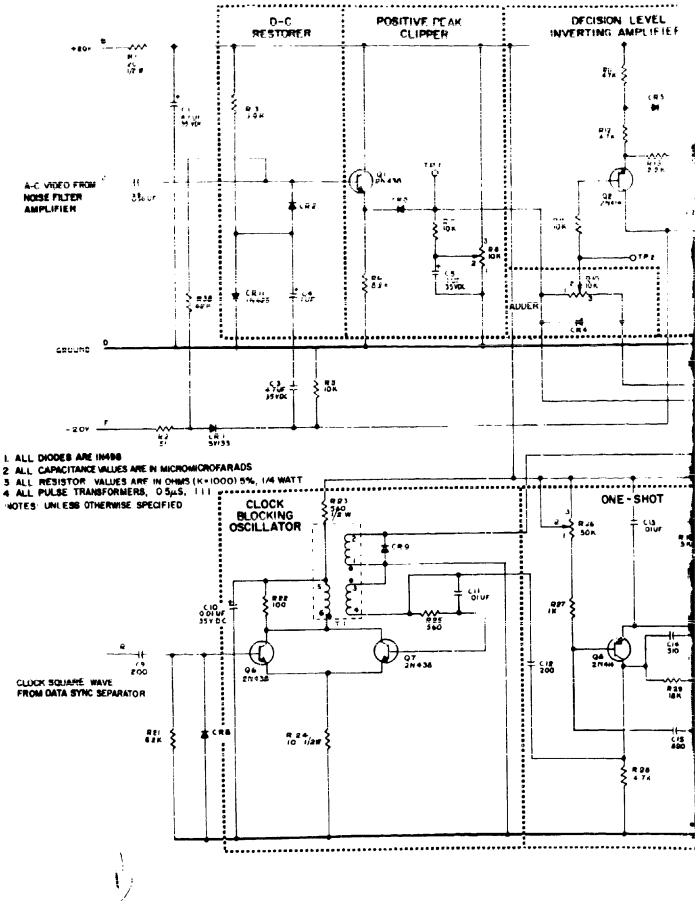

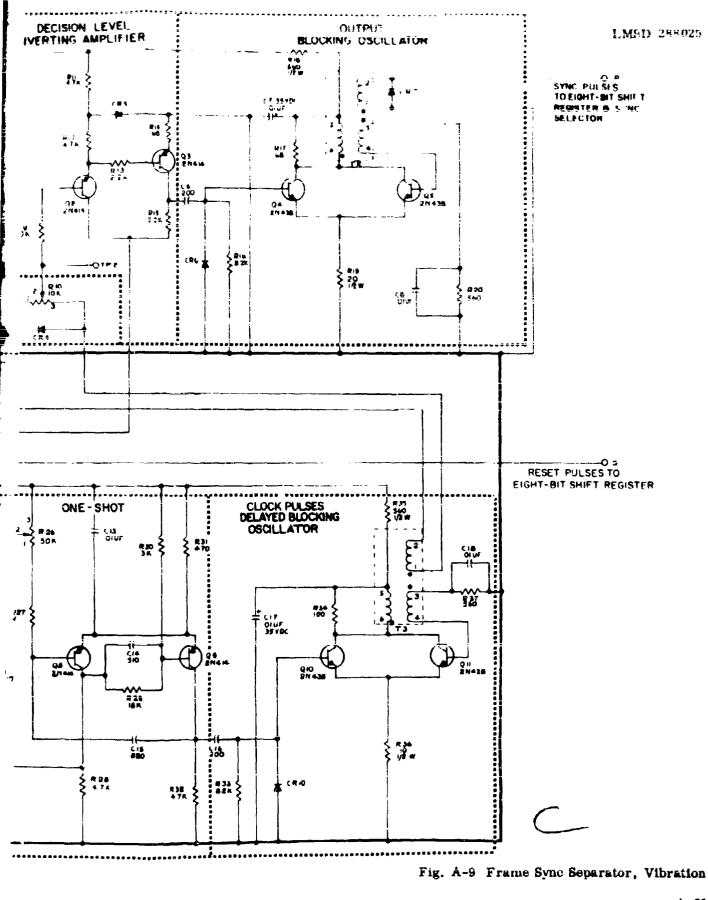

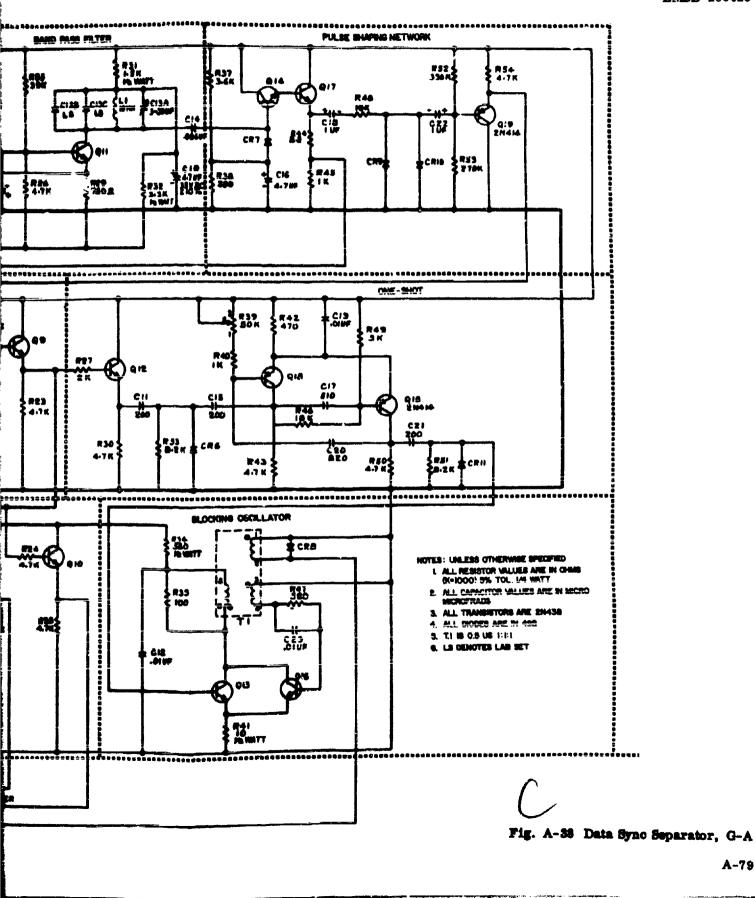

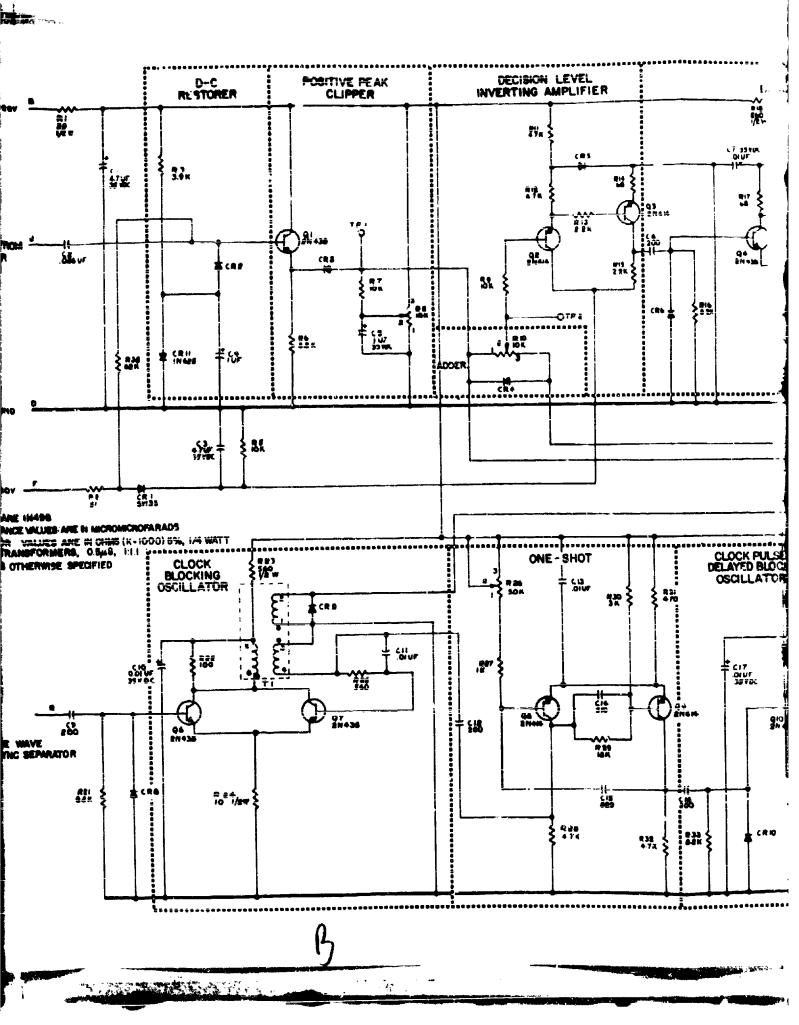

The Frame Sync Separator produces a pulse whenever a data pulse is absent in the composite pulse train. This unit is adjusted so that whenever the level of a data pulse falls below a 0.5-volt level with reference to the base line, a pulse is produced. The unit is made up of the following functioning circuits: d-c restorer, positive peak clipper, adder, decision level inverting amplifier, one-shot, and three blocking oscillators. A schematic diagram appears in Fig. A-9.

The composite pulse train (a-c video) input is delivered to pin J. It is then clamped to a few tenths of a volt, positive d-c, by means of the d-c restorer composed of capacitors C2 and C4, diode CR2, diode CR11, and resistor R3.

7-28

#### LOCKHEED AIRCRAFT CORPORATION

The signal is then delivered to the positive peak clipper set to clip below minimum its level, which is approximately +2 volts as monitored at test point TP1. This clipper is composed of transistor Q1, diode CR3, and associated components. The clipping level is adjusted by varying resistor R8.

The clock square wave from the Data Sync Separator appears at pin R. It is delivered to the clock blocking oscillator composed of transistors Q6 and Q7, transformer T1, and associated components. The output of this blocking oscillator is delivered to pin S as reset pulses to the Eight-Bit Shift Register. It also is delivered to the onesl ot composed of transistors Q8 and Q9 and associated components. This multivibrator introduces a variable time delay from 4 to 25 microseconds. The time delay is set by adjusting resistor R26. The output is delivered as clock pulses to a delayed blocking oscillator composed of transistors Q10 and Q11, transformer T3, and associated components.

The output of this blocking oscillator is delivered to the adder composed of resistor R10. This adder combines the clipped composite pulse train and delayed data sync. Resistor R26 in the one-shot circuit is adjusted so that the negative-going blocking oscillator pulses are centered on the data pulses as they are monitored at test point TP2.

The output of the adder is delivered to the decision level inverting amplifier composed of transistors Q2 and Q3, diode CR5, and associated components. This amplifier selects the blocking oscillator pulses which coincide with the absence of data pulses and provides a positive-going pulse to fire the output blocking oscillator composed of transistors Q4 and Q5, transformer T2, and associated components.

The output blocking oscillator provides sync pulses which are delivered to the Eight-Bit Shift Register and the Sync Selector at pin P. Resistor R10 is adjuste so that the blocking oscillator fires reliably whenever a data pulse is absent but will not fire under any other conditions. A good setting of R10 would be halfway between (1) the

7-29

I

I

Π

I

ſ

E

- Pri Jacob

Ī

L

I

setting that just <u>begins</u> to fire the output blocking oscillator at clock rate, and (2) the setting that just gtops firing the output blocking oscillator at data pulse absence rate. This setting can be monitored at pins J and P.

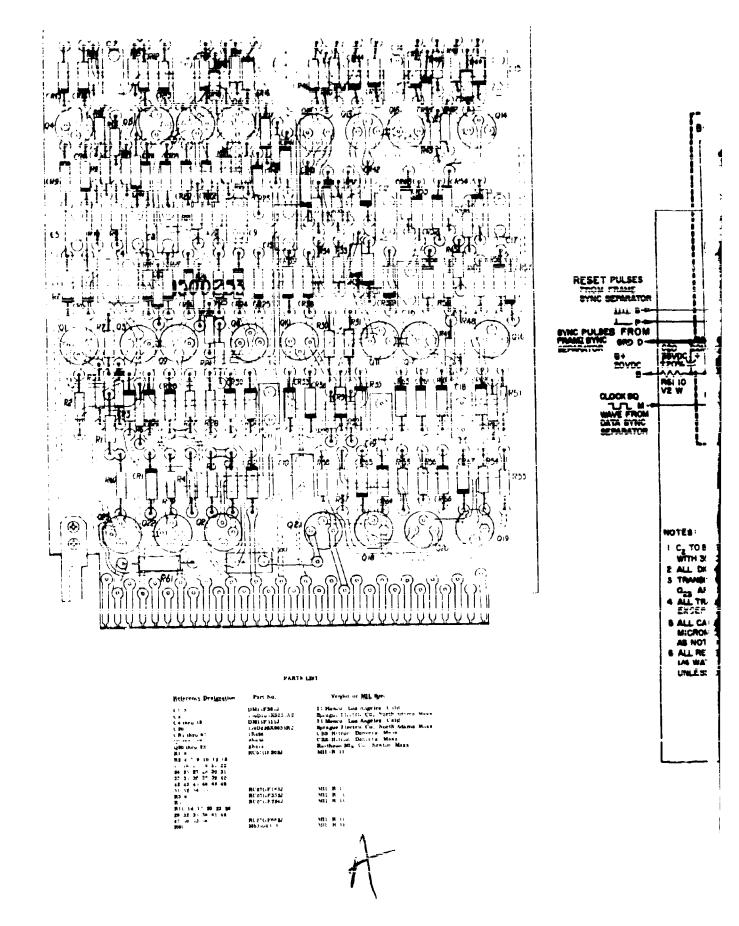

7, 2. 5. 3 Kight-Bit Shift Begister

The purpose of the Eight-Bit Shift Register is to store data pulse absence or sync pulse information for eight clock periods (of time) and present to a succeeding AND gate direct sync pulse outputs and stored sync pulse outputs.

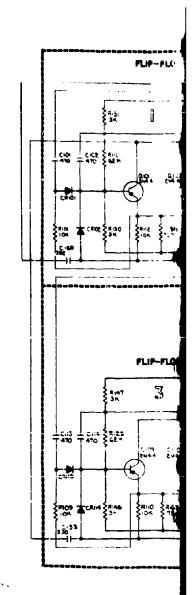

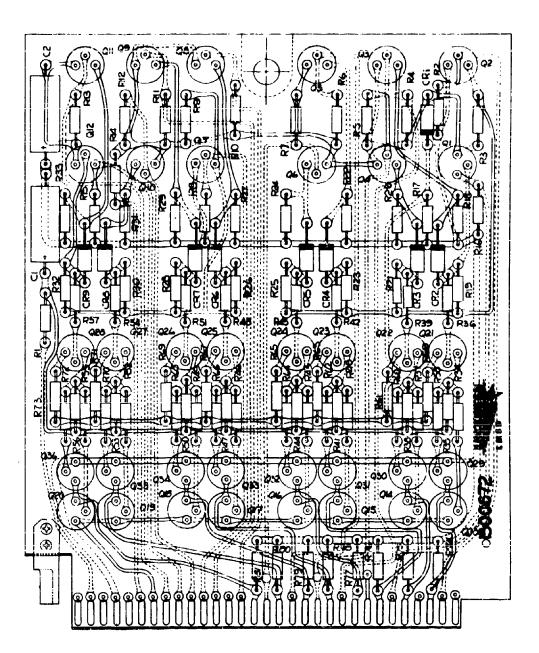

This unit is composed of a series string of nine delay-coupled flip-flops, four output emitter followers, and a clock driver. The schematic diagram is shown in Fig. A-10.

The first flip-flop acts as a buffer stage for the succeeding eight units in the shift register. It stores the sync pulses until the clock shifts this information into the first storage flip-flop.

Three inputs are provided: Reset (clock) pulses from the Frame Sync Separator appear at pin S; sync pulses from the Frame Sync Separator appear at pin P; and the clock square wave from the Data Sync Separator appears at pin M.

The reset pulse on pin S passes through diode CR1 and saturates transistor Q1. when a sync pulse is present at pin P, current passes through diode CR2 causing transis.or Q3 to saturate and the collector of transistor Q1 to go to high potential. This allow: capacitor C5 to charge through R10 because diode CR7 is back-biased when transistor Q2 of the clock driver is cut off with a negative clock pulse. When transistor Q2 is saturated with a positive clock pulse, diodes CR7 and CR2 conduct because of the previews charge on capacitor C5. This current flowing through diode CR8 cuts off transistor Q4 and saturates transistor Q5, thus setting up the first storage flip-flop.

In a like manner, the absence of a syne pulse will cause the first storage stage to be set up in the opposite way with transistor Q5 cut off and transistor Q4 saturated. This process continues through succeeding stages until the last stage is reached.

Two outputs are provided by the output emitter followers. The stored sync pulses are delivered to pin U for transfer to the Programmer, while the direct sync pulses are delivered to pin K for transfer to the Programmer.

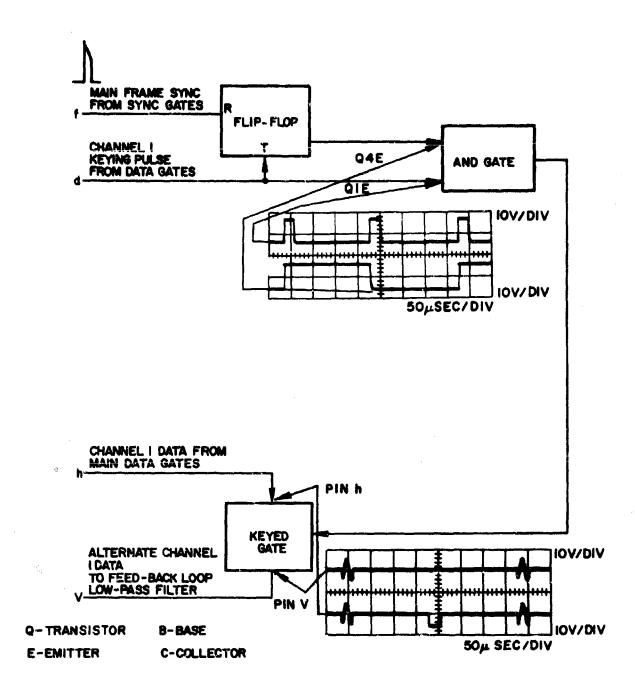

7.2.3.4 Programmer

I

1:

F

Ľ

The purpose of the Programmer is to (1) provide a keying pulse to the sync gate every other frame at the Channel 1 position and (2) provide the AND ing logic associated with the Eight-Bit Shift Register. The Programmer is composed of an AND gate and a flip-flop. A schematic diagram is shown in Fig. A-11.

Inputs to the AND gate (pins K and U) are provided by the Eight-Bit Shift Register. Input at pin K corresponds to the absence of a data pulse, and input at pin U corresponds to the presence of a data pulse delayed for eight bits of time. Diodes CR1 and CR2 and the emitter follower composed of transistor Q1 and resistor R1 provide a pulse upon the time-coincidence of input 3 at K and U.

The flip-flop, which is composed of transistors Q2 and Q3 and associated components, is triggered by the Channel 1 keying pulse from the data gate. This pulse appears at pin d. The flip-flop output, which is coupled through the emitter follower composed of transistor Q4 and resistor R12, constitutes a keying pulse to the sync gate and is delivered to pin a.

7.2.3.5 Sync Selector

The purpose of the Sync Selector is to combine sync pulses for recording purposes in such a manner that only sync gate and keyed gate circuitry need be used to produce

Revised 25 May 1960

7-31

LMBD-288025

**I**

e a la calendaria de la c execularia de la calendaria de

E

both main and subcommutated frame sync while in the reproduce mode. A schematic diagram of the Sync Selector is shown in Fig. A-12.

There are two inputs to the Sync Selector. Sync pulses from the Eight-Bit Shift Register AND gate appear on pin Z. Sync pulses from the Frame Sync Separator appear on pin P.

Some pulses entering at pin P pass through an emitter follower composed of transistor Q1 and resistors R2 and R4. These pulses then enter the gate circuit, composed of transistors Q3, Q4, and Q5 and associated components, at the emitter of transistor Q4. Series switch Q4 and shunt switch Q5 are keyed by a pulse amplifier composed of transistor Q3 and recistors R3 and R7. This pulse amplifier is operated by subcommutated keying pulses, which appear on pin K in such a manner that the presence of a keying pulse opens the gate and the absence of a keying pulse closes the gate. Output pulses from the gate are passed through the emitter follower composed of transistor Q7 and resistor R12 for delivery to gin d as the subcommutated sync pulse to the sync gate. Output pulses from the gate are also passed through the emitter follower composed of transistor Q6 and resistor R11 and are coupled through capacitor C4 for delivery to the blocking oscillator that is composed of transistors Q8 and Q9, transformer T1, and associated components.

Sync pulses also enter at pin Z and pass through an omitter follower composed of transistor Q2 and resistor R6 and are then coupled through capacitor C3 for delivery to the blocking oscillator.

The blocking oscillator is fired by current pulses from either capacitor C3 or capacitor C4. The positive output pulses of the blocking oscillator are delivered to pin f as composite frame sync for the Digital Record Electronics.

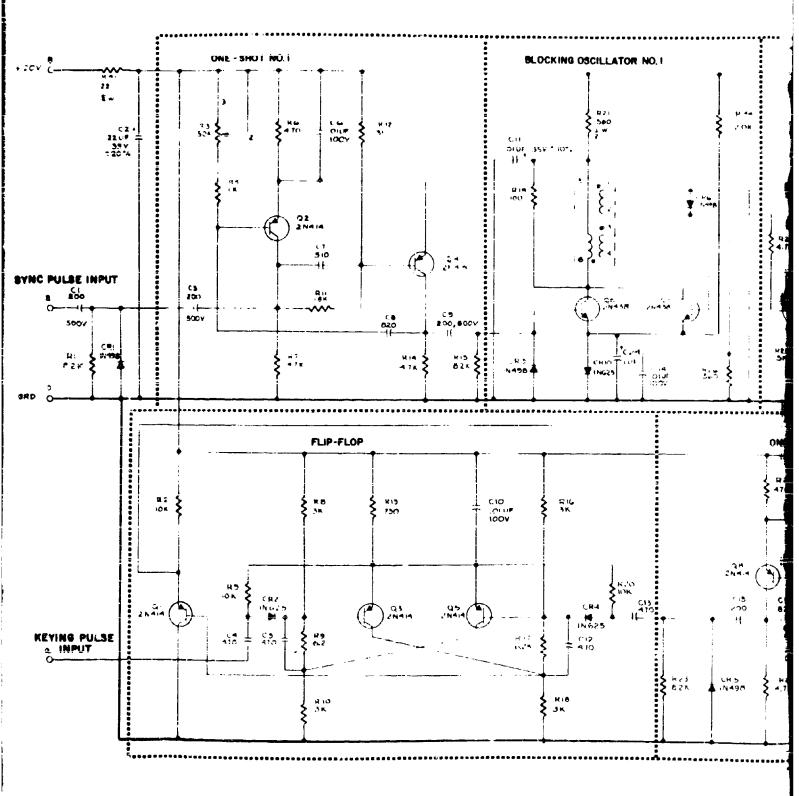

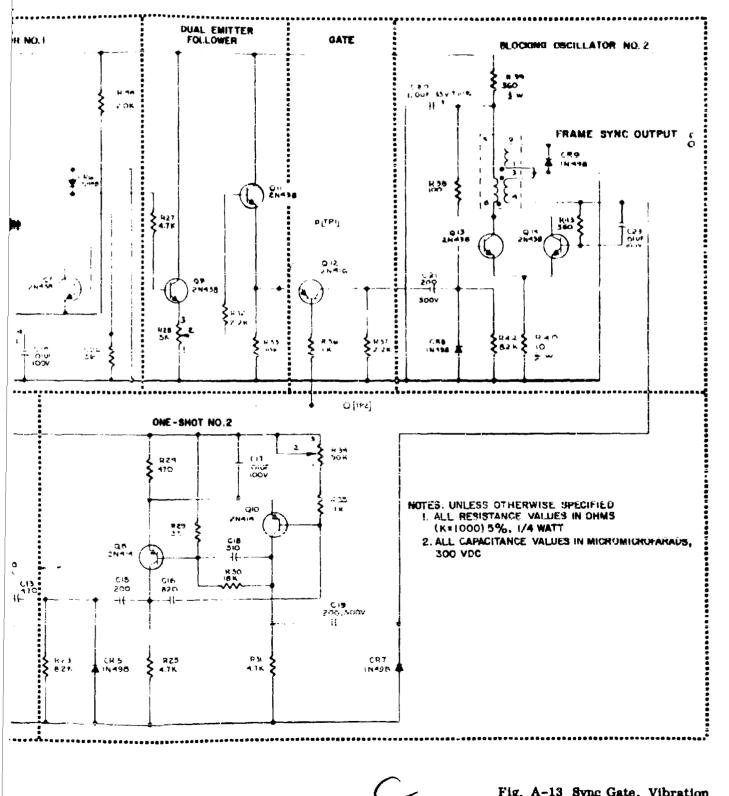

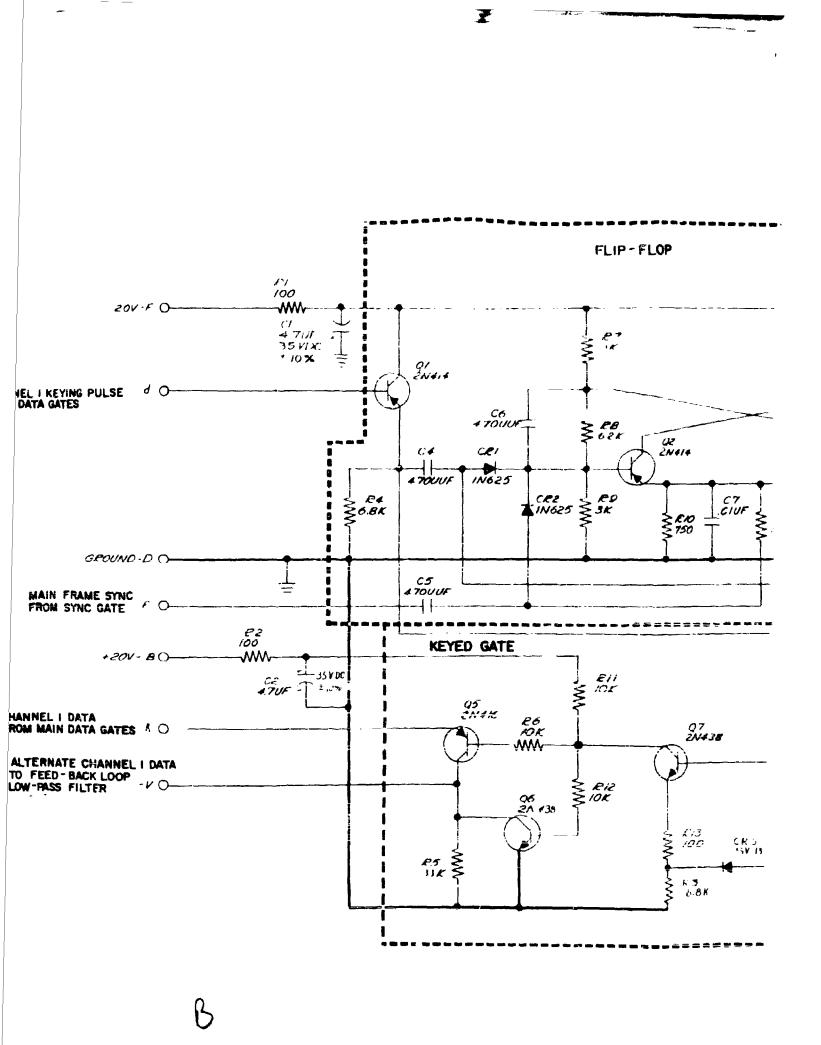

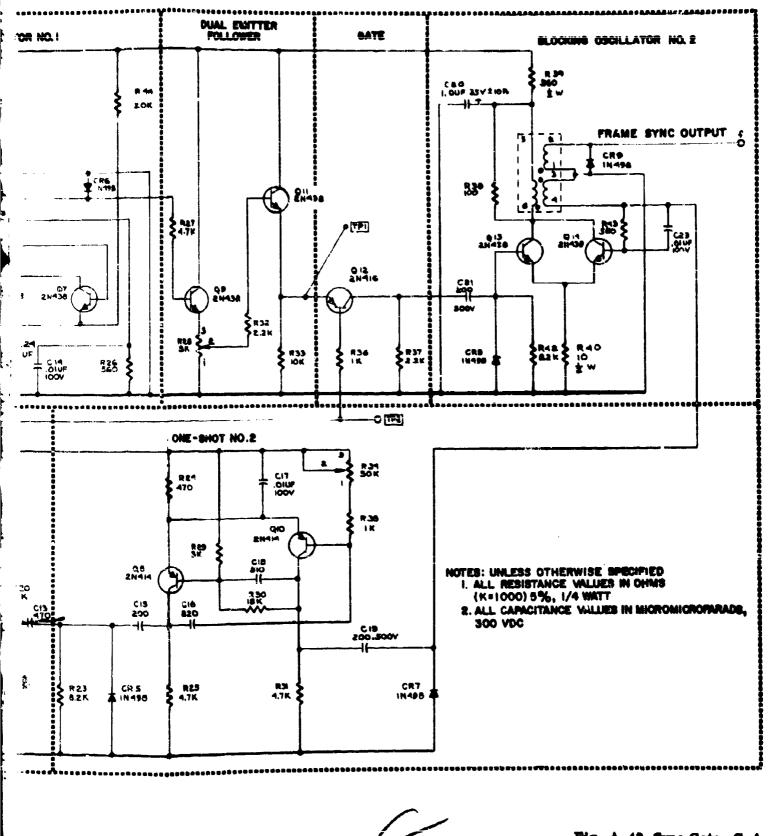

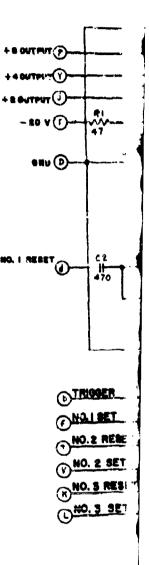

# 7. 2. 3. 6 Sync Gate

The purpose of the Sync Gate is to permit frame sync pulses to be generated only when such pulses are anticipated. Sync pulses which are not true sync pulses are scantines produced by preceding sync separation circuits because of r-f interference. Therefore, if a pulse can be supplied to arrive at a time when frame sync is expected and this pulse keys a gate that follows the frame sync logic circuitry, the chanse of prefacing false frame sync is greatly reduced. The Sync Gate is made up of two cae-shate, two blocking oscillators, a flip-flop, a dual emitter follower, and a gate. The schemetic diagram for the Sync Gate is shown in Fig. A-13.