|  |  | This document has been approved for public release and sale. |  |

|--|--|--------------------------------------------------------------|--|

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

|  |  |                                                              |  |

15 18 72-185 15 Fechnical ( port 15 - 1972

### SHORT PULSE EFFECTS IN SEMICONDUCTOR DIODES

IKOR Incorporated

### Approved for public release; distribution unlimited.

Reproduced by NATIONAL TECHNICAL INFORMATION SERVICE US Department of Conduct Co Againstand Co 2015

Rome Air Development Center Air Force Systems Command Griffiss Air Force Base, New York

| Security Classification                                                                                                                                                                                                                                                                                                                                                           | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| يجديها الأجريبي الالعاكات فلاقت النبوجي بيانا الألف المتحديني والمتحد                                                                                                                                                                                                                                                                                                             | ENT CONTROL DATA - R & D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                   | and indexing annotation must be entered when the overall report is classified)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| ORIGINATING ACTIVITY (C) porate author)                                                                                                                                                                                                                                                                                                                                           | 20. REPORT SECURITY CLASSIFICATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| IKOR Incorporated                                                                                                                                                                                                                                                                                                                                                                 | UNCLASSIFIED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| N.W. Industrial Park                                                                                                                                                                                                                                                                                                                                                              | 25. GROUP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| Burlington, MA 01803                                                                                                                                                                                                                                                                                                                                                              | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| REPORT TITLE                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| SHORT PULSE EFFECTS IN SEMICONDUCT                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 4 DESCRIPTIVE NOTES (Type of report and inclusive dat<br>Final Report 13 Sep 71 - 13 May 72<br>5 AUTHOR(S) (First name, middle initial, last name)                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| Derek J. Fitzgerald<br>James J. Stekert                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| REPORT DATE                                                                                                                                                                                                                                                                                                                                                                       | 78. TOTAL NO OF PAGES 75, NO OF REFS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| August 1972                                                                                                                                                                                                                                                                                                                                                                       | 48 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| B. CONTRACT OR GRANT NO.                                                                                                                                                                                                                                                                                                                                                          | 90. ORIGINATOR'S REPORT NUMBER(S)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| F30602-72-C-0046                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| Tab Orden No. 150(0053                                                                                                                                                                                                                                                                                                                                                            | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| Job Order No. 45060251                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                   | 9b. OTMER REPORT NO(3) (Any other numbers that may be assigned<br>this report)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 0 DISTRIBUTION STATEMENT                                                                                                                                                                                                                                                                                                                                                          | RADC-TR-72-185                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| RADC Project Engineer<br>Leon L. Stevens (OCTE)                                                                                                                                                                                                                                                                                                                                   | Rome Air Development Center (OCTE)<br>Griffiss Air Force Base, New York 1344                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| AC 315-330-4251                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 3 ABSTRACT                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| and in series with a 50-ohm stripl<br>8 diodes. It is found in the seri<br>in forward bias at all signal volt<br>region thickness. At higher signa<br>signal since diode conductance sig<br>stress. A new reverse bias equiva<br>shown. Forward to reverse bias st<br>parallel bias address. No irrever<br>within the signal limits. Some ir<br>noted. A non-optimized SPDT swite | determine the feasibility of using PIN diodes as<br>ps, 8 MW impulse signals. Single diodes in shunt<br>line were studied, as were series stacks of up to<br>ies configurations that good signal fidelity obtain<br>tages, with insertion loss being a function of I<br>al voltages it is an even stronger function of the<br>mificantly increases with internal voltage<br>thent circuit for high voltage transient signals is<br>tack switching occurs in less than 500 ns with<br>resible signal or switching effects are observed<br>reversible increase in reverse bias current is<br>the was constructed and studied. Results show<br>oftage, short pulse PIN diode duplexer. |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

.

### UNCLASSIFIED

÷

Security Classification

| KEY WORDS          | LINKA |     | LINKB  |        | LINKC |       |

|--------------------|-------|-----|--------|--------|-------|-------|

|                    | ROLE  | WT. | ROLE   | W T    | ROLE  | W     |

|                    |       |     |        |        |       |       |

| PIN Diodes         |       |     |        |        |       |       |

| Switches           |       |     |        |        |       |       |

| Short Pulse        |       |     |        |        |       |       |

| Microwaves         |       |     |        |        |       |       |

| High Voltage       |       |     |        |        |       |       |

| Transient Response |       |     |        |        |       |       |

| -                  |       |     |        |        |       |       |

|                    |       |     |        |        |       |       |

|                    |       |     | Į.     |        |       |       |

|                    |       | }   |        |        |       |       |

|                    |       |     | 1      |        |       |       |

|                    |       |     | 1      |        | l     |       |

|                    |       | l   | [      |        | 1     |       |

|                    |       | 1   | ļ      |        |       | )<br> |

|                    |       |     |        |        | 1     | l     |

|                    |       |     |        |        | ł     | ł     |

|                    |       |     | l      |        | 1     | 1     |

|                    |       | ł   |        |        |       |       |

|                    |       |     |        |        |       |       |

|                    | l     | 1   |        |        | 1     |       |

|                    |       | 1   | 1      |        |       |       |

|                    |       |     | [      |        |       |       |

|                    |       | -   | 1      |        |       | 1     |

|                    |       |     | Ì      |        |       |       |

|                    |       |     |        | 1      | 1     | l     |

|                    |       |     |        |        | 1     |       |

|                    |       |     |        |        |       |       |

|                    |       |     |        |        | 1     |       |

|                    |       |     |        |        |       |       |

|                    |       |     |        |        |       |       |

|                    |       |     | 1      |        | [     |       |

|                    |       |     |        |        |       |       |

|                    |       |     |        |        |       |       |

|                    |       | ļ   | ł      |        |       |       |

|                    |       |     |        |        |       |       |

|                    |       |     |        |        |       |       |

|                    |       |     |        |        |       |       |

|                    |       |     |        |        |       |       |

|                    |       |     | 1      |        | İ     |       |

|                    |       | ł   |        |        |       |       |

|                    |       | ļ   |        |        |       |       |

|                    |       | 1   |        |        |       |       |

|                    |       |     | ļ      |        |       |       |

|                    |       | İ   |        |        |       |       |

|                    |       |     |        |        |       |       |

|                    |       | l   |        |        |       |       |

|                    |       | 1   |        |        |       |       |

|                    |       |     |        |        | Ì     |       |

|                    | 1     |     | ļ      |        |       |       |

|                    |       |     |        |        |       |       |

|                    |       | 1   |        |        |       |       |

|                    |       |     |        |        |       |       |

|                    | i     | 1   |        |        | 1     |       |

|                    |       |     |        |        |       |       |

| ACGriffiss AFB NY  |       | l   |        |        |       |       |

| GACGriffiss AFB NY |       | 1   | UNCLAS | SIFIED |       |       |

### SHORT PULSE EFFECTS IN SEMICONDUCTOR DIODES

Derek J. Fitzgerald James J. Stekert

**IKOR** Incorporated

Approved for public release; distribution unlimited.

### FOREWORD

This Final Report, "Short Pulse Effects in Semiconductor Diodes," covering the period 13 September 1971 to 13 May 1972, was prepared by IKOR Incorporated, N.W. Industrial Park, Burlington, Massachusetts, under contract F30602-72-C-0046, Job Order Number 45060251.

This program was administered by Rome Air Development Center, Griffiss Air Force Base, New York. Mr. Leon L. Stevens (OCTE) was the Froject Engineer for the Center.

This report has been reviewed by the Information Office (OI) and is releasable to the National Technical Information Service (NTIS).

This technical report has been reviewed and is approved.

Lem L Stevene

Approved:

LEON L. STEVENS Project Engineer Electron Devices Section

Approved:

JAMES L. RYNNING Colonel, USAF Chief, Surveillance and Control Division

FOR THE COMMANDER:

tud fil

FRED I. DIAMOND Acting Chief, Plans Office

### ABSTRACT

An investigation has been made to determine the feasibility of using PIN diodes as switching elements to control 150 ps, 8 MW impulse signals. Single diodes in shunt and in series with a 50 ohm stripline were studied, as were series stacks of up to 8 diodes. It is found in the series configurations that good signal fidelity obtains in forward bias at all signal voltages, with insertion loss being a function of I region thickness. Reverse bias isolation also is a function of I region thickness. At higher signal voltages it is an even stronger function of the signal, since diode conductance significantly increases with internal voltage stress. A new reverse bias equivalent circuit for high voltage transient signals is shown. Forward to reverse bias stack switching occurs in less than 500 ns with parallel bias address. No irreversible signal or switching effects are observed within the signal limits. Some irreversible increase in reverse bias current is noted. A non-optimized SPDT switch was constructed and studied. Results show definite feasibility for a high voltage, short pulse PIN diode duplexer.

### TABLE OF CONTENTS

| SECTION | TITLE                             | PAGE |

|---------|-----------------------------------|------|

|         |                                   |      |

|         | ABSTRACT                          | vi   |

|         | LIST OF ILLUSTRATIONS             | vii  |

|         | LIST OF NOTATION                  |      |

| Ι.      | INTRODUCTION                      | 1    |

|         | 1. Background                     | 1    |

|         | 2. Purpose of Program             | 2    |

|         | 3. Work Performed                 | 2    |

| п.      | DIODE CHARACTERIZATION            | 4    |

|         | 1. PIN Diode Properties           | 4    |

|         | 2. Text Fixtures                  | 7    |

|         | 3. Experimental Apparatus         | 9    |

|         | 4. Series Diode Measurements      | 11   |

|         | 5. Shunt Diode Measurements       | 13   |

|         | 6. Diode Switching Time           | 16   |

|         | 7. Diode Conductance Relationship | 16   |

|         | 8. New Diode Equivalent Circuit   | 20   |

| III.    | DIODE STACKS                      | 24   |

| 1.1.4   | 1. Analytical Results             | 24   |

|         | 2. Experimental Results           | 26   |

| IV.     | THE SPDT SWITCH                   | 37   |

| 146     | 1. Switching Configurations       | 37   |

|         | 2. SPDT Measurements              | 40   |

| ••      | SUMMARY AND CONCLUSIONS           | 43   |

| v.      | 1. Diode Characterization         | 43   |

|         | 2. Diode Stacks                   | 43   |

|         | 3. SPDT Switch                    | 44   |

|         |                                   |      |

۷

Preceding page blank

| SECTION | TITLE           | PAGE |

|---------|-----------------|------|

| VI.     | RECOMMENDATIONS | 45   |

|         | REFERENCES      | 47   |

### LIST OF ILLUSTRATIONS

### Figure

.

Page

| 1.   | FIN Diode Structure                                       | 5  |

|------|-----------------------------------------------------------|----|

| 2.   | Diode Equivalent Circuits                                 | 6  |

| 3.   | Diode Test Fixture                                        | 8  |

| 4.   | Experimental Test Facility                                | 10 |

| 5.   | Series Mounted Diode Transmission and Reflection          | 12 |

| 6.   | Experimental Sectes Diode Transmission                    | 14 |

| 7.   | Typical Experimental Characteristics of a Shunt PIN Diode | 15 |

| 8.   | <b>Figue Switching Time Measurement Circuit</b>           | 17 |

| 9.   | Typica: Diode Characteristics                             | 18 |

| 10.  | Diode Co. auctance vs. Electrical Field                   | 19 |

| 11.  | Short Pulse Simplified Equivalent Circuit                 | 21 |

| 12.  | Incident Voltage vs. Diode Conductance                    | 22 |

| 13.  | Summary Incident Voltage vs. Conductance                  | 23 |

| 14.  | Stack Equivalent Circuit                                  | 25 |

| 15.  | Theoretical Stack Voltage Stress                          | 27 |

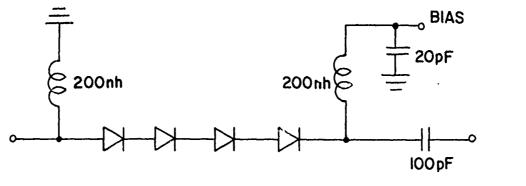

| 16.  | Diode Stack Circuit Diagram                               | 28 |

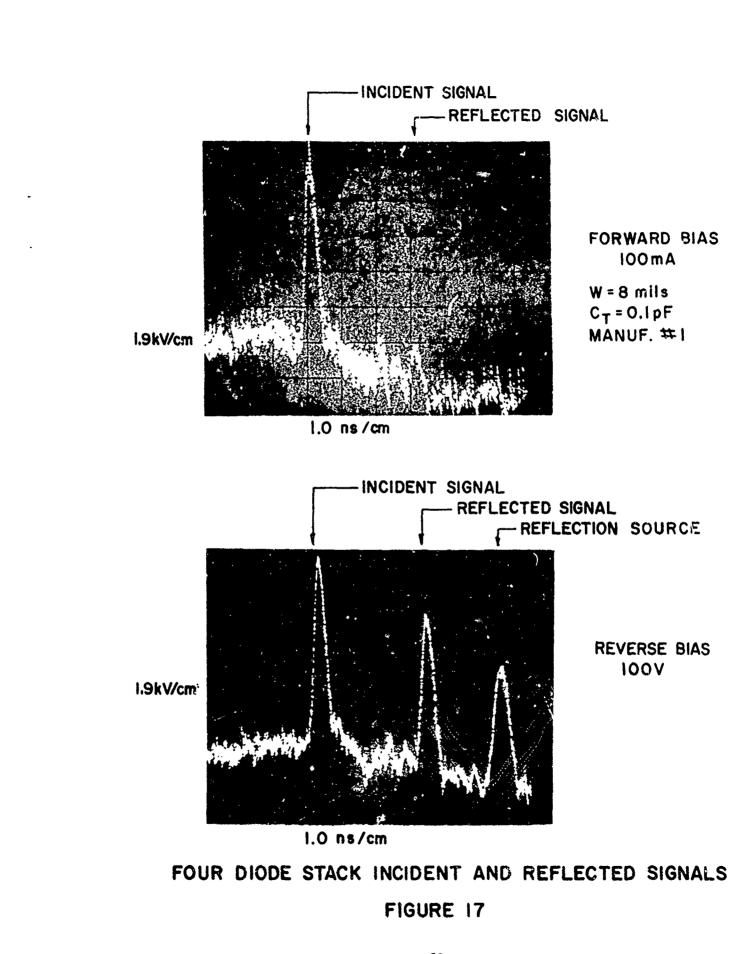

| 17.  | Four Diode Stack Incident and Reflected Signals           | 29 |

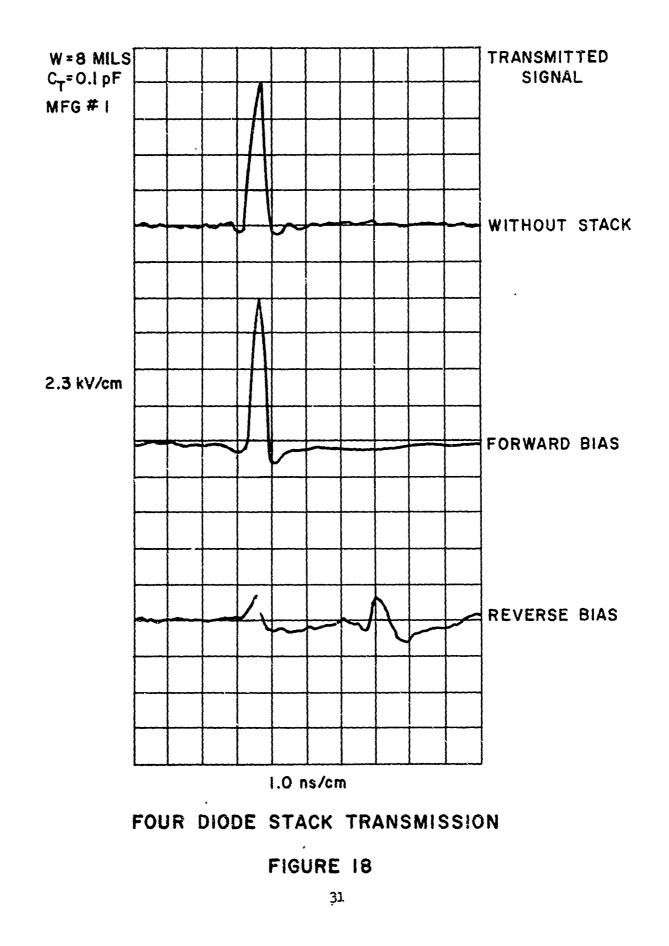

| 18.  | Four Diode Stack Transmission                             | 31 |

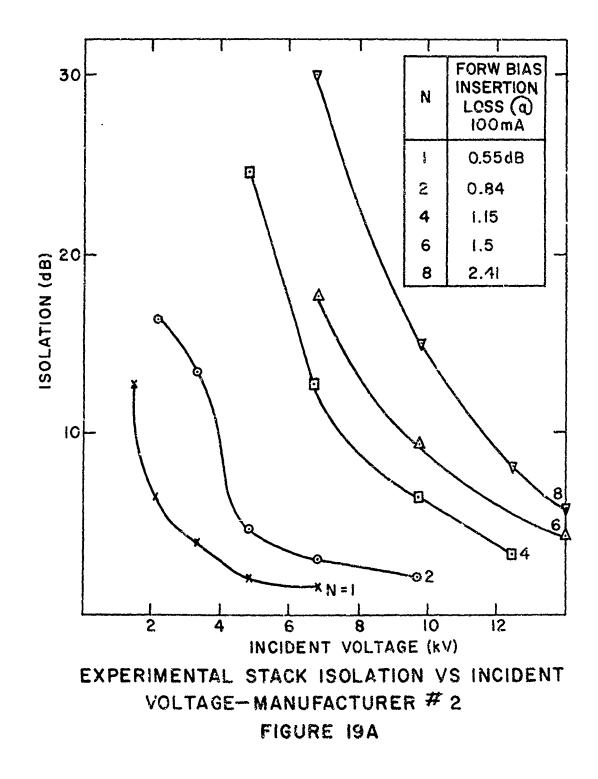

| 19A. | Experimental Stack Isolation vs. Incident Voltage -       |    |

|      | Manufacturer #2                                           | 32 |

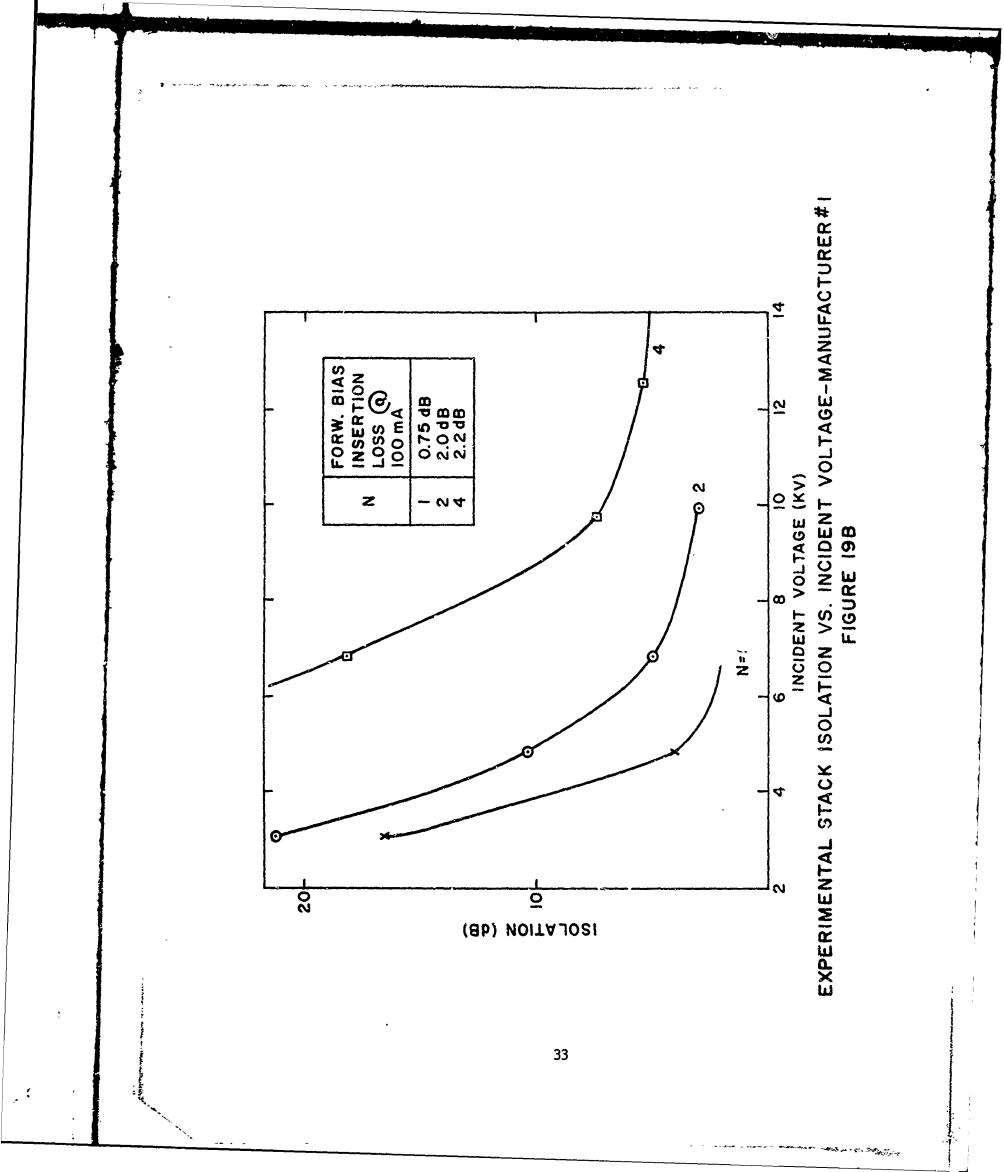

| 19B. | Experimental Stack Isolation vs. Incident Voltage -       |    |

|      | Manufacturer #1                                           | 33 |

| 20.  | Theo.etical Stack Isolation vs. Incident Voltage          | 34 |

| 21.  | Isolation vs. Incident Voltage for Various Diode Spacing  | 36 |

| 22.  | Basic Duplexer Function                                   | 38 |

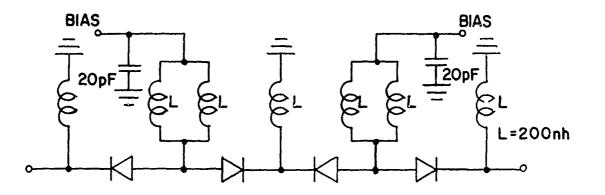

| 23.  | SPDT Switch Configurations                                | 39 |

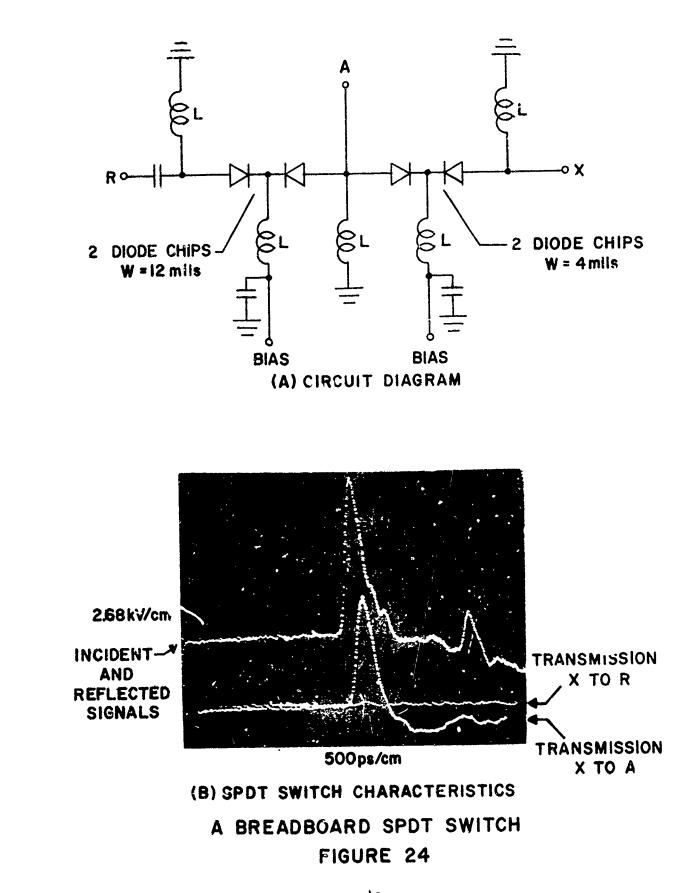

| 24.  | A Breadboard SPDT Switch                                  | 41 |

### LIST OF NOTATION

| А               | =        | Antenna terminal, a constant (See Figure 13)                      |

|-----------------|----------|-------------------------------------------------------------------|

| с <sup>1</sup>  | =        | Junction Capacitance                                              |

| CP              | <i>=</i> | Package Capacitance                                               |

| с <sub>т</sub>  | =        | C <sup>b</sup> + C <sup>1</sup>                                   |

| d               | =        | Diode stack spacing                                               |

| Ŀ               | =        | Electric field intensity                                          |

| G               | =        | Conductance                                                       |

| ISOL            | =        | Isolation (ratio of forward bias to reverse<br>bias transmission) |

| L               | =        | Inductance                                                        |

| Ll              | =        | Internal Inductance                                               |

| <sup>L</sup> 2  | =        | External Inductance                                               |

| $L_{T}$         | Ξ        | $L_1 + L_2$                                                       |

| n               | =        | An exponent (See Figure 13)                                       |

| N               | =        | Number of Diodes                                                  |

| Р               | =        | Parallel (See Figure 23)                                          |

| R               | =        | Receiver terminal                                                 |

| R <sub>F</sub>  | =        | Forward bias resistance                                           |

| R<br>R          | =        | Reverse bias resistance                                           |

| S               | =        | Series (See Figure 23)                                            |

| <sup>t</sup> fr | =        | Forward to reverse blas switching time                            |

| v               | =        | Voltage                                                           |

| $v_{ji}$        | =        | Voltage across diode in stack                                     |

| V <sub>ST</sub> | =        | Voltage input to stack                                            |

| w               | =        | I region thickness                                                |

| х               | =        | Transmitter terminal                                              |

| Z <sub>o</sub>  | =        | Characteristic impedance                                          |

| (J)             | 2        | Angular frequency                                                 |

viii

### SECTION I

### INTRODUCTION

### 1. BACKGROUND

The existence of high peak power, short pulse sources has created a control problem. It is desirable to be able to switch such sources in and out of microwave networks in times which would make feasible such applications as Radar duplexing.

Since free space electromagnetic propagation is roughly one foot per nanosecond, devices with switching times on the order of 250 ns or less are desirable. Also, since sources with sub-nanosecond peak powers on the order of 10 MW are available, it is desirable for switch circuitry to be able to cope with the full output at useful repetition rates. Not only must the circuit elements pass such pulses with electromagnetic integrity, but they must be able to provide sufficient throughput along desired paths while providing sufficient isolation to others. Should it be desired to duplex a transmitter and receiver to a single antenna, a sensitive receiver must not see peak power levels of more than several watts during transmit, yet be available for reception within 250 ns. Meanwhile, the quality of the transmitted and received signal should not be significantly degraded. Given pulse widths on the order of 100 ps, this means instantaneous bandwidths of amplitude and phase fidelity on the order of 5 GHz, and a type of nondispersive circuitry uncommon to less transient signals.

Conventionally, high power duplexers utilize gas discharge tubes or ferrites to achieve the rf switching action. Such devices have been built with extremely high power handling capabilities. However, the gas clean-up and the associated long recovery time of the TR tubes is not attractive for the short pulse application. Although ferrite circulators and limiters possess many of the desired characteristics, inherent limitations in time response exist which reduce the protection afforded the receiver against main bang, the effects of high antenna mismatch and the return from large nearby targets. When a high power microwave pulse of sufficient amplitude to exceed a threshold value is applied to the ferrite, a uniform precession will build up

in the time order of  $10^{-8}$ s. Consequently, a leading edge spike problem is associated with these devices which make them relatively unattractive for sub-nanosecond short pulse application.

Semiconductor diodes have been used as microwave control elements for several years now. Characteristically, they have fast response, relatively low driving power, the ability to eliminate spike leakage, and the potential for long life. However, little or no information exists on the suitability of these elements for sub-nanosecond applications. Thus, it is apparent that investigation and characterization of the properties of semiconductor devices when subjected to short pulses is required.

### 2. PURPOSE OF PROGRAM

The object of this program is to develop PIN diode techniques which individually or in multiple can be used to switch 100 ps 20,000 V pulses in a 50 ohm non-dispersive transmission line. The diode switching time from non-conducting to conducting should be less than 250 ns. The turn-off time should be less than 500 ns.

### 3. WORK PERFORMED

During this program both theoretical and experimental investigations of the short pulse effects on semiconductor diodes were conducted.

In Section II, various types of individual PIN diodes mounted in both series and parallel configurations are characterized. Details of the test fixtures and the experimental procedures are discussed, and the findings are presented. The relative merits of different types of diodes are compared, and a new diode equivalent circuit for short pulse operation emerges.

In Section III, the diodes are combined into series mounted stacks and the theoretical and experimental properties of such stacks are described. Appropriate design criteria for diode stacking under short pulse conditions are developed. As a final evaluation, Section IV considers the embodiment of diode stacks into SPDT switch configurations for short pulse duplexing applications. Experimental results with a breadboard SPDT diode switch are shown and discussed.

The results of the program are summarized and conclusions made in Section V, while recommendations for future study and development are presented in Section VI.

within the state

### SECTION II

### DIODE CHARACTERIZATION

In this section, the concept of switching with individual diode elements is reviewed and the problems specifically associated with short pulse applications are discussed. Experimental results are presented showing the characteristics of various types of individual PIN diodes when subjected to short pulse stresses in series and in shunt. The relationship between the diode conductance and the impressed short pulse electric field then is developed. From this, a new equivalent circuit model of a reverse biased diode is established.

### 1. PIN DIODE PROPERTIES<sup>1</sup>

PIN type semiconductor diodes have been used for many years as microwave switching elements. The rf impedance of the diode may be switched from a usually small value in the forward biased, conducting state to another usually larger impedance in the non-conducting, reverse biased state. In an rf switching network, the diodes are incorporated into a transmission system in such a manner that a change in diode impedance results in a desired change in the rf signal transmission. The diode impedance is controlled via a dc bias circuit which must then be isolated from the signal circuit, usually by means of chokes and bypass capacitors.

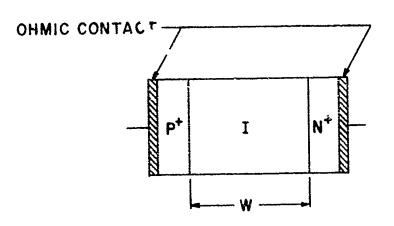

The ideal PIN diode structure is shown in Figure 1. The silicon diode usually consists of an intrinsic or very lightly doped I-region, with abrupt junctions to heavily doped  $P^+$  and  $N^+$  regions. Metalization layers and electrical contact are made to the highly doped diffused faces.

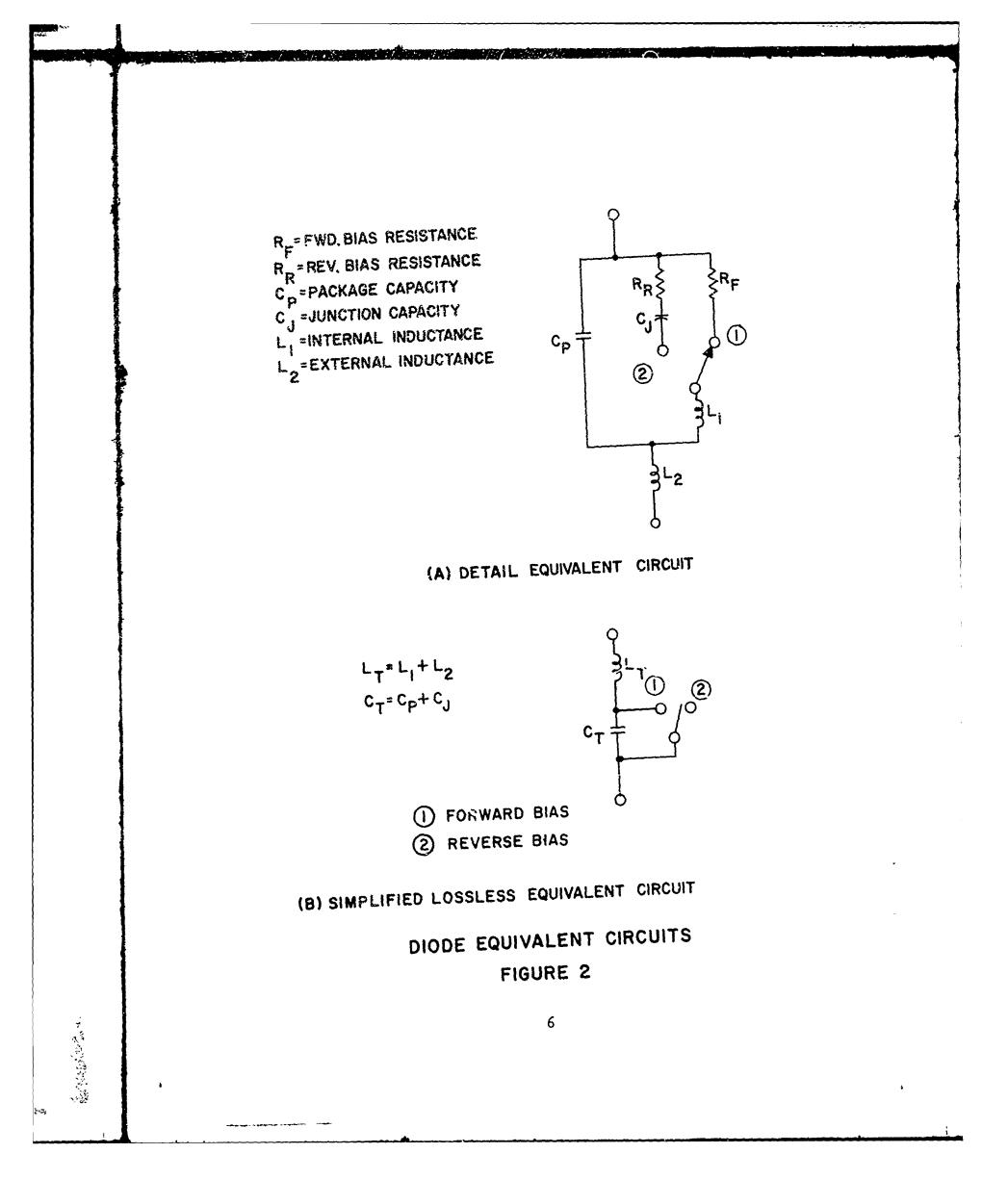

The commonly used equivalent circuit of the forward and reverse biased diode is presented in Figure 2. When the diode is forward biased, holes and electrons are injected into the I-layer from the  $P^+$  and  $N^+$  regions respectively. If the carrier lifetimes are relatively long, the I-region becomes flooded with carriers giving rise to the low resistance and inductive reactance of the forward biased diode. Under forward bias a carrier moves primarily by diffusion. Given a short pulse signal the transit

time of carriers in the I-region then can be much longer than the duration of the applied signal. Under such conditions, no rectification occurs for either positive or negative signal polarity. Such is the case for the 100 to 200 ps impulses used in this program.

When a diode is switched from the forward to reverse bias state by application of a reverse voltage, the current does not decay immediately because the excess carriers within the diode have a finite lifetime and the external circuit cannot remove them instantaneously. Transient currents are generated which decay as the space charge regions developing at the Ijunction become progressively wider and the residual charge is swept out. The diode impedance then rapidly increases as the voltage across the diode increases to a steady-state reverse-bias value. At this point the diode impedance looks essentially capacitive as shown in Figure 2A. It often is more convenient for many circuit design applications to use the simplified equivalent circuit model of the diode shown in Figure 2B.

Under conditions of high voltage short pulse excitation it is found that reverse bias conductivity as well as the capacitive character of the I-region must be taken into account. It is shown below that such conductivity is an increasing function of the electric field intensity in the bulk of the device. This necessitates a modification of the reverse bias equivalent circuit for the diode.

### 2. TEST FIXTURES

Two types of test fixtures were developed for mounting diodes in a 50 ohm transmission line structure. One accommodates diode mounting in series with the transmission line, while the other provides shunt mounting of the diode. The purpose of the test fixture is to allow investigation of the properties of the various types of PIN diodes under high power, short pulse stresses.

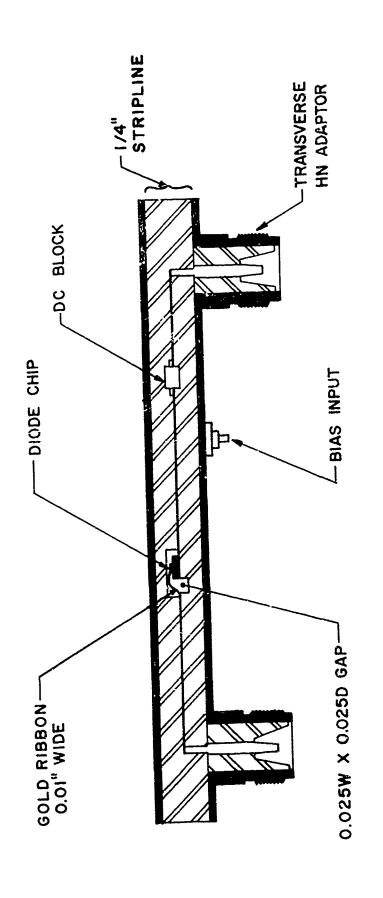

An assembly detail of the series mounting test fixture is shown in Figure 3. It is seen that the fixture is a stripline structure, with transverse HN adaptors for coupling the high voltage pulse signais into and out of the structure. The diode bias circuit is built into the fixture. A 200 nh coil connects the bias input to a point in the transmission line between the diode

7

and the states a

FIGURE 3

:

## DIODE TEST FIXTURE

Not to scale.

ЪĘ.

and the dc block. A similar coil provides a dc return path to ground on the other side of the diode. A 20 pF chip by-pass capacitor is used at the bias input. The purpose of the gap or transverse slot cut through the dielectric in the vicinity of the gold ribbon is not only to provide a mounting point for the series diode, but also to inhibit voltage tracking across the teflon-fibre-glass dielectric surface. A single gap without a diode can withstand a 150 ps pulse with an amplitude of approximately 13 kV before breaking down. The breakdown voltage can be increased to greater than 20 kV by air pressuri-zation to 50 p.s.i.

The transverse HN to stripline adaptors can transmit a 20 kV, 150 ps pulse with good fidelity. The VSWR of two adaptors joined by a length of 50 ohm stripline is 1.2:1. Similar adaptor results have been obtained using both 0.250" and 0.125" stripline ground plane spacing (GPS).

The voltage stress on a reverse biased, series mounted diode is twice that of a shunt mounted diode in the same impedance transmission line.<sup>2</sup> Further, it will be shown in Section IV that series mounting is fundamental to realizing a short pulse SPDT switch function. Thus, most emphasis has been placed on characterizing series diodes. However, for comparison purposes and completeness, some shunt mounted diodes were tested.

The shunt mounted diode test fixture consists of a length of GR 874 type coaxial transmission line. An Erie feed thru capacitor screwed into the outer coaxial conductor provides the mounting and bias contact for the diode under test. The diode-to-inner-conductor contact is insured by having a gold plated phosphor bronze fuzz button between these parts. All shunt-mounted diodes tested were sealed in glass or metal-ceramic packages, which have inherently more inductance than the non-packaged chips used in the series mounted tests.

### 3. EXPERIMENTAL APPARATUS

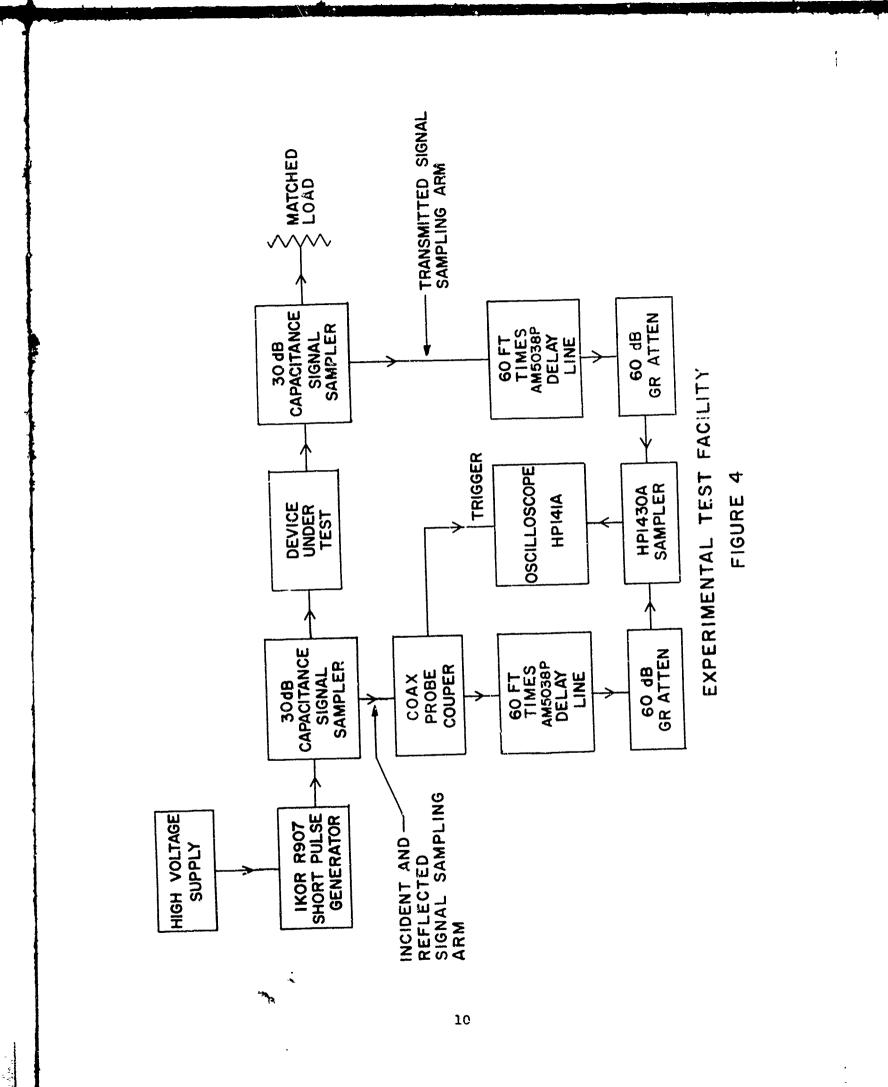

The experimental apparatus used to test the diodes is illustrated schematically in Figure 4. Shown are two capacitive signal samplers, one on either side of the device under test. One sampler is used to monitor the input and reflected signals from the device, while the other monitors the

Q

-

transmitted signals. The amplitude of the incident voltage is controlled by adjustment of the short pulse generator. Determination of the absolute value of the signals is made by careful calibration of the attenuation from the signal sampler to the input of the HP 1430A sampler.

The procedure for measuring the transmission and reflection coefficients is quite straightforward with this set up. The device first is removed from the circuit and a short length of transmission line is substituted. An adjustment of the gain of either of the two oscilloscope channel amplifiers is used to provide equal signal levels from the two samplers. The diode device then is substituted back into the circuit, and direct comparison can be made on the oscilloscope of the incident voltage, the reflected voltage and the transmitted voltage.

### 4. SERIES DIODE MEASUREMENTS

Using the measurement procedure described above, the transmission and reflection properties of various diodes were obtained.

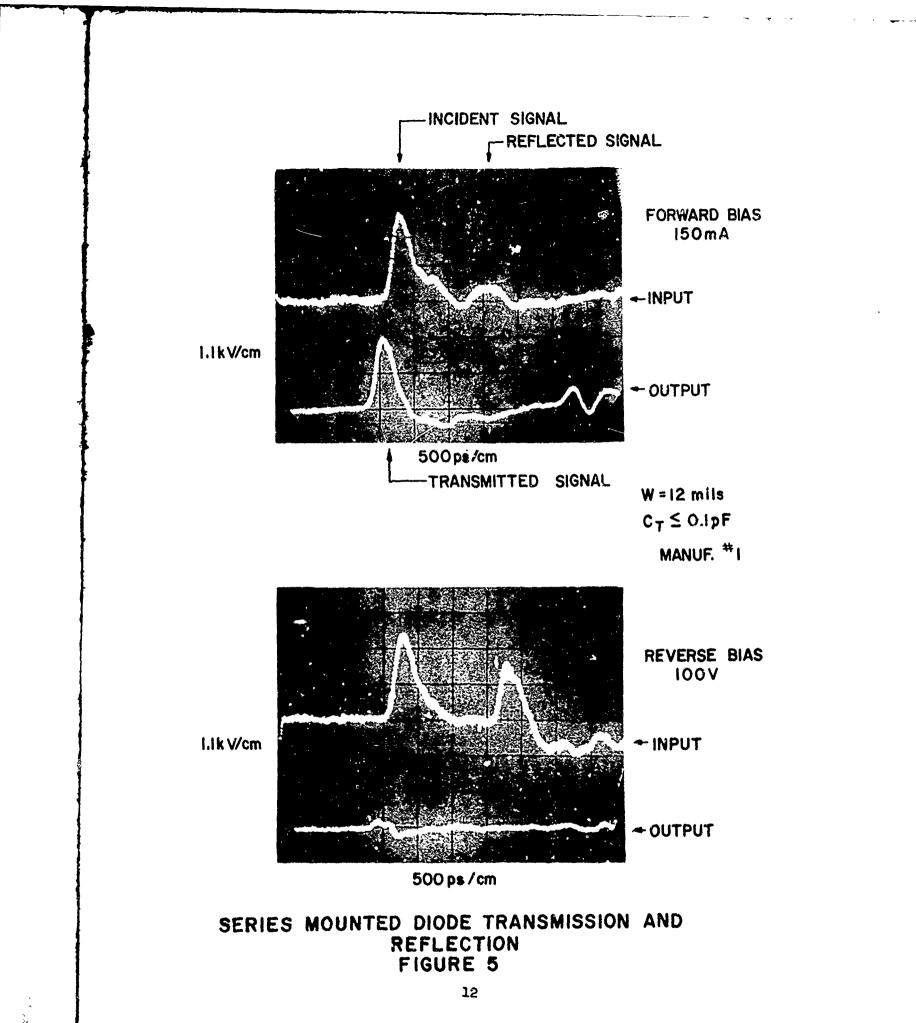

Photographs showing the typical reflection and transmission properties of a series mounted diode are presented in Figure 5. All scales are linear. The upper and lower photographs correspond to the forward bias and the reverse bias characteristics respectively. Comparing the two traces in the upper photograph we see that the forward bias insertion loss is 2.0 dB. The slight displacemer of the peak amplitudes between the traces is attributed to a small difference in delay within the measuring system. The small bump in the upper trace 1.5 ns after the incident voltage is due to reflections from the diode. The magnitude of the reflection shown is attributed mostly to the length of gold ribbon which joins the upper contact of the diode to the transmission line. The small peaks in the tail of the output response result from load reflections.

The lower photograph indicates a signal isolation of greater than 22 dB when the diode is switched to 100 V reverse bias. The signal transmitted in the isolation state loses fidelity because of the frequency dependent nature of the diode capacitive reactance. Further, as shown, most of the energy is reflected.

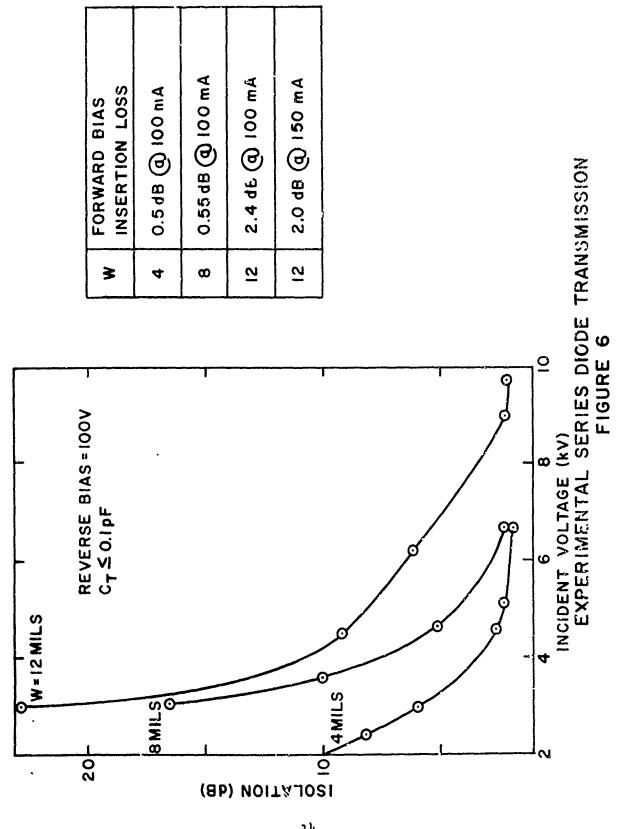

In general, the forward bias characteristics of the diode are found to remain the same for all incident voltage stresses up to 20 kV, the maximum voltage applied. Pulse fidelity is retained and no adverse effects are noted in the transmission properties. However, as the incident voltage is increased, the isolation in the reverse bias state decreases. The point at which this occurs has been found to depend on the I-region thickness of the diode. This is shown in Figure 6 where the reverse bias isolation versus incident voltage is plotted for diodes with different I-region thickness. Generally, the greater the I-region thickness the greater the isolation. However, as indicated from the table of forward bias insertion loss in Figure 6, the series resistance of the diode also increases with I-region thickness. Further, it is found that varying the bias voltage from 0 to 250 V has negligible effects on the dicde isolation characteristics. Thus, the reduction in isolation does not appear to be nearly as critically dependent on the width of the depletion region as on the overall I-region thickness.

An effort was made to determine if the observed decrease in isolation was due to surface or bulk resistivity changes. Various diode encapsulants such as Dow Corning 646 were applied to the diodes. Also, the air surrounding the diode was pressurized to 100 p.s.i. None of these experiments appeared to change the isolation characteristics. It therefore seems likely that the mechanism is internal to the diode and not a surface effect.

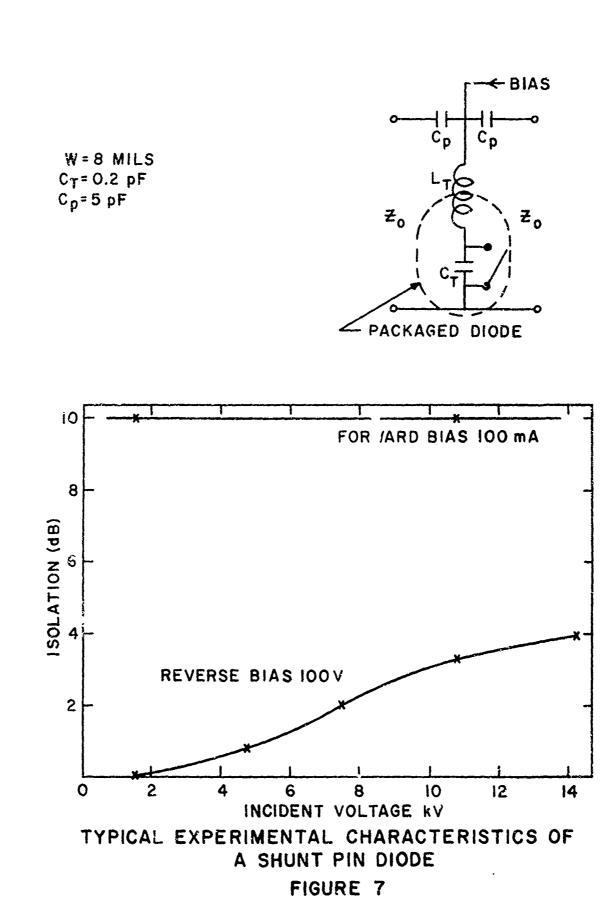

### 5. SHUNT DIODE MEASUREMENTS

Experimental measurements were made on various packaged diodes mounted in shunt. Typical transmission characteristics of a shunt mounted diode are shown in Figure 7 for both the forward and reverse bias states. The reverse bias state corresponds to the low loss transmitting mode, which progressivly becomes more lossy as the incident voltage increases. In the shunt configuration, a large change in diode conductance is required before any applicable non-linear effects are observed in the transmission characteristics.

In the forward bias state the isolation is the order of 10 dB. This low value is attributed to the inductance,  $L_{T}$ , which primarily results from the

**.**

ŝ,

,

Ł

diode package. The isolation could be increased by resonating the parasitic elements. However, this clearly indicates why a packaged diode configuration is unsuitable as a switch function over the multi-octave bands required for short pulse operation.

In addition to monitoring the shunt diode transmission characteristics, an effort was made to observe the diode pulse current. This was done by placing a current meter or a current probe in the bias lead. The attempt was not completely successful, since part of the diode current always passed through the by-pass capacitors,  $C_p$ . However, by monitoring the portion of the diode current passing through the bias lead, changes in the diode leakage current could be observed as the short pulse voltage stresses were increased. Generally changes in the leakage current could be observed before any noticeable changes in the transmission characteristics occurred. Quite often application of the input signal resulted in permanent deterioration of the reverse voltage leakage current. However, permanent 'eterioration in the transmission characteristics was not observed. Detailed characterizations of the diode I-V curve, before and after the application of the short pulse stress, were not made.

### 6. DIODE SWITCHING TIME

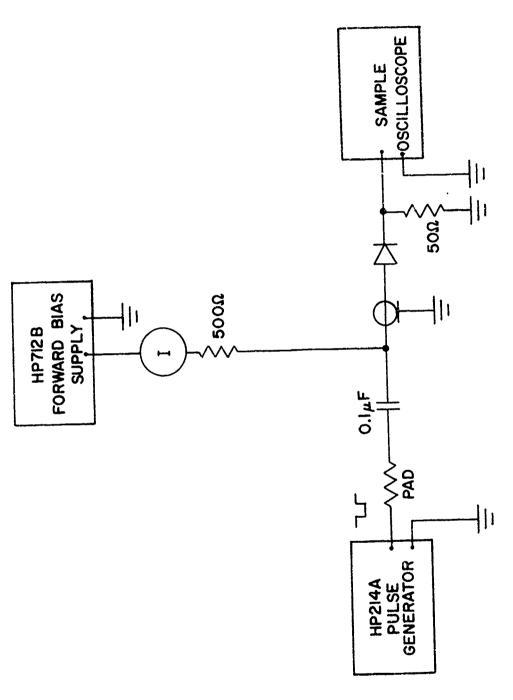

The circuit employed for measuring the switching time characteristics of the diodes is shown in Figure 8. The switching time may be defined as the time taken for the diode current to decay from 90% to 10% of the initial current. This is an extremely conservative estimate of the switching time since the rf impedance of the diode changes substantially only near the beginning of the current decay. A summary of the typical switching times of the diodes tested is shown in Figure 9.

### 7. DIODE CONDUCTANCE

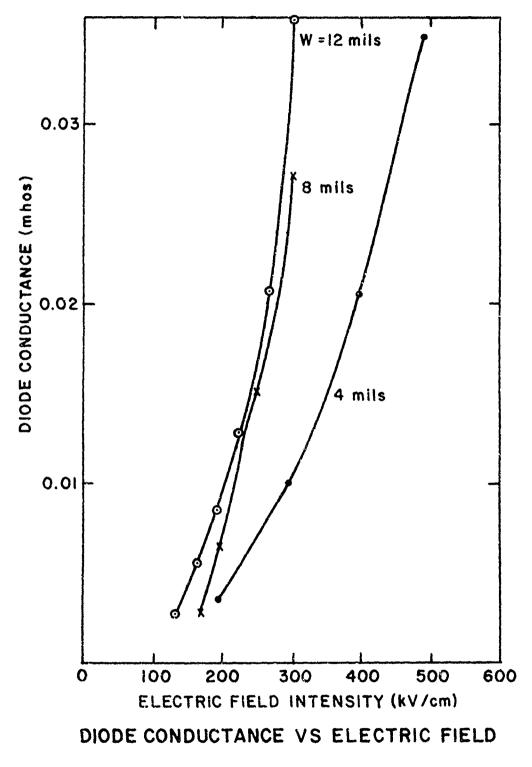

A plot of conductance, G, versus electric field intensity, E, is given in Figure 10 for various PIN diode structures. These curves are derived from the data presented previously in Figure 6 using the assumption of a uniform, ideal parallel plate capacitor field. Below 100 kV/cm the

### FIGURE 8

Hand Barrier, a

# DIODE SWITCHING TIME MEASUREMENT CIRCUIT

1

1

i 1

| 0.1        |

|------------|

| 0.1        |

| 0.55       |

| 0.65       |

| <u>ک.5</u> |

1

FIGURE 9

TYPICAL DIODE CHARACTERISTICS

\* <sup>†</sup> = TIME REQUIRED TO SWITCH FROM A FORWARD BIAS CURRENT OF <sup>†</sup> IOOMA TO A STEADY REVERSE VOLTAGE OF IOOV. MEASURED FROM THE IO% AND 90% POINTS OF THE TRANSIENT CURRENT WAVEFORM.

ł

FIGURE 10

conductance falls to the point where the diode capacitive reactance becomes the major impedance to transmission. In the range 100 to 250 kV/cm, the conductance increases rapidly with field and asymptotes to a linear behavior observed in the 250 to 500 kV/cm range. It should be noted that the above behavior is very similar to that observed by J. N. Park, et al.<sup>3</sup> in nearintrinsic silicon using voltage pulses of 20  $\mu$ s duration. However, the field intensity under short pulse excitation is approximately a factor of 10 greater for the same effects. It appears that under such intense field conditions, electrons and holes that are present in equilibrium in the Iregion are accelerated and create additional hole-electron pairs by bulk ionization of the lattice structure. The electron-hole pairs then accelerate and generate further pairs resulting in avalanche multiplication.

### 8. NEW DIODE EQUIVALENT CIRCUIT

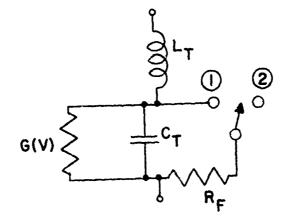

It has been shown that the conductivity of the I-region is highly dependent on the electric field intensity. Thus the reverse bias equivalent circuit of a PIN diode previously presented is inadequate to describe the behavior of the diode under high level short pulse excitation. An alternate simplified equivalent circuit of a reverse biased PIN under short pulse conditions is shown in Figure 11. The capacitive reactance of the diode is shunted by a conductance, G(V), which is a function of the applied voltage.

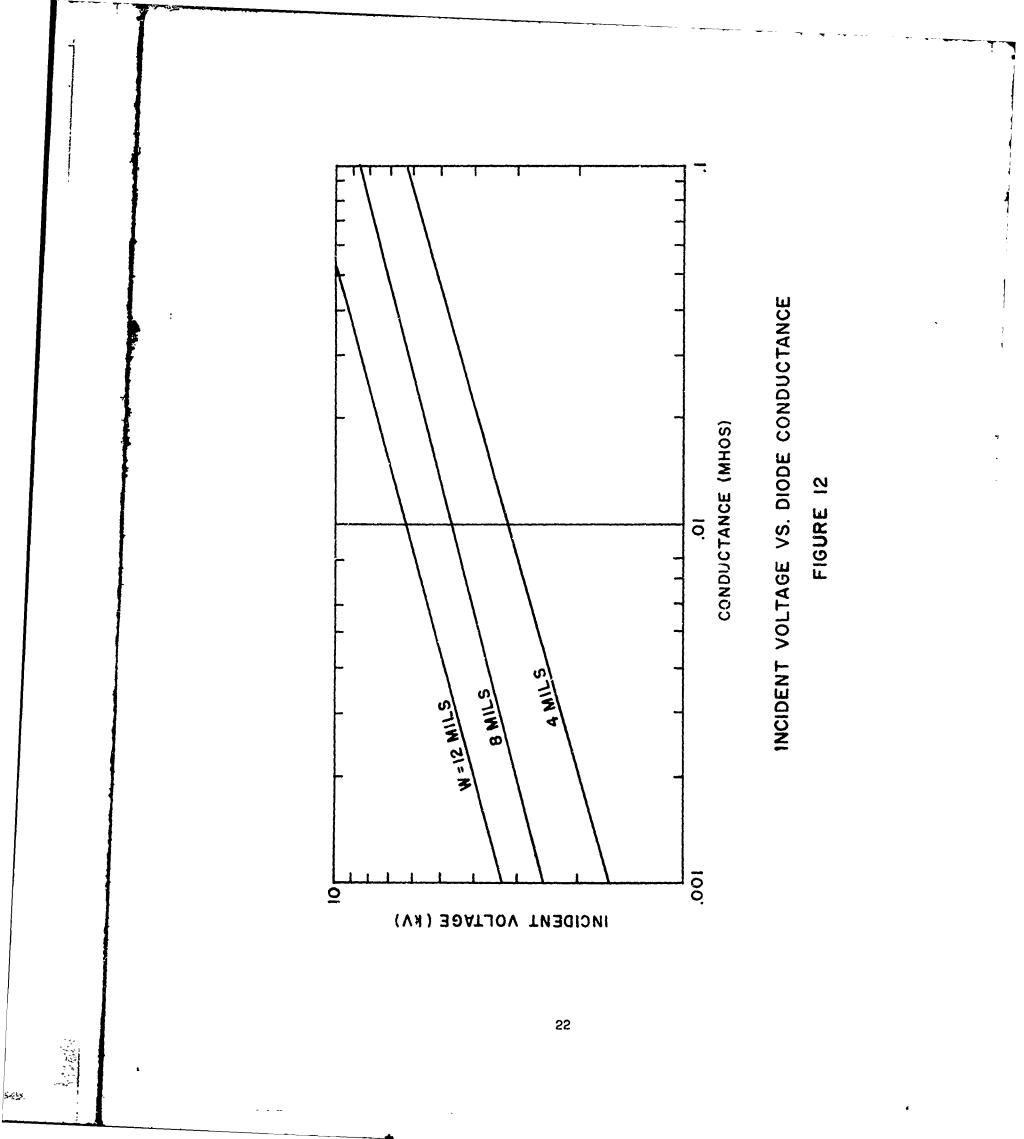

Since the inductance,  $L_T$ , is small for an unpackaged diode, one may neglect  $L_T$  and directly relate the conductance to the applied voltage. A summary of the relationship between diode conductance and applied voltage for the various diodes tested is presented in Figures 12 and 13. Note that the data appears to be well defined by the relationship  $G = AV^n$ .

2 REVERSE BIAS

### SHORT PULSE SIMPLIFIED EQUIVALENT CIRCUIT

| G | = | A | ٧ | , | 1 |  |

|---|---|---|---|---|---|--|

|---|---|---|---|---|---|--|

| MANUFACTURER    | W<br>(MILS)       | n                           | A<br>(mhos/kvolt)                                                                              |

|-----------------|-------------------|-----------------------------|------------------------------------------------------------------------------------------------|

| <br> <br> <br>2 | 4<br>8<br>12<br>8 | 3.01<br>2.86<br>3.04<br>2.0 | -4<br>$2 \times 10^{-4}$<br>$3 \times 10^{-5}$<br>$1.5 \times 10^{-5}$<br>$1.6 \times 10^{-3}$ |

**REVERSE** BIAS = 100VDIODE CAPACITANCE  $\leq 0.1 \text{ pF}$

### SUMMARY INCIDENT VOLTAGE VS. CONDUCTANCE

•

FIGURE 13

23

war and a set and the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the set of the

### SECTION III

### DIODE STACKS

We now turn to a discussion of the theoretical and experimental properties of a stack of closely mounted series diodes in a transmission line.

### 1. ANALYTIC RESULTS

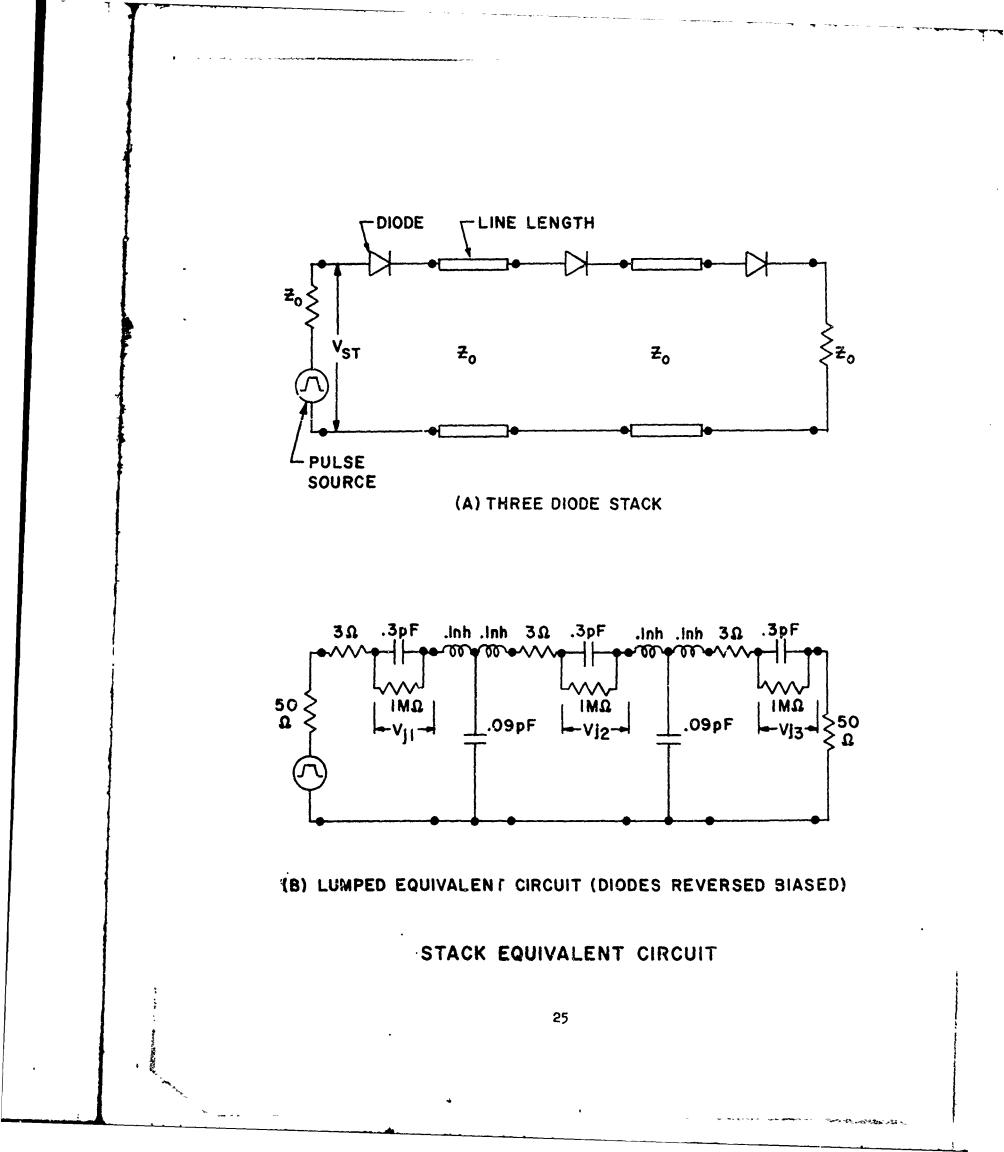

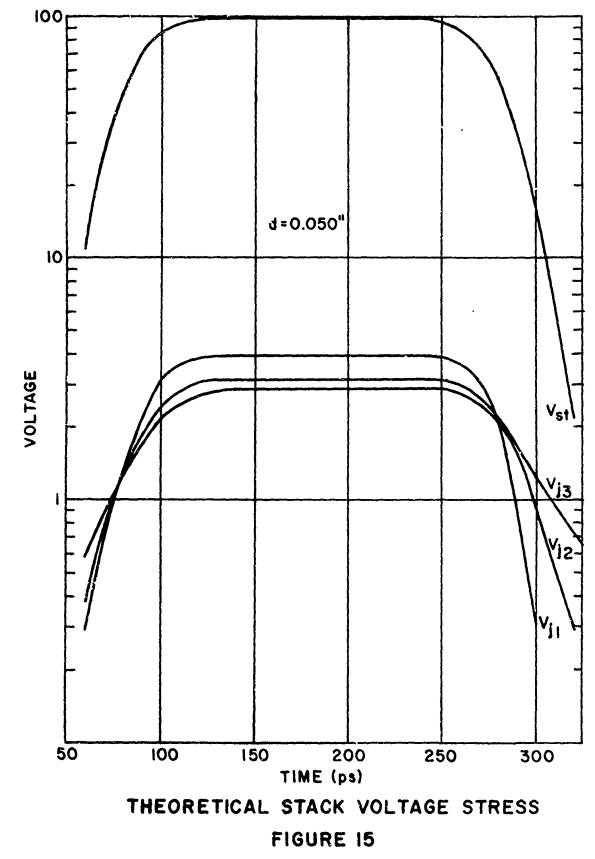

The short time domain signals being considered here present several problems not usually encountered in microwave design. Since the signals being used have transients of well under 100 ps duration, the propagation sequence through a dicde stack becomes important. If the diode stacking is to be most effective in reverse bias, it is desirable for the signal voltage to be evenly distributed across all the diodes. With a short risetime on the leading edge of the signal, it is possible that the voltage stress on the first diodes may build to inordinate levels before the voltage wave can propagate across the following diodes in the stack. As shown in Section II, this would significantly increase the conductance of each diode in turn to a higher level than would a more evenly distributed voltage, thereby significantly decreasing the overall isolation capabilities of the stack. To check the possible occurrence of such a "domino" reaction, and to determine the effect of the reverse biased stack on pulse integrity, a time domain transient analysis was carried out.

A computer circuit analysis program was utilized to examine stack properties. The program performs a linear transient pulse response analysis on a simulated diode stack. The three diode series arrangement chosen for analysis is represented by the circuit shown in Figure 14. The source pulse is represented by 50 ps linear rise and fall times separated by a 150 ps constant amplitude, for a total duration of 250 ps. The three reverse biased diodes are each represented by a 0.3 pF capacitor with a 1 Mohm resistor in shunt and a 3 ohm resistor in series. The diodes are separated by 0.050" lengths of 50 ohm air line which are simulated by low pass LC filter structures. It should be noted that the program is not capable of performing the non-linear transient analysis required if the 1 Mohm shunt resistor were to be a function of the input voltage,  $V_{St}$ .