# UNCLASSIFIED

# AD NUMBER

## AD489661

# NEW LIMITATION CHANGE

TO

Approved for public release, distribution unlimited

## FROM

Distribution authorized to U.S. Gov't. agencies and their contractors; Administrative/Operational Use; Jul 1966. Other requests shall be referred to Rome Air Development Center, Griffiss AFB, NY.

# AUTHORITY

RADC USAF ltr, 17 Sep 1971

THIS PAGE IS UNCLASSIFIED

RADC -TR- 65-397, Vol II FINAL REPORT

**9 9**

6000

ま

# ANALYSIS OF SMALL ASSOCIATIVE MEMORIES FOR DATA STORAGE AND RETRIEVAL SYSTEMS

VOLUME II, TECHNICAL DISCUSSION

Robert S. Green, Dr. Jack Minker, and Warren E. Shindle

## TECHNICAL REPORT NO. RADC-TR-65-397, Vol II

July 1966

This document is subject to special export controls and each transmittal to foreign governments or foreign nationals may be made only with prior approval of RADC (EMLI), GAFB, N.Y. 13440.

Rome Air Development Center Research and Technolog: Division Air Force Systems Command Griffies Air Force Base, New York

# ANALYSIS OF SMALL ASSOCIATIVE MEMORIES FOR DATA STORAGE AND RETRIEVAL SYSTEMS

VOLUME II. TECHNICAL DISCUSSION

Robert S. Green, Dr. Jack Minker, and Warren E. Shindle

This document is subject to special export controls and each transmittal to foreign governments or foreign nationals may be made only with prior approval of RADC (EMLI), GAFB, N.Y. 13440.

MAINE ENDINERLING HARLE NHAME, N.J. 19726/64

#### FOREWORD

This report was prepared by the Auerbach Corp., Philadelphia, Pa.; under Contract Number AF30(602)-3564; Project Number 4594 and Task Number 459402. The RADC project engineer is Ronald J. Ferris, EMID.

This is a final report and covers the period of work from October 1964 to September 1965; the originator's report number is 1231-TR2.

The results of this study are contained in two volumes: Volume I presents in summary form, an introduction, findings, conclusions, and recommendations. In additicn, this volume contains a discussion on associative memories and the comparative analyses of the associative memory configurations studied. A short critique of the Goodyear Associative Processor and a bibliography are also given in this volume.

Volume II contains the detailed discussion of the study. This volume specifies the problem of "how" the study was conducted. It presents the technical details, the relevant flowcharts, algorithms, and encoding. Each section of this volume contains information pertinent to the approach, technical details, and the findings and conclusions. Supplementary information relevant to the study is contained in the appendices.

The principal investigators on this study were Mr. James Dugan, Mr. Robert Snaw Green (Project Engineer - hardware related studies), Mrs. Renee Jasper, Mr. Marvin Katz, Dr. Jack Minker (Program Manager), Mr. James Mulford, and Mr. Warren E. Shindle (Project Engineer - problem analysis and programming related studies). The authors would like to express their appreciation to the numerous members of the AUERBACH technical staff who were called upon for expert advice on specialized areas of study. These are: Mr. George Ncborak, Mr. Sheldon Einhorn, Mr. Don Russel, Mr. Ken Rose, Mr. Lawrence Feidelman, Mr. Ralph Howe, Mr. Arthur Hughes, Mr. Stephen Leibholz, Mr. Lester Probst, Mr. Robert Rossheim, and Dr. Jerome Salle.

Release of subject report to the general public is prohibited by the Strategic Trade Control Program, Mutual Defense Assistance Control List (revised 6 January 65), published by the Department of State.

This technical report has been reviewed and is approved.

Gowan Approved: ROBERT J. QUINN, Colonel, USAF Chief, Intel and Info

Processing Div

Chief, Info Processing Branch

FOR THE COMMANDER: For A ) I and Y Chief, Advanced Studies Group

## TABLE OF CONTENTS (Summary of Volumes I and II)

**5**.2

•

## VOLUME I

## Management Report

| Section I    | Management Summary                                                      | 1-1 |

|--------------|-------------------------------------------------------------------------|-----|

| Section II   | Discussion and Comparative Analyses of Associative<br>Memories          | 2-1 |

| Section III  | Critique of the Goodyear Aerospace Corporation<br>Associative Processor | 3-1 |

| Bibliography |                                                                         | B-1 |

## VOLUME II

## Technical Discussion

| Section I    | Introduction.                                    | 1-1 |

|--------------|--------------------------------------------------|-----|

| Section II   | Hybrid Associative Configurations                | 2-1 |

| Section III  | The Sea Surveillance Problem                     | 3-1 |

| Section IV   | Data Base                                        | 4-1 |

| Section V    | Input Message Processing                         | 5-1 |

| Section VI   | File Maintenance                                 | 6-1 |

| Section VII  | Query Processing                                 | 7-1 |

| Section VIII | Comparison of the A2 and GAP Associative Systems | 8-1 |

| Appendix A   | Preliminary Programming Manual for the Goodyear  |     |

|              | Associative Processor                            | A-1 |

| Appendix B   | Detailed Timing Equations                        | B-1 |

| Appendix C   | Routines                                         | C-1 |

iii

## TABLE OF CONTENTS, VOLUME II

. . .

0

| Section  |                                                     | Page  |

|----------|-----------------------------------------------------|-------|

| I        | INTRODUCTION                                        | 1-1   |

| 1.1      | Overall Scope of RADC Associative Memory Program    | 1-2   |

| 1.2      | Study Considerations                                | 1-3   |

| 1.3      | Problem Selection                                   | 1-6   |

| 1.4      | Study Restrictions                                  | 1-10  |

| 1.5      | Summary of Volume II Contents                       | 1-10  |

| п        | HYBRID ASSOCIATIVE CONFIGURATIONS                   | 2-1   |

| 2.1      | Introduction                                        | 2-1   |

| 2.2      | Ground Rules                                        | 2~1   |

| 2.3      | Associative Memories                                | 2-2   |

| 2.4      | Hy rid Configuration Parameters and Possibilities   | 2-10  |

| 2.5      | Description and Logic of the Configurations Studied | 2-20  |

| 2.6      | Timing of Associative Memory Configuration          | 2-78  |

| 2.7      | Cost                                                | 2-94  |

| 2.8      | Comparison of Configurations                        |       |

| 2.9      | Comments on the 1604-B                              | 2-108 |

| ПІ       | THE SEA SURVEILLANCE PROBLEM                        | 3-1   |

| 3.1      | XIntroduction                                       | 3-1   |

| 3.2      | Data Base Contents.                                 | 3-2   |

| 3.3      | Input Message Processing                            | 3-3   |

| 34       | Maintenance Operations                              | 3-4   |

| 3.5      | Query Operations                                    | 3-5   |

| 3.6      | System Constraints                                  | 3-8   |

| 3.7      | Statistics                                          | 3-9   |

| 3.8      | Evaluation                                          | 3-9   |

| žV       | DATA BASE                                           | 4-1   |

| 4.1      | Introduction.                                       | 4-1   |

| 4.2      | File Structures and File Design Considerations      | 4-1   |

| 4.3      | Multi-List Structure for Sea Surveillance Problem   | 4-9   |

| 4.4      | Physical Record Layout                              | 4-20  |

| 4.5      | Influence of Associative Memories on Data Base      | 4-27  |

| 4.6      | Organization                                        |       |

| <b>.</b> |                                                     | 4-01  |

iv

## TABLE OF CONTENTS, VOLUME II (Cont.)

| V         INPUT MESSAGE PROCESSING         5-1           5.1         Introduction.         5-1           5.2         Input Message - Procedural Logic.         5-3           5.3         Attribute Spiit Routine.         5-4           5.4         Sub-String Processor .         5-20           5.5         Maintenance Order Generators.         5-20           5.5         Maintenance Order Generators.         5-20           6.1         Introduction.         6-1           6.1         Introduction.         6-1           6.2         File Maintenance Problems Peculiar to This System         6-3           6.3         Description of the File Maintenance Order -         6-4           6.4         File Maintenance Order Families         6-5           6.5         Transaction Codes         6-5           6.6         File Maintenance Processing         6-6           6.7         Assembler         6-13           6.8         Router         6-13           6.9         Executing Routines         6-13           6.10         Related Transaction Routine         6-29           6.11         Family Control and Write         6-30           VII         QUERY PROCESSING         7-1 | Section |                                                   | Page |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------------------------------------|------|

| 5.2       Input Message - Procedural Logic.       5-3         5.3       Attribute Split Routine.       5-4         5.4       Sub-String Processor       5-20         5.5       Maintenance Order Generators       5-26         VI       FILE MAINTENANCE.       6-1         6.1       Introduction.       6-1         6.2       File Maintenance Problems Peculiar to This System       6-3         6.3       Description of the File Maintenance Order       6-4         6.4       File Maintenance Order Families       6-5         6.5       Transaction Codes       6-5         6.6       File Maintenance Processing       6-6         6.7       Assembler       6-7         6.8       Router       6-13         6.9       Executing Routines       6-13         6.10       Related Transaction Routine       6-29         6.11       Family Control and Write       6-30         VII       QUERY PROCESSING       7-1         7.1       Introduction       7-1         7.2       User's Query Language.       7-16         7.4       Run Routine.       7-39         7.5       Controller       7-46         7.6       <                                                                               | V       | INPUT MESSAGE PROCESSING                          | 5-1  |

| 5.3       Attribute Split Routine.       5-4         5.4       Sub-String Processor       5-20         5.5       Maintenance Order Generators       5-26         VI       FILE MAINTENANCE.       6-1         6.1       Introduction.       6-1         6.2       File Maintenance Problems Peculiar to This System       6-3         6.3       Description of the File Maintenance Order       6-4         6.4       File Maintenance Order Families       6-5         6.5       Transaction Codes       6-5         6.6       File Maintenance Processing       6-6         6.7       Assembler       6-7         6.8       Router       6-13         6.9       Executing Routines       6-13         6.10       Related Transaction Routine.       6-29         6.11       Family Control and Write       6-30         VII       QUERY PROCESSING       7-1         7.1       Introduction.       7-1         7.2       User's Query Language.       7-1         7.3       Query Pre-Processor.       7-16         7.4       Run Routine.       7-39         7.5       Controller       7-53         7.7       Queries<                                                                                   | 5.1     | Introduction.                                     | 5-1  |

| 5.4       Sub-String Processor       5-20         5.5       Maintenance Order Generators       5-26         VI       FILE MAINTENANCE       6-1         6.1       Introduction       6-1         6.2       File Maintenance Problems Peculiar to This System       6-3         6.3       Description of the File Maintenance Order       6-4         6.4       File Maintenance Order Families       6-5         6.5       Transaction Codes       6-5         6.6       File Maintenance Processing       6-6         6.7       Assembler       6-7         6.8       Router       6-13         6.9       Executing Routines       6-13         6.10       Related Transaction Routine       6-29         6.11       Family Control and Write       6-30         VII       QUERY PROCESSING       7-1         7.1       Introduction       7-1         7.2       User' s Query Language       7-1         7.3       Query Pre-Processor       7-16         7.4       Run Routine       7-39         7.5       Controller       7-53         7.7       Queries       7-66         7.8       Output Functions <t< td=""><td>5.2</td><td>Input Message - Procedural Logic</td><td>5-3</td></t<>                | 5.2     | Input Message - Procedural Logic                  | 5-3  |

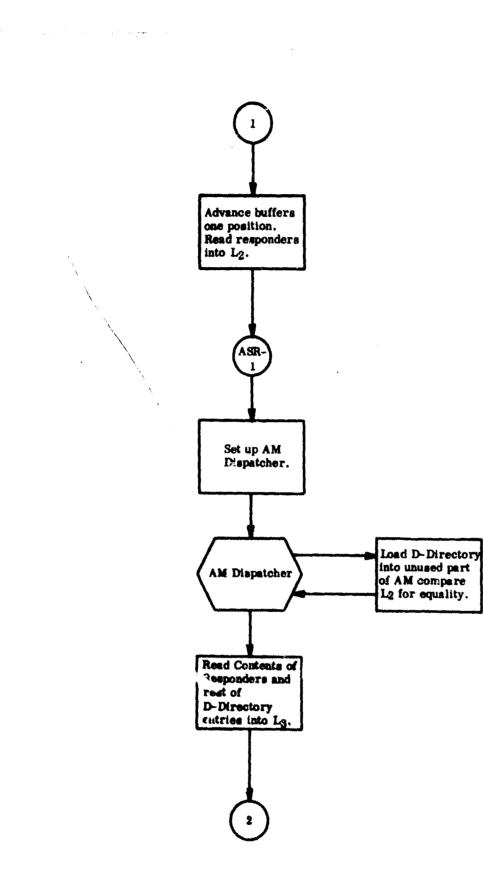

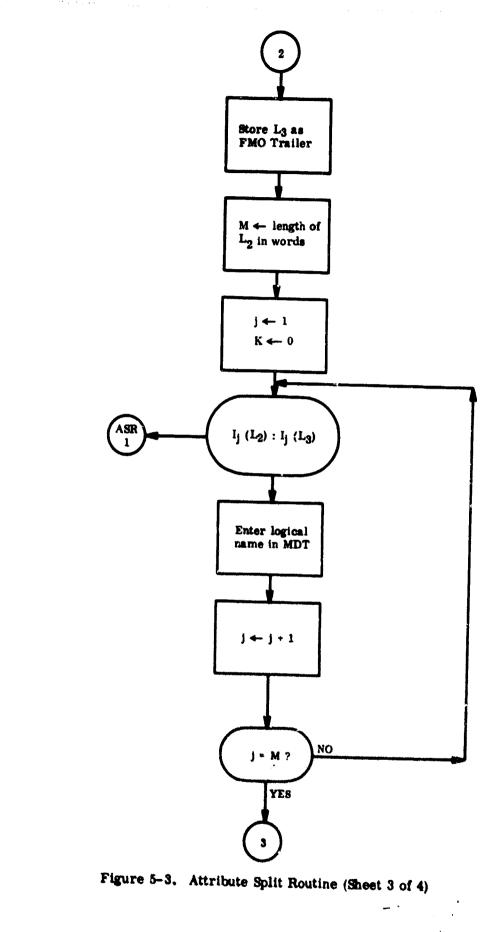

| 5.5       Maintenance Order Generators.       5-26         VI       FILE MAINTENANCE.       6-1         6.1       Introduction.       6-1         6.2       File Maintenance Problems Peculiar to This System       6-3         6.3       Description of the File Maintenance Order       6-4         6.4       File Maintenance Order Families       6-5         6.5       Transaction Codes       6-6         6.6       File Maintenance Processing       6-6         6.7       Assembler       6-7         6.8       Router       6-7         6.9       Executing Routines       6-13         6.10       Related Transaction Routine.       6-29         6.11       Family Control and Write       6-30         VII       QUERY PROCESSING       7-1         7.1       Introduction.       7-1         7.2       User's Query Language.       7-1         7.3       Query Pre-Processor.       7-16         7.4       Run Routine.       7-53         7.5       Controller       7-46         7.6       Input Routine.       7-53         7.7       Queries       7-66         7.8       Output Functions <t< td=""><td>5.3</td><td>Attribute Split Routine.</td><td>5-4</td></t<>                        | 5.3     | Attribute Split Routine.                          | 5-4  |

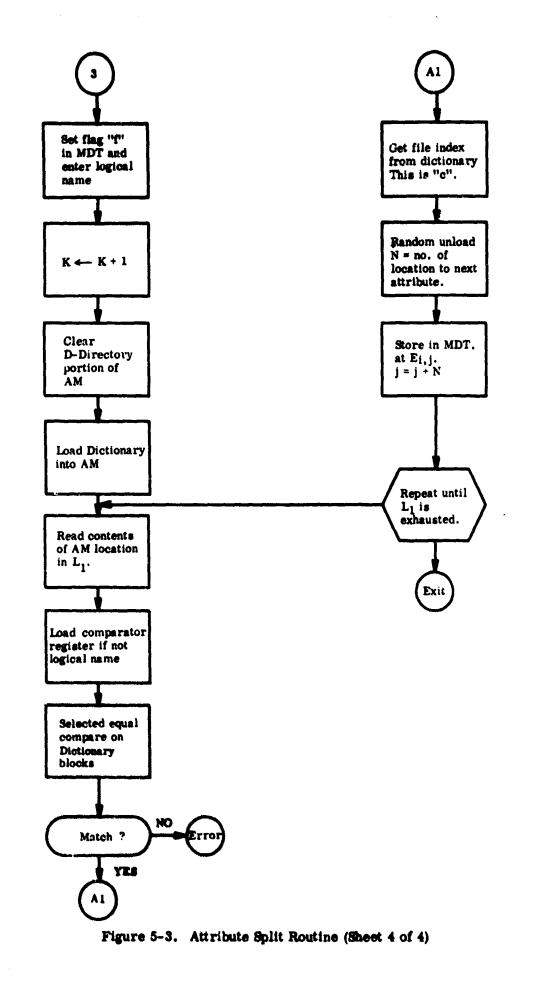

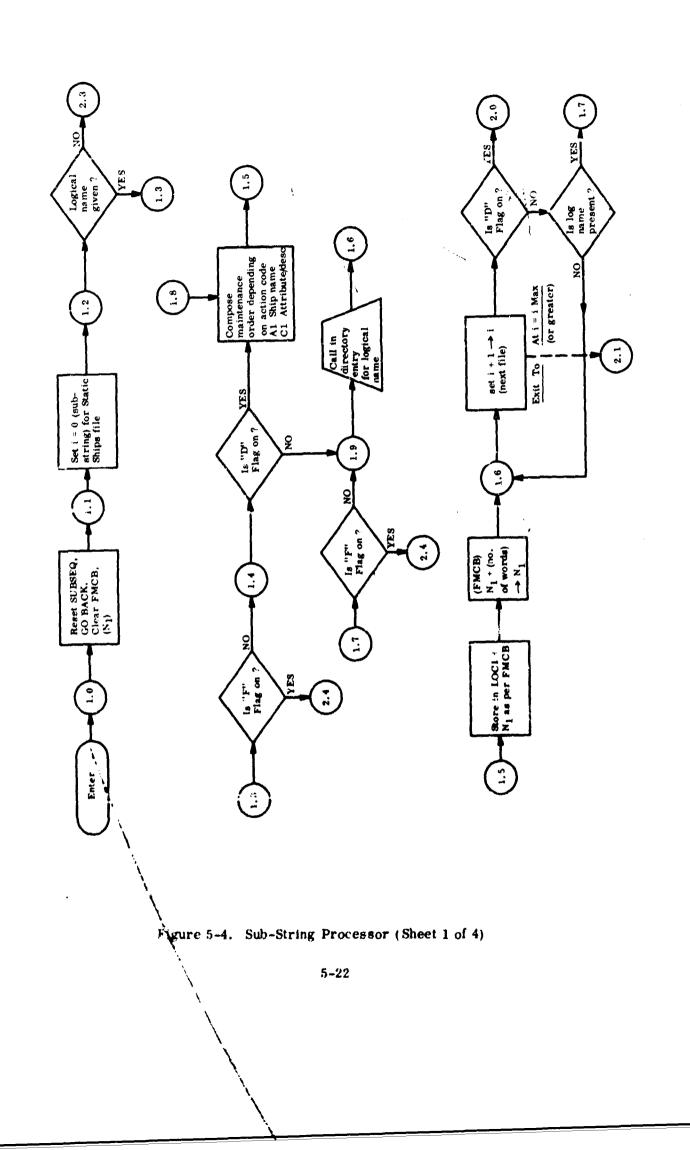

| VI       FILE MAINTENANCE.       6-1         6.1       Introduction.       6-1         6.2       File Maintenance Problems Peculiar to This System       6-3         6.3       Description of the File Maintenance Order       6-4         6.4       File Maintenance Order Families       6-5         6.5       Transaction Codes       6-5         6.6       File Maintenance Processing       6-6         6.7       Assembler       6-7         6.8       Router       6-7         6.9       Executing Routines       6-13         6.9       Executing Routines       6-13         6.10       Related Transaction Routine       6-29         6.11       Family Control and Write       6-30         VII       QUERY PROCESSING       7-1         7.1       Introduction.       7-1         7.2       User's Query Language.       7-1         7.3       Query Pre-Processor.       7-16         7.4       Run Routine.       7-39         7.5       Controller       7-46         7.6       Input Routine.       7-53         7.7       Queries       7-70         7.8       Output Functions       7-70                                                                                                  | 5.4     | Sub-String Processor                              | 5-20 |

| 6.1       Introduction.       6-1         6.2       File Maintenance Problems Peculiar to This System       6-3         6.3       Description of the File Maintenance Order       6-4         6.4       File Maintenance Order Families       6-5         6.5       Transaction Codes       6-6         6.6       File Maintenance Processing       6-6         6.7       Assembler       6-7         6.8       Router       6-13         6.9       Executing Routines       6-13         6.10       Related Transaction Routine       6-29         6.11       Family Control and Write       6-30         VII       QUERY PROCESSING       7-1         7.1       Introduction       7-1         7.2       User's Query Language       7-1         7.3       Query Pre-Processor       7-16         7.4       Run Routine       7-39         7.5       Controller       7-46         7.6       Input Routine       7-53         7.7       Queries       7-70         7.8       Output Functions       7-70         7.9       Tag Memory       7-80         VIII       COMPARISON OF THE A2 AND GAP ASSOCIATIVE                                                                                               | 5.5     | Maintenance Order Generators                      | 5-26 |

| 6.2       File Maintenance Problems Peculiar to This System       6-3         6.3       Description of the File Maintenance Order       6-4         6.4       File Maintenance Order Families       6-5         6.5       Transaction Codes       6-5         6.6       File Maintenance Processing       6-6         6.7       Assembler       6-7         6.8       Router       6-13         6.9       Executing Routines       6-13         6.10       Related Transaction Routine       6-29         6.11       Family Control and Write       6-30         VII       QUERY PROCESSING       7-1         7.1       Introduction       7-1         7.2       User's Query Language       7-1         7.3       Query Pre-Processor       7-16         7.4       Run Routine       7-39         7.5       Controller       7-53         7.7       Queries       7-66         7.8       Output Functions       7-70         7.9       Tag Memory       7-80         VIII       COMPARISON OF THE A2 AND GAP ASSOCIATIVE       8-1         8.1       Introduction       8-1                                                                                                                                 | VI      | FILE MAINTENANCE                                  | 6-1  |

| 6.3       Description of the File Maintenance Order                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6.1     |                                                   | 6-1  |

| 6.4       File Maintenance Order Families       6-5         6.5       Transaction Codes       6-5         6.6       File Maintenance Processing       6-6         6.7       Assembler       6-7         6.8       Router       6-7         6.9       Executing Routines       6-13         6.10       Related Transaction Routine       6-29         6.11       Family Control and Write       6-30         VII       QUERY PROCESSING       7-1         7.1       Introduction       7-1         7.2       User's Query Language       7-1         7.3       Query Pre-Processor       7-16         7.4       Run Routine       7-39         7.5       Controller       7-46         7.6       Input Routine       7-53         7.7       Queries       7-70         7.9       Tag Memory       7-80         VIII       COMPARISON OF THE A2 AND GAP ASSOCIATIVE       8-1         8-1       Introduction       8-1                                                                                                                                                                                                                                                                                         | 6.2     | File Maintenance Problems Peculiar to This System | 6-3  |

| 6.5       Transaction Codes       6-5         6.6       File Maintenance Processing       6-6         6.7       Assembler       6-7         6.8       Router       6-13         6.9       Executing Routines       6-13         6.10       Related Transaction Routine       6-29         6.11       Family Control and Write       6-30         VII       QUERY PROCESSING       7-1         7.1       Introduction       7-1         7.2       User's Query Language       7-1         7.3       Query Pre-Processor       7-16         7.4       Run Routine       7-39         7.5       Controller       7-53         7.7       Queries       7-66         7.8       Output Functions       7-70         7.9       Tag Memory       7-80         VIII       COMPARISON OF THE A2 AND GAP ASSOCIATIVE<br>SYSTEMS       8-1         8.1       Introduction.       8-1                                                                                                                                                                                                                                                                                                                                     | 6.3     | -                                                 | 6-4  |

| 6.6       File Maintenance Processing       6-6         6.7       Assembler       6-7         6.8       Router       6-13         6.9       Executing Routines       6-13         6.10       Related Transaction Routine.       6-29         6.11       Family Control and Write       6-30         VII       QUERY PROCESSING       7-1         7.1       Introduction.       7-1         7.2       User's Query Language.       7-1         7.3       Query Pre-Processor.       7-16         7.4       Run Routine.       7-39         7.5       Controller       7-53         7.7       Queries       7-66         7.8       Output Functions       7-70         7.9       Tag Memory       7-80         VIII       COMPARISON OF THE A2 AND GAP ASSOCIATIVE       8-1         8.1       Introduction.       8-1                                                                                                                                                                                                                                                                                                                                                                                         | 6.4     | File Maintenance Order Families                   | 6-5  |

| 6.7       Assembler       6-7         6.8       Router       6-13         6.9       Executing Routines       6-13         6.10       Related Transaction Routine       6-29         6.11       Family Control and Write       6-30         VII       QUERY PROCESSING       7-1         7.1       Introduction       7-1         7.2       User's Query Language       7-1         7.3       Query Pre-Processor       7-16         7.4       Run Routine       7-39         7.5       Controller       7-53         7.7       Queries       7-66         7.8       Output Functions       7-70         7.9       Tag Memory       7-80         VIII       COMPARISON OF THE A2 AND GAP ASSOCIATIVE       8-1         8.1       Introduction       8-1                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6.5     | Transaction Codes                                 | 6-5  |

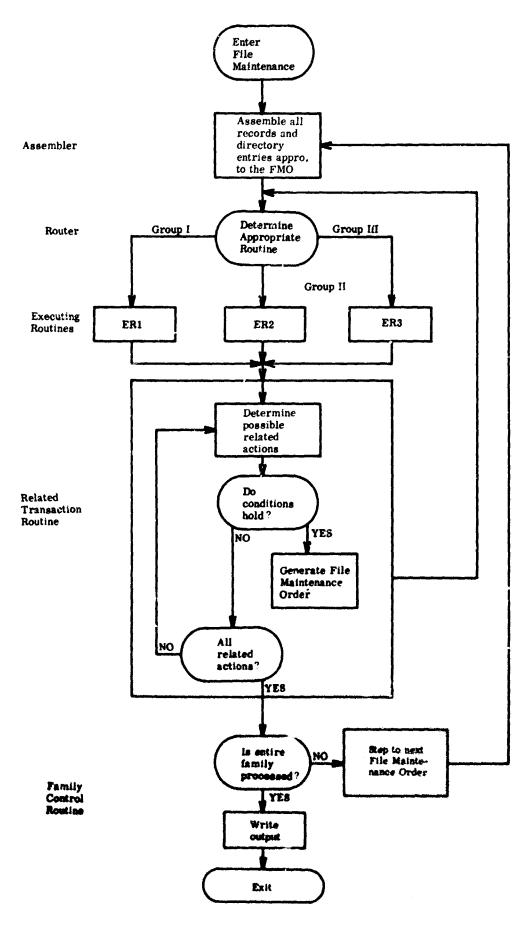

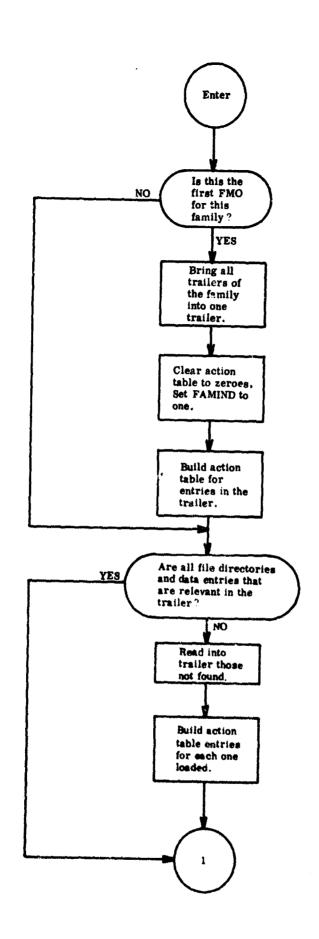

| 6.8       Router       6-13         6.9       Executing Routines       6-13         6.10       Related Transaction Routine.       6-29         6.11       Family Control and Write       6-30         VII       QUERY PROCESSING       7-1         7.1       Introduction.       7-1         7.2       User's Query Language.       7-1         7.3       Query Pre-Processor.       7-16         7.4       Run Routine.       7-39         7.5       Controller       7-46         7.6       Input Routine.       7-53         7.7       Queries       7-66         7.8       Output Functions       7-70         7.9       Tag Memory       7-80         VIII       COMPARISON OF THE A2 AND GAP ASSOCIATIVE SYSTEMS       8-1         8.1       Introduction.       8-1                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6.6     | -                                                 | 6-6  |

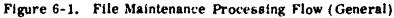

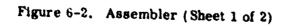

| 6.9       Executing Routines.       6-13         6.10       Related Transaction Routine.       6-29         6.11       Family Control and Write       6-30         VII       QUERY PROCESSING       7-1         7.1       Introduction.       7-1         7.2       User's Query Language.       7-1         7.3       Query Pre-Processor.       7-16         7.4       Run Routine.       7-39         7.5       Controller       7-46         7.6       Input Routine.       7-53         7.7       Queries       7-66         7.8       Output Functions       7-70         7.9       Tag Memory       7-80         VIII       COMPARISON OF THE A2 AND GAP ASSOCIATIVE       8-1         8.1       Introduction.       8-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6.7     | Assembler                                         | 6-7  |

| 6. 10       Related Transaction Routine.       6-29         6. 11       Family Control and Write       6-30         VII       QUERY PROCESSING       7-1         7. 1       Introduction.       7-1         7. 2       User's Query Language.       7-1         7. 3       Query Pre-Processor.       7-16         7. 4       Run Routine.       7-39         7. 5       Controller       7-46         7. 6       Input Routine.       7-53         7. 7       Queries       7-66         7. 8       Output Functions       7-70         7. 9       Tag Memory       7-80         VIII       COMPARISON OF THE A2 AND GAP ASSOCIATIVE SYSTEMS       8-1         8.1       Introduction.       8-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6.8     |                                                   | 6-13 |

| 6.11       Family Control and Write       6-30         VII       QUERY PROCESSING       7-1         7.1       Introduction       7-1         7.2       User's Query Language       7-1         7.3       Query Pre-Processor       7-16         7.4       Run Routine       7-39         7.5       Controller       7-46         7.6       Input Routine       7-53         7.7       Queries       7-66         7.8       Output Functions       7-70         7.9       Tag Memory       7-80         VIII       COMPARISON OF THE A2 AND GAP ASSOCIATIVE SYSTEMS       8-1         8.1       Introduction       8-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6.9     | Executing Routines                                | 6-13 |

| VII       QUERY PROCESSING       7-1         7.1       Introduction.       7-1         7.2       User's Query Language.       7-1         7.3       Query Pre-Processor.       7-16         7.4       Run Routine.       7-39         7.5       Controller       7-46         7.6       Input Routine.       7-53         7.7       Queries       7-66         7.8       Output Functions       7-70         7.9       Tag Memory       7-80         VIII       COMPARISON OF THE A2 AND GAP ASSOCIATIVE SYSTEMS       8-1         8.1       Introduction.       8-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6.10    | Related Transaction Routine                       | 6-29 |

| 7.1       Introduction.       7-1         7.2       User's Query Language.       7-1         7.3       Query Pre-Processor.       7-16         7.4       Run Routine.       7-39         7.5       Controller       7-46         7.6       Input Routine.       7-53         7.7       Queries       7-66         7.8       Output Functions       7-70         7.9       Tag Memory       7-80         VIII       COMPARISON OF THE A2 AND GAP ASSOCIATIVE<br>SYSTEMS       8-1         8.1       Introduction.       8-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6.11    | Family Control and Write                          | 6-30 |

| 7.2       User's Query Language.       7-1         7.3       Query Pre-Processor.       7-16         7.4       Run Routine.       7-39         7.5       Controller       7-46         7.6       Input Routine.       7-53         7.7       Queries       7-66         7.8       Output Functions       7-79         7.9       Tag Memory       7-80         VIII       COMPARISON OF THE A2 AND GAP ASSOCIATIVE<br>SYSTEMS       8-1         8.1       Introduction.       8-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | VII     | QUERY PROCESSING                                  | 7-1  |

| 7.3       Query Pre-Processor.       7-16         7.4       Run Routine.       7-39         7.5       Controller       7-46         7.6       Input Routine.       7-53         7.7       Queries       7-66         7.8       Output Functions       7-79         7.9       Tag Memory       7-80         VIII       COMPARISON OF THE A2 AND GAP ASSOCIATIVE       8-1         8.1       Introduction.       8-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         | Introduction                                      | 7-1  |

| 7.4       Run Routine.       7-39         7.5       Controller       7-46         7.6       Input Routine.       7-53         7.7       Queries       7-66         7.8       Output Functions       7-70         7.9       Tag Memory       7-80         VIII       COMPARISON OF THE A2 AND GAP ASSOCIATIVE       8-1         8.1       Introduction.       8-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -       | · –                                               |      |

| 7.5       Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •       | -                                                 |      |

| 7.6       Input Routine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -       | Run Routine                                       | 7-39 |

| 7.7       Queries       7-66         7.8       Output Functions       7-79         7.9       Tag Memory       7-80         VIII       COMPARISON OF THE A2 AND GAP ASSOCIATIVE<br>SYSTEMS       8-1         8.1       Introduction       8-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -       |                                                   |      |

| 7.8       Output Functions       7-79         7.9       Tag Memory       7-80         VIII       COMPARISON OF THE A2 AND GAP ASSOCIATIVE<br>SYSTEMS       8-1         8.1       Introduction       8-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -       | -                                                 |      |

| 7.9       Tag Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         | -                                                 |      |

| VIII       COMPARISON OF THE A2 AND GAP ASSOCIATIVE<br>SYSTEMS,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |                                                   |      |

| SYSTEMS         8-1           8.1         Introduction         8-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7,9     | Tag Memory                                        | 7-80 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | VIII    |                                                   | 8-1  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8.1     | Introduction.                                     | 8-1  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8.2     |                                                   | 8-2  |

v

( and

## TABLE OF CONTENTS, VOLUME II (Cont.)

~

## Section

Page

× 2

1

## Appendices

| Α | PRELIMINARY PROGRAMMING MANUAL FOR THE GOODYEAR<br>ASSOCIATIVE PROCESSOR | A-1 |

|---|--------------------------------------------------------------------------|-----|

| B | DETAILED TIMING EQUATIONS                                                | B-1 |

| С | ROUTINES                                                                 | C-1 |

## LIST OF ILLUSTRATIONS, VOLUME II

D:

Contraction and

| rigure |                                                                                               | Page          |

|--------|-----------------------------------------------------------------------------------------------|---------------|

| 1-1    | Problem Selection Possibilities vs. Selection Criteria                                        | 1-9           |

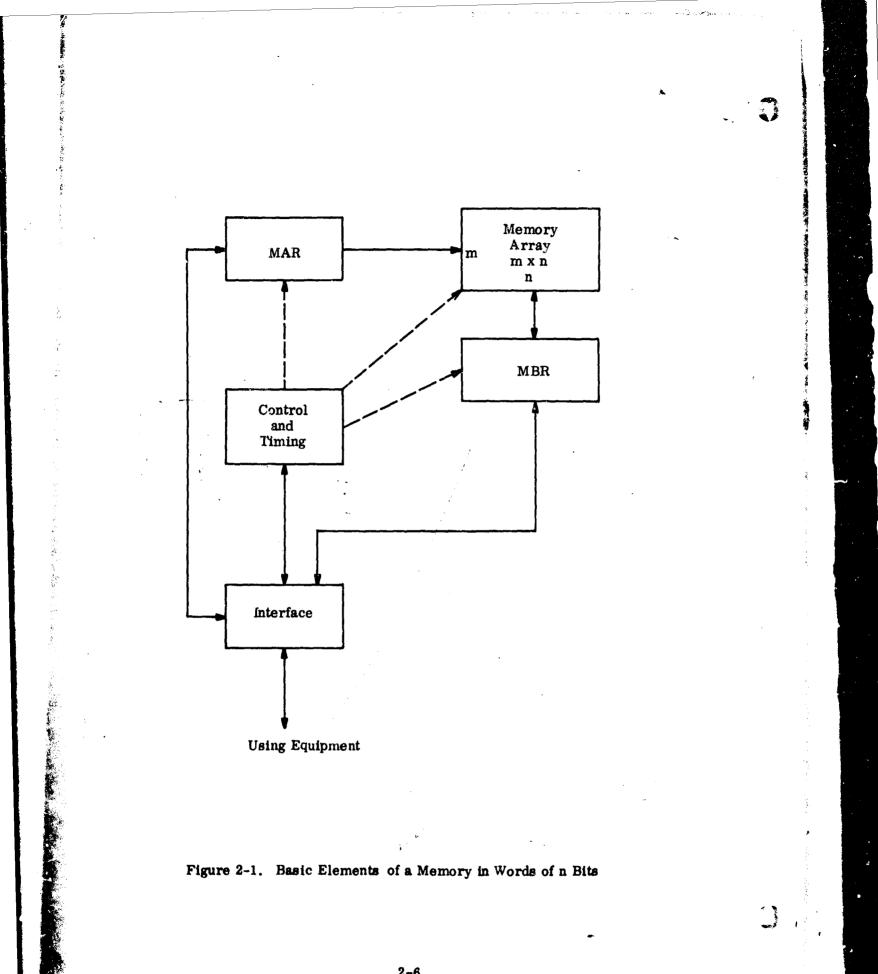

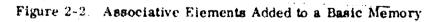

| 2-1    | Basic Elements of a Memory in Words of n Bits                                                 | 2-6           |

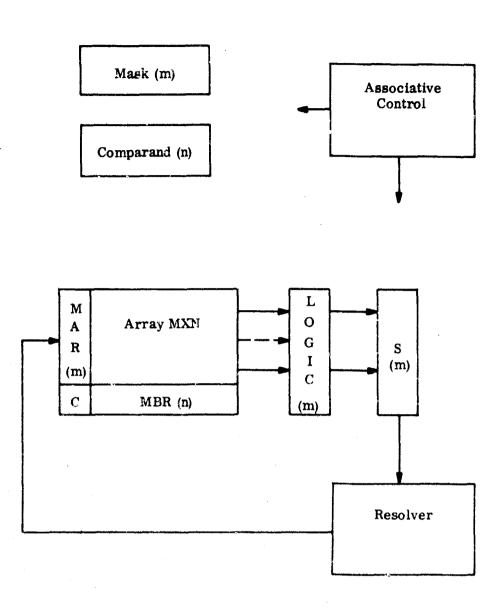

| 2-2    | Associative Elements Added to a Basic Memory                                                  | 2-7           |

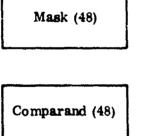

| 2-3    | GAP Associative Implementation                                                                | 2-9           |

| 2-4    | Elements of Associative Technology                                                            | 2-11          |

| 2-5    | Associative Memory Parameters                                                                 | 2-13          |

| 2-6    | Possible Searches                                                                             | 2-14          |

| 2-7    | AM Logic Mechanization Possibilities                                                          | 2-16          |

| 2-8    | Connection and Configuration Parameters                                                       | 2-19          |

| 2-9    | AM Logic Mechanization Possibilities                                                          | 2-21          |

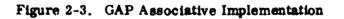

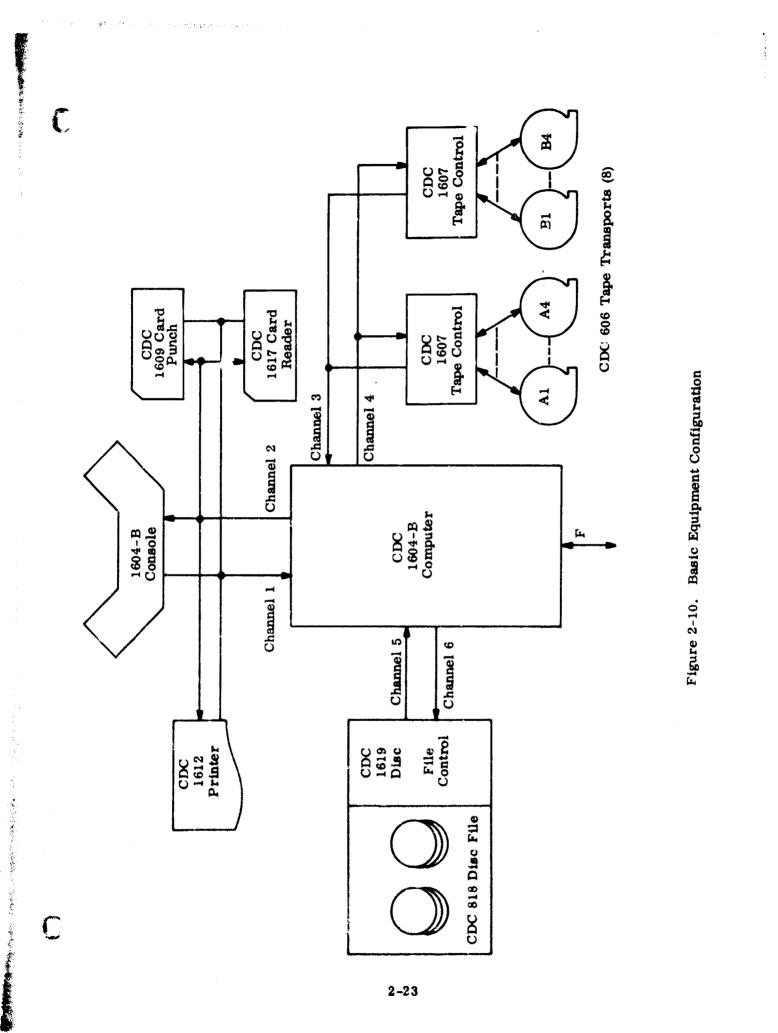

| 2-10   | Basic Equipment Configuration                                                                 | 2-23          |

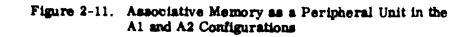

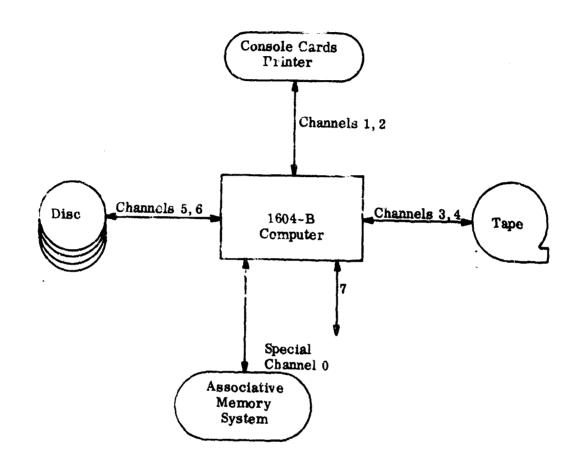

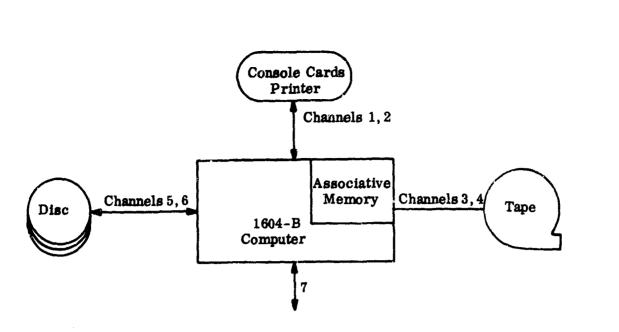

| 2-11   | Associative Memory as a Peripheral Unit in the A1 and A2<br>Configurations                    | 2-24          |

| 2-12   | Associative Memory in the GAP Peripheral Device Configuration via a Direct Access Channel.    | 2-25          |

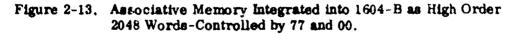

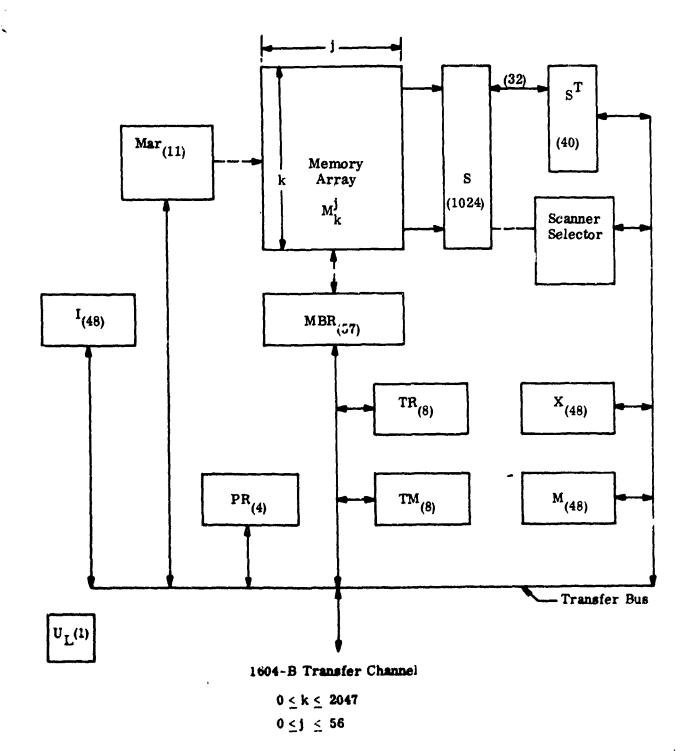

| 2-13   | Associative Memory Integrated into 1604-B as High Order 2048<br>Words-Controlled by 77 and 00 | 2-26          |

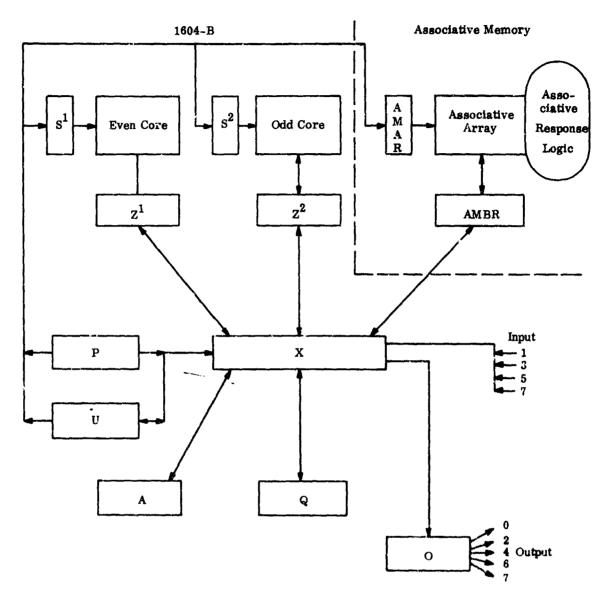

| 2-14   | Detail of Integrated Associative Memory Configuration                                         | 2-27          |

| 2-15   | Block Diagram of GAP Connected to the 1604-B Computer                                         | 2-30          |

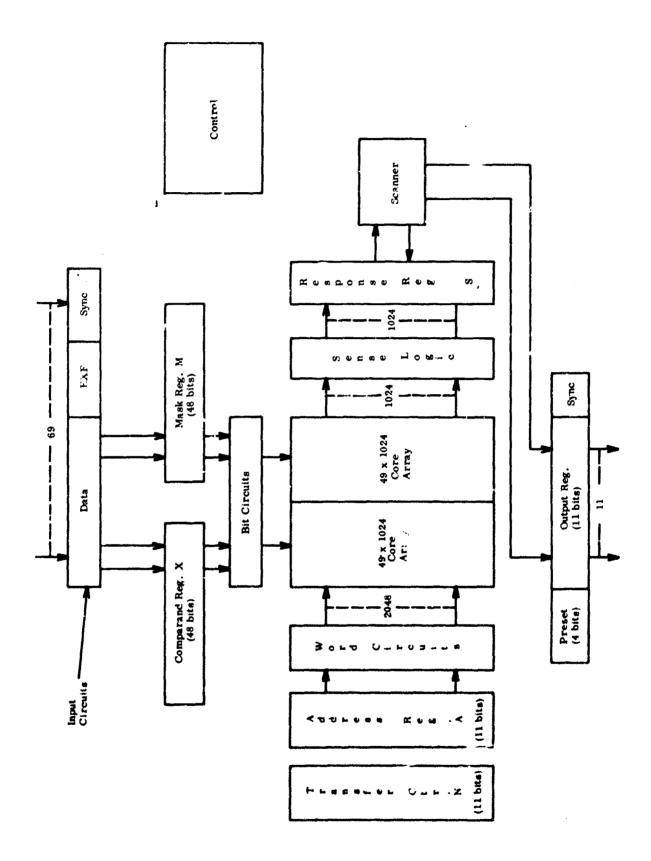

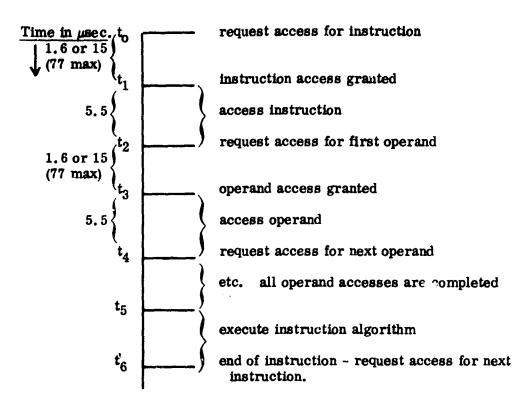

| 2-16   | Logic Block Diagram for Small AM                                                              | 2- <b>3</b> 5 |

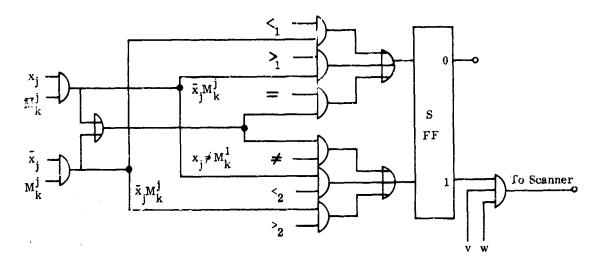

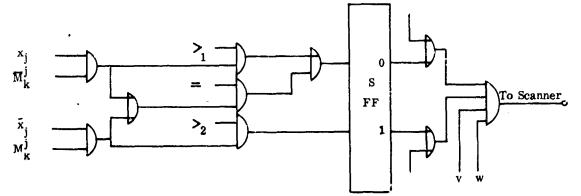

| 2-17   | Logic Cross Section                                                                           | 2-37          |

| 2-18   | Alternate Logic Configurations                                                                | 2-38          |

| 2-19   | Search Algorithms                                                                             | 2-43          |

| 2-20   | Register Block Diagram - Model A2                                                             | 2-51          |

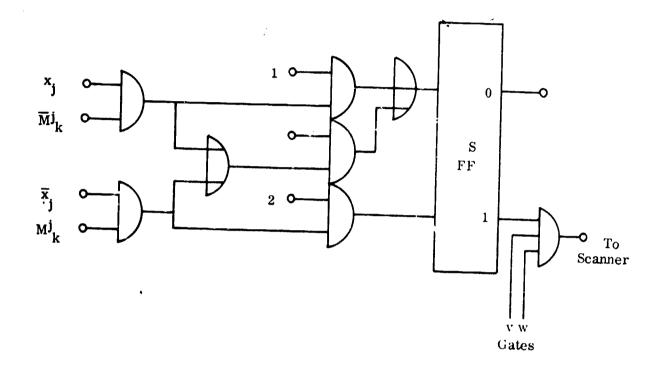

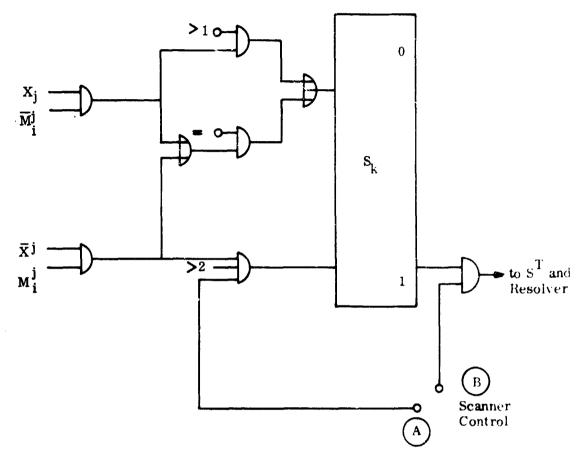

| 2-21   | S Register Logic, One Stage                                                                   | 2-53          |

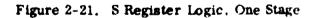

| 2-22   | A3 1604-B Associative Memory Integrated Configurations                                        | 2-66          |

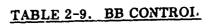

| 2-23   | Instruction Execution Sequence                                                                | 2-81          |

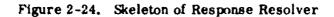

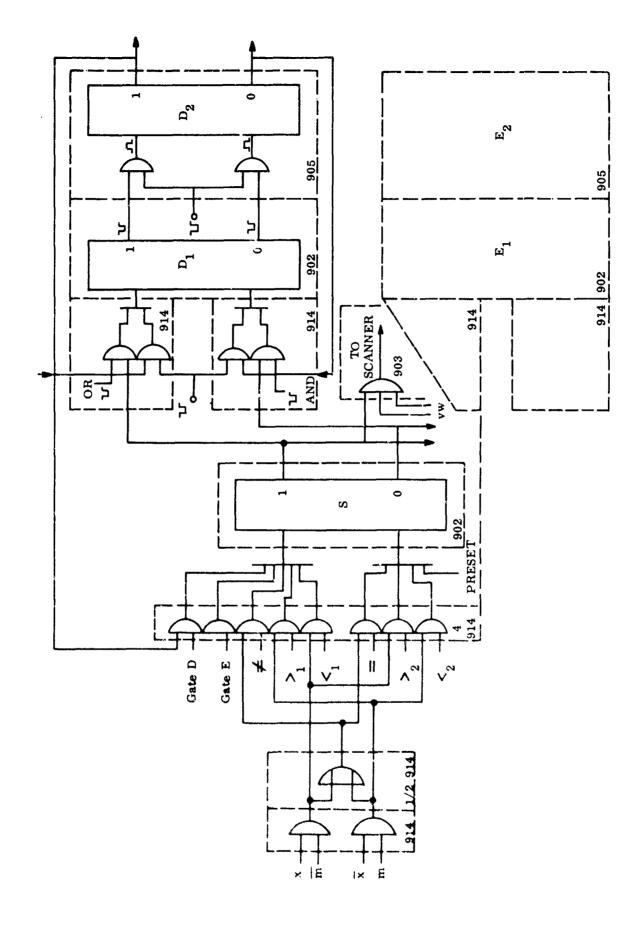

| 2-24   | Skeleton of Response Resolver                                                                 | 2-83          |

# LIST OF ILLUSTRATIONS, VOLUMI (Cont.)

## Figure

## Page

Į.

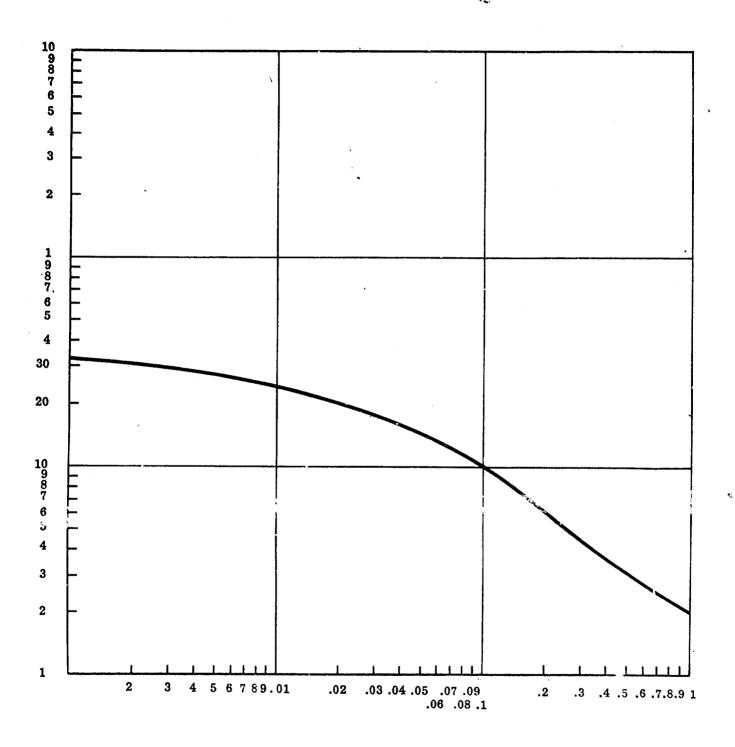

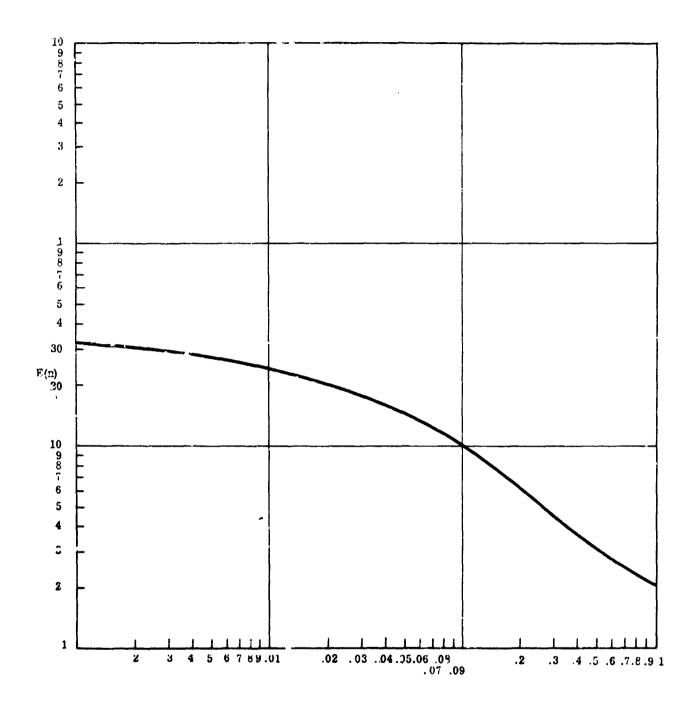

| 2-25 | Resolution Steps vs. Probability of ONE in Given<br>Position of S | 2-85    |

|------|-------------------------------------------------------------------|---------|

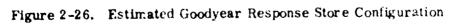

| 2-26 | Estimated Goodyear Response Store Configuration                   | 2-96    |

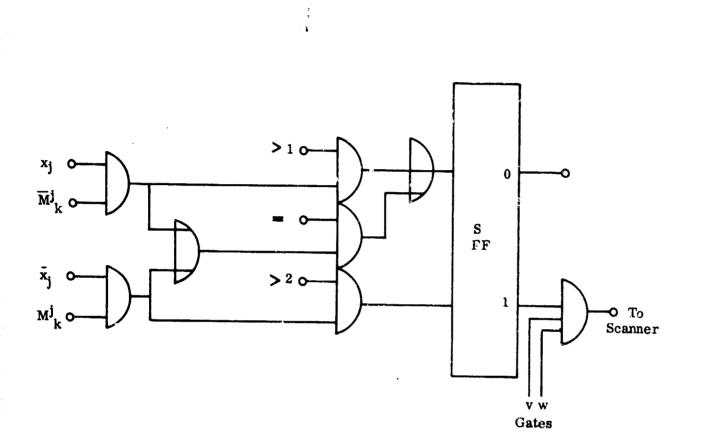

| 2-27 | A1 Response Store                                                 | 2-100   |

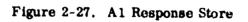

| 2-28 | A2 Response Store                                                 | 2-102   |

| 4-1  | File Organization for the Sea Surveillance Problem                | 4-11/12 |

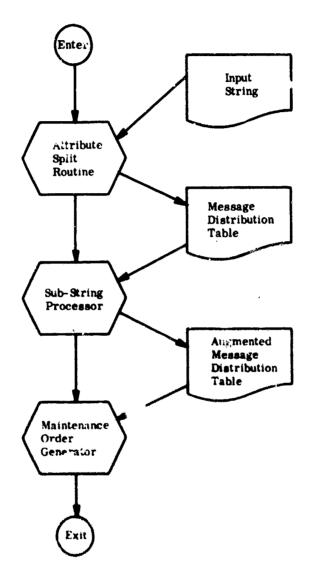

| 5-1  | Input Message Processor Organization                              | 5-5     |

| 5-2  | Example of Message Distribution Table                             | 5-8     |

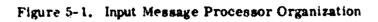

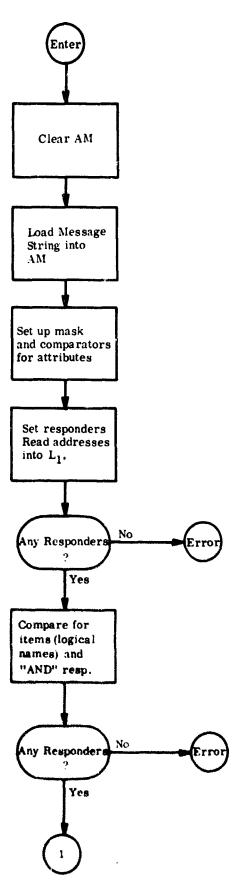

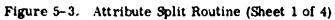

| 5-3  | Attribute Split Routine (4 sheets)                                | 5-11    |

| 5-4  | Sub-String Processor (4 sheets)                                   | 5-22    |

| 5-5  | Examples of Reduction of Input Messages to Maintenance Orders     | 5-27    |

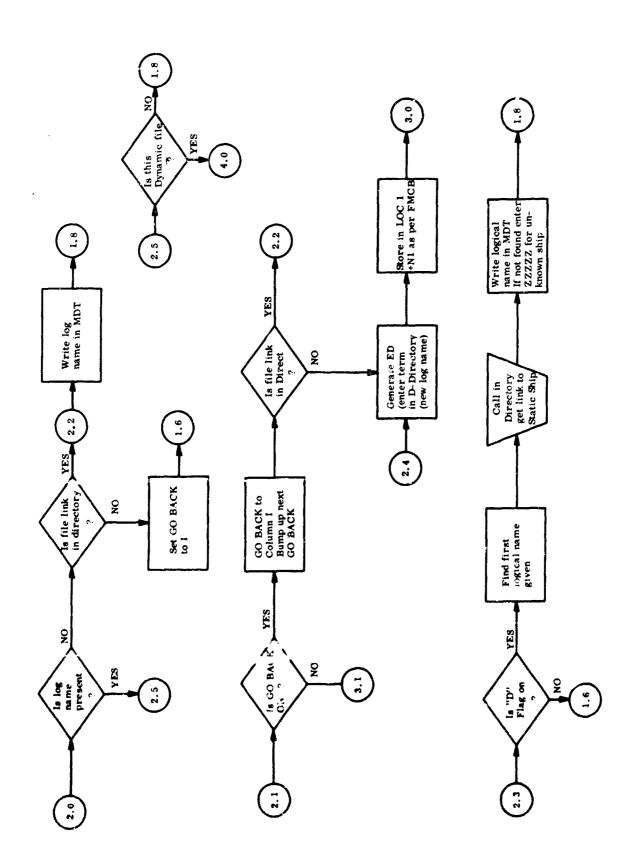

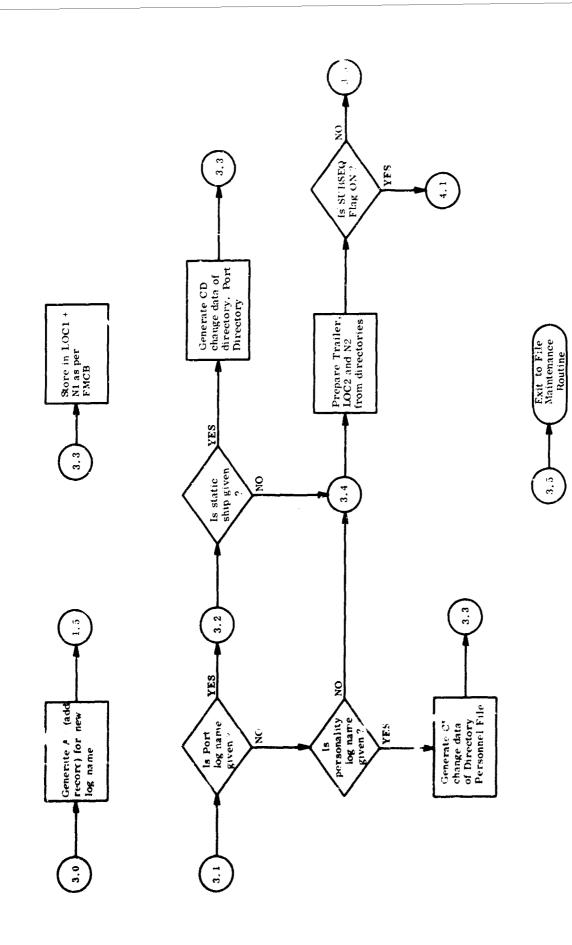

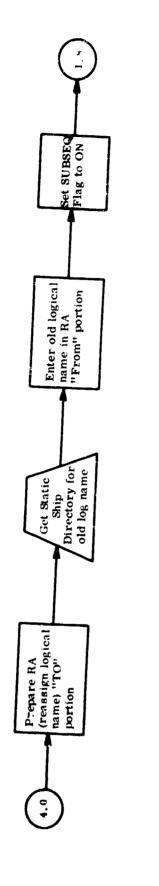

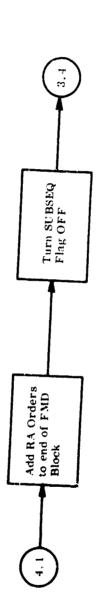

| 6-1  | File Maintenance Processing Flow (General)                        | 0-8     |

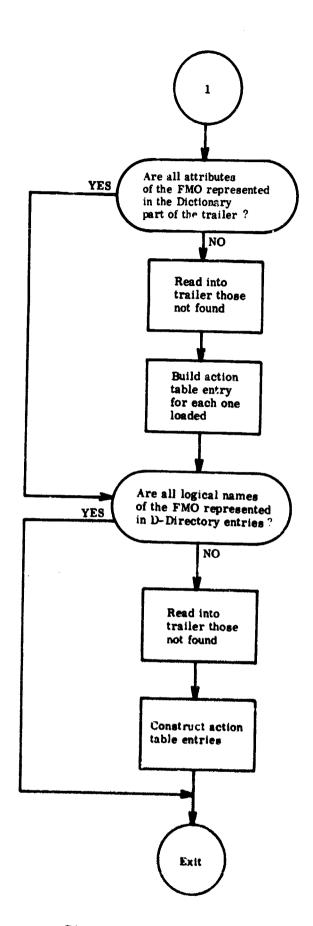

| 6-2  | Assembler (2 sheets)                                              | 6-14    |

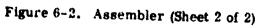

| 6-3  | Router                                                            | 6-16    |

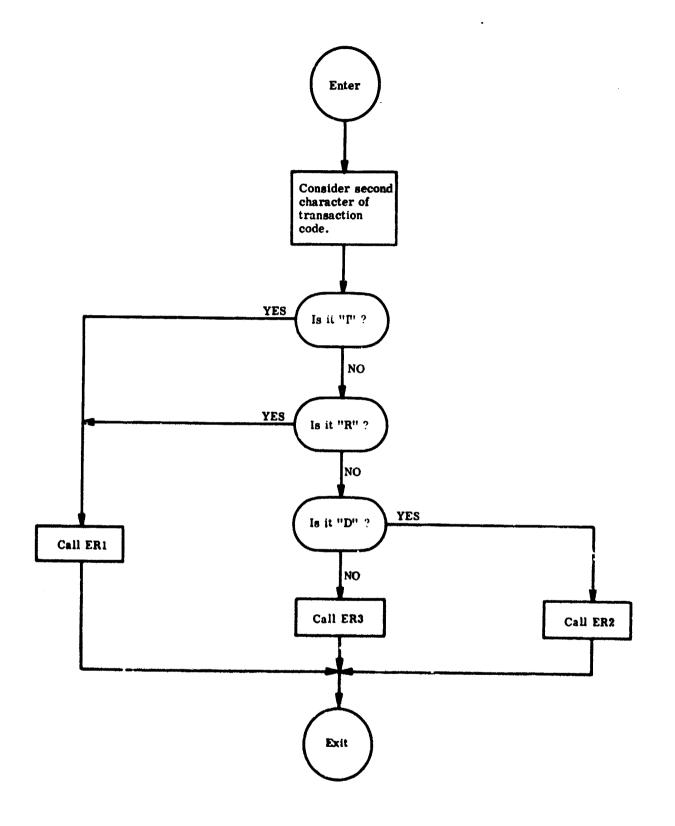

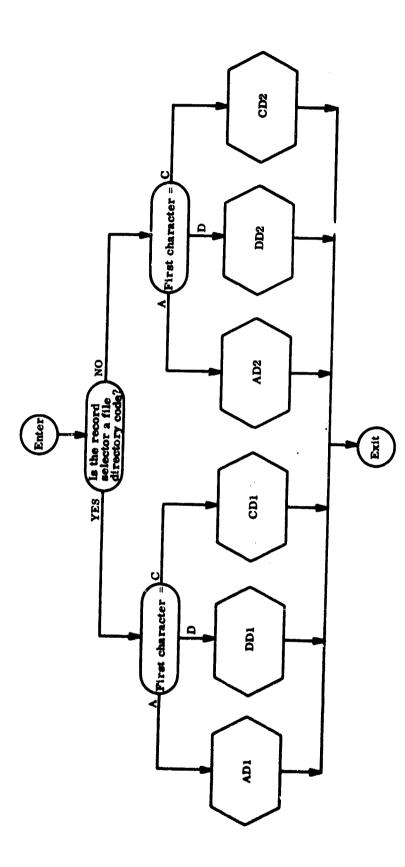

| 6-4  | ER1 Routine                                                       | 6-18    |

| 6-5  | ER2 Routine                                                       | 6-19    |

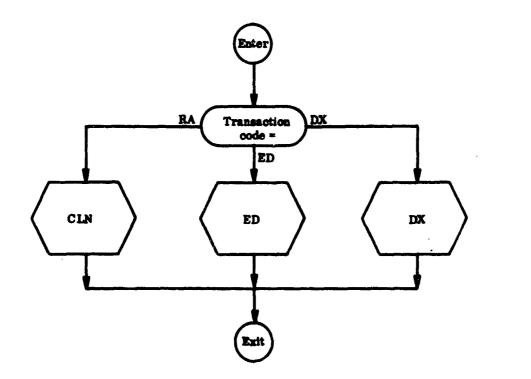

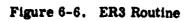

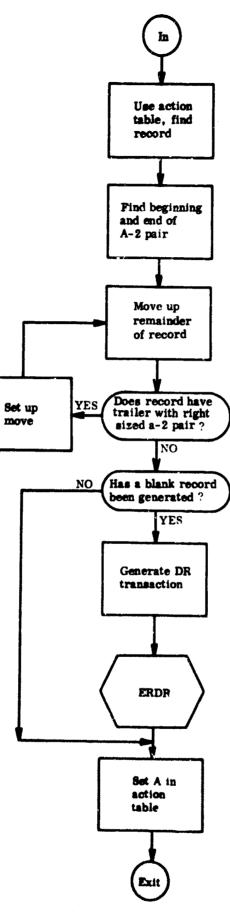

| 6-6  | ER3 Routine                                                       | 6-20    |

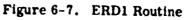

| 6-7  | ERD1 Routine                                                      | 6-23    |

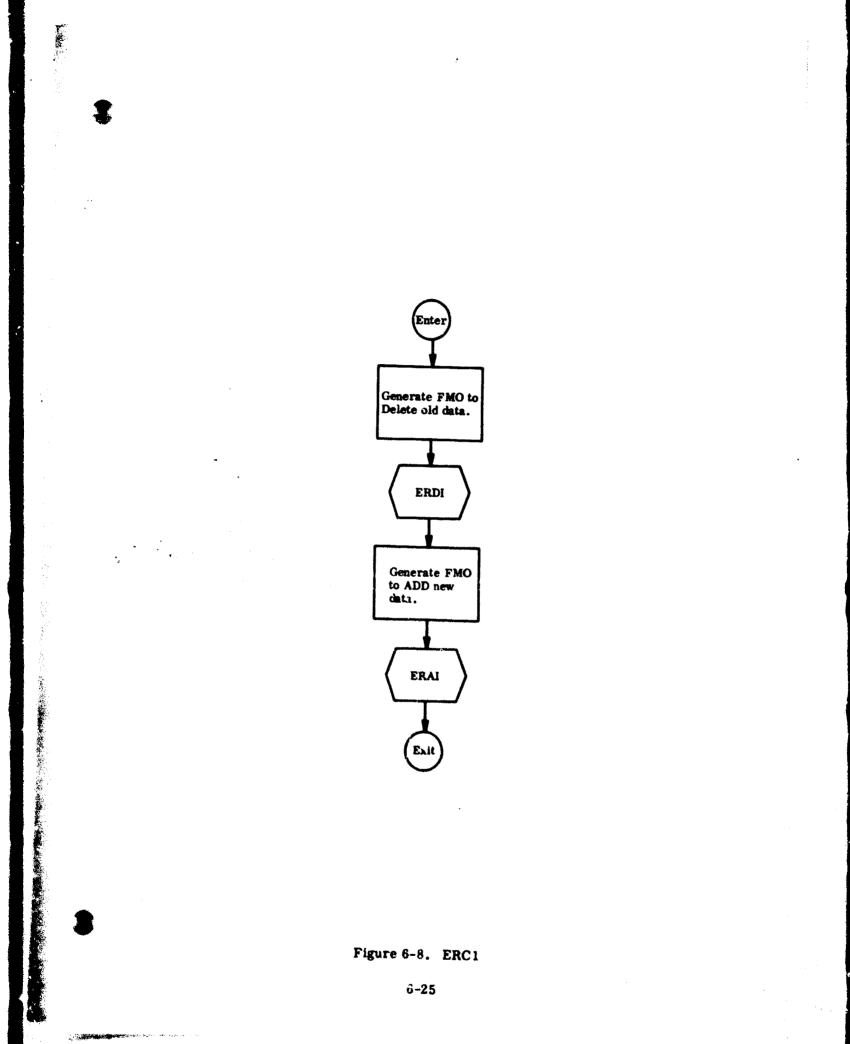

| 6-8  | ERC1                                                              | 6-25    |

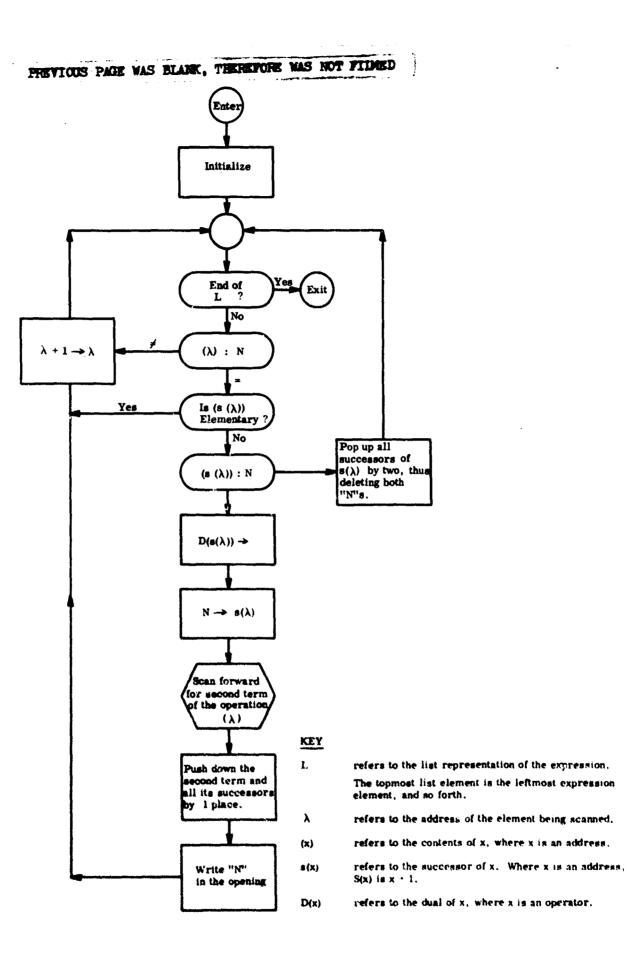

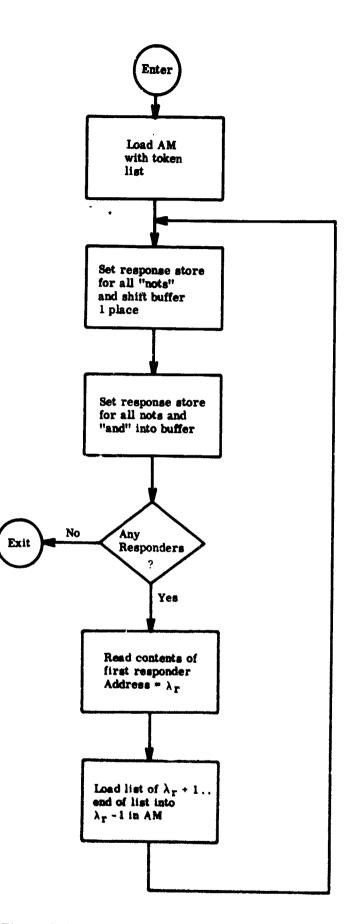

| 7-1  | Scan for Pushdown Point Flow Chart                                | 7-9/10  |

| 7-2  | Double Negation DN1 - AM Form                                     | 7-12    |

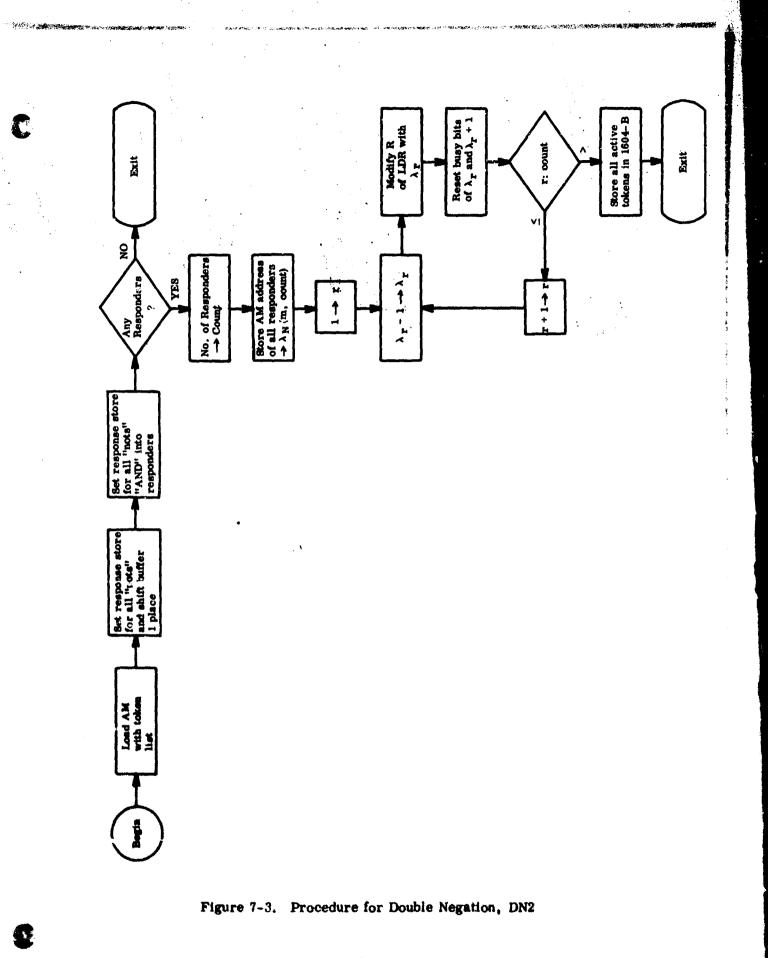

| 7-3  | Procedure for Wuble Negation, DN2                                 | 7-13    |

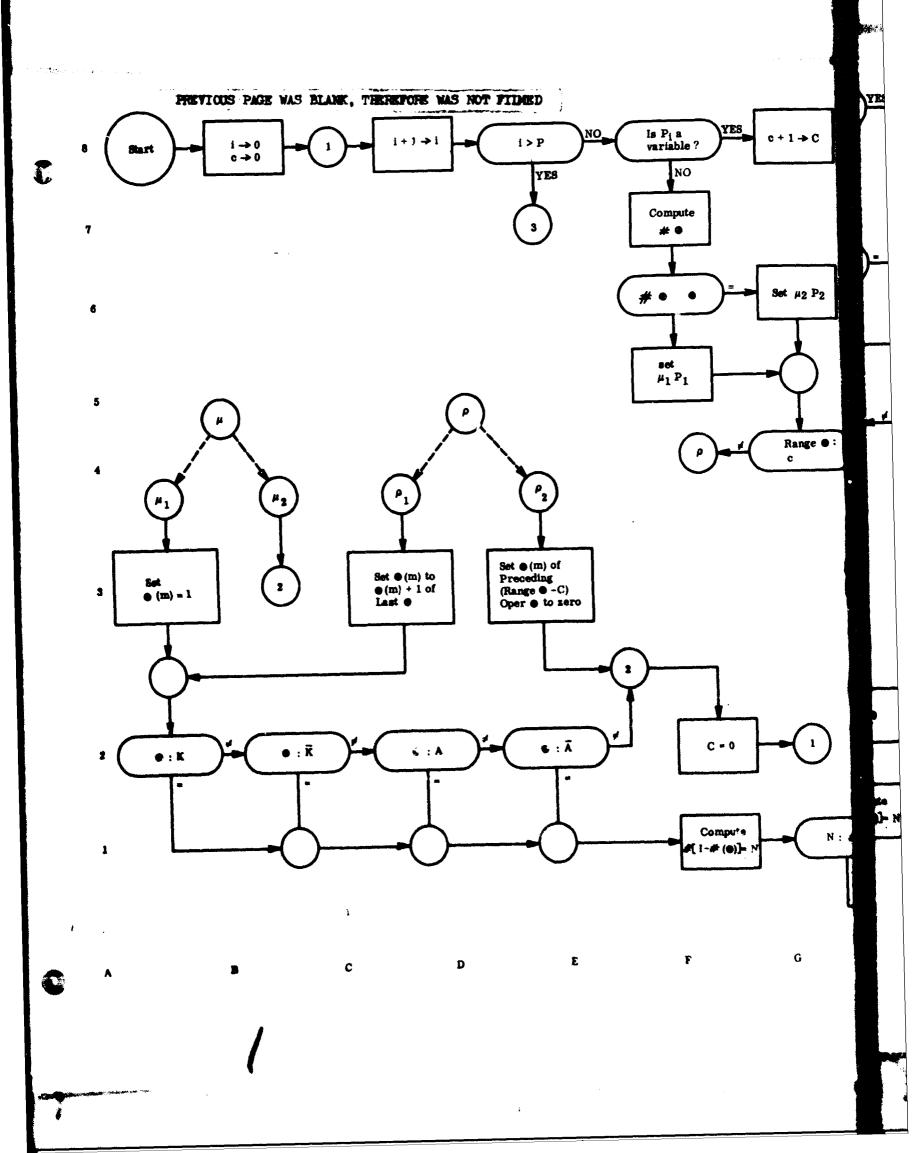

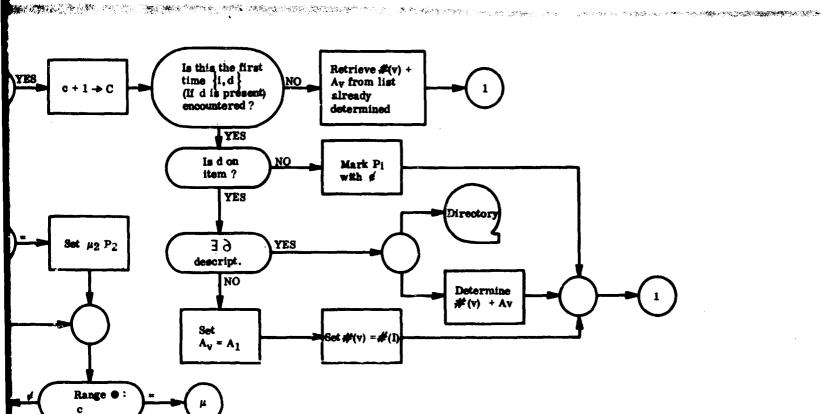

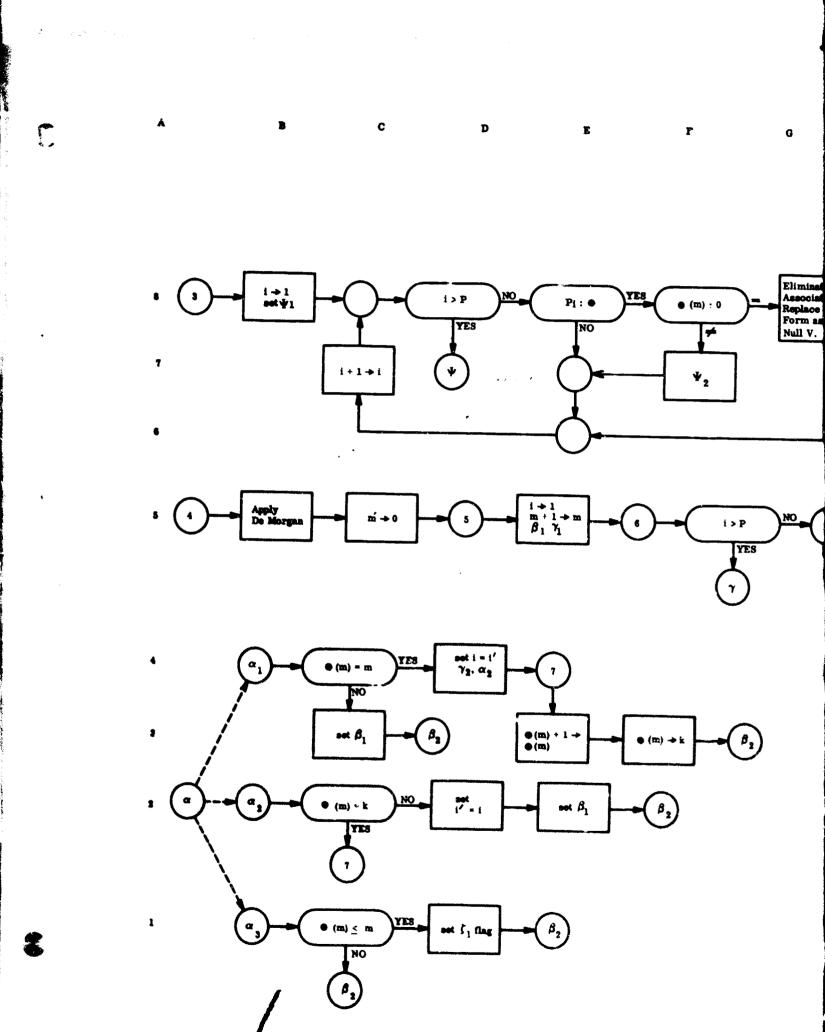

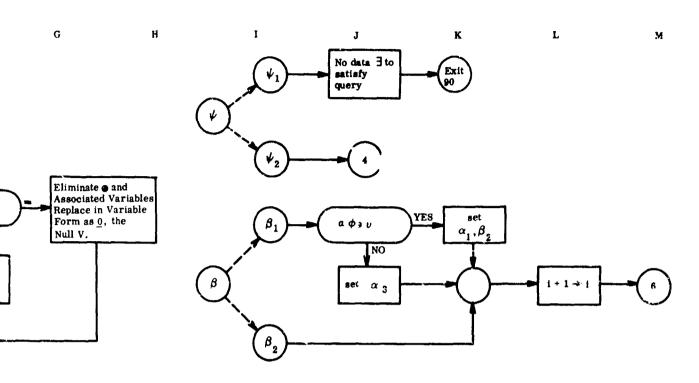

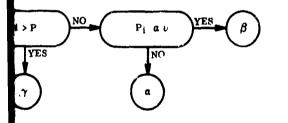

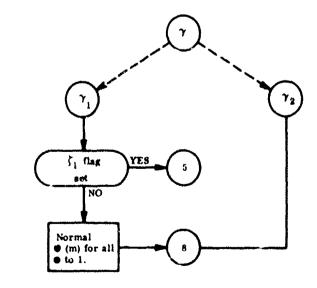

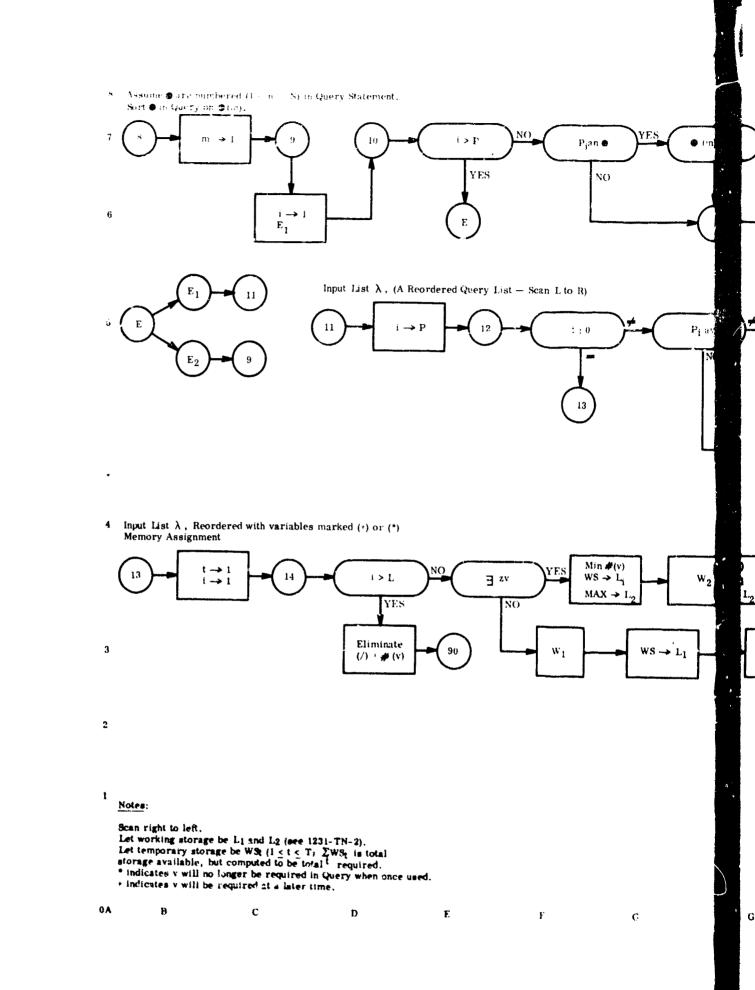

| 7-4  | Query Pre Arocessor (3 sheets)                                    | 7-29/30 |

| B-1  | Resolution Steps vs. Probability of ONE in Given<br>Position of S | B-4     |

## LIST OF TABLES, VOLUME II

| Table      |                                                     | Page   |

|------------|-----------------------------------------------------|--------|

| 2-1        | Comparison of Response Store Configurations         | 2-41   |

| 2-2        | AJ Instruction Set                                  | 2-44   |

| 2-3        | Functions for Logical Operations                    | 2-55 . |

| 2-4        | Instruction Fields                                  | 2-57   |

| 2-5        | Opcodes for 77 <sub>8</sub> Instructions            | 2-70   |

| 2-6        | Search Instructions                                 | 2-74   |

| 2-7        | Logic for Search Operations.                        | 2-74   |

| 2-8        | W-Field Control.                                    | 2-77   |

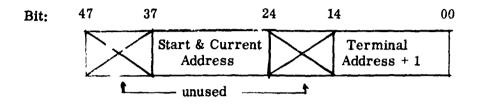

| 2-9        | BB Control                                          | 2-77   |

| 2-10       | GAP Instruction Times                               | 2-89   |

| 2-11       | A2 Timings                                          | 2-91   |

| 2-12       | A3 Instruction Timings                              | 2-92   |

| 2-13       | A3 Control Instruction Timing                       | 2-93   |

| 2-14       | Goodyear Response Store Estimate                    | 2-97   |

| 2-15       | Estimated Costs of Array and Associated Electronics | 2-98   |

| 2-16       | Cost Estimate for Registers and Other Circuits      | 2-98   |

| 2-17       | Estimated Costs for GAP                             | 2-99   |

| 2-18       | A1 Response Store Costs                             | 2-101  |

| 2-19       | Summary of A1 Costs                                 | 2-103  |

| 2-20       | Cost Comparison of AMs                              | 2-103  |

| 2-21       | Transfer Rate for 1604-B-A3 Move Instruction        | 2-105  |

| 2-22       | A Comparison of Configurations                      | 2-110  |

| <b>∛−1</b> | Attribute Identifier                                | 4-21   |

|            | Rules for Interpreting Record Selector              | 6-11   |

| 4          | Command List Representation                         | 7-67   |

| 7-2        | Subroutine Timing Comparison                        | 7-71   |

ix

## LIST OF TABLES, VOLUME II (Cont.)

| Table |                                                             | Page |

|-------|-------------------------------------------------------------|------|

| 7-3   | Timing of Representative Questions                          | 7-73 |

| 7-4   | 1604-B Frequency and Number of Instructions per Subroutines | 7-75 |

| 7-5   | GAP Frequency and Number of Instructions per Subroutine     | 7-76 |

X

#### EVALUATION

### I. Study Objective:

The objective of this work was to determine the value of state-of-the-art associative memories to more efficient execution of typical non-numeric and intelligence problems by the general purpose computer. Thus it was not the intent to provide an absolute figure of merit which would set the value of small associative memories. Nor was it the intent to evaluate the full range of memory logic design or nature of connection to the computer which an associative memory device may take. It was hoped however, that a useful reference point would be established with which to guide further studies. It should be noted that these studies are the first significant attempts to evaluate an associative memory in a system context; \* i.e., the associative memory is considered in association with a general purpose computer, typical peripheral hardware, and system programming.

#### II. Approach:

the second s

#### A. Selection of CDC 1604B and CDC 818 Disc

At the outset it was realized that the CDC 1604B computer, the CDC 818 disc and the Goodyear associative processor might not result in an optimum combination for the problems selected. Rather, the selection was based on the following:

1. The CDC 1604B is representative of "second generation" computers which are the most prominent in Air Force use today. Moreover, due to the high cost of replacing computer systems, it may be some time before present systems are replaced. Consequently, considerable savings might be realized from determining how these computers could be used more efficiently.

2. RADC recognized that there are several factors in addition to the choice of an associative memory and a general purpose computer which affect study results. These factors are associated with the software and with file structure, query statements, etc. thus by selecting the CDC 1604B and the CDC 818 disc, we provide the capability to modify the software and gain a more thorough understanding of the role of software in evaluating associative memories.

<sup>\*</sup>See Mr. Ronald Ferris' comments in Volume 11 of the International Federation for Information Processing 1965 proceedings under the panel session on Content Addressable Memories.

3. Since the hardware is available at RADC, the software programs developed can be implemented and exercised in order to provide empirical data with a minimum of cost and time.

÷.,

It should be emphasized that the selection of the CDC 1604B computer and CDC 818 disc does not affect the accuracy of the comparison made between the associative memory configuration and the non-associative memory configuration, since in both cases the same general purpose computer and disc were used. In fact, this is the type of data that is of interest to us.

B. Selection of Goodyear Associative Processor (GAP)

The primary intent of this effort was to evaluate the GAP merely as a first step in a long range plan to evaluate associative memories. Consequently, whether or not the GAP is optimally designed for a specific task is relatively unimportant. Instead it should be viewed as a research tool for use in obtaining valuable information pertaining to associative processing, particularly in the area of software. Accordingly the GAP design was selected with the intent to evaluate a state-of-the-art product with reasonable cost. Finally, it should be emphasized that evaluation of GAP cannot be construed as an evaluation of Goodyear Aerospace's capability to design computers.

C. Selection of Problems

The problems used throughout the study are actually processing functions. The intent was to choose a set of processing functions common to many specific problems and in so doing obtain generalizable results. Hence, the term sea surveillance merely indicates the source of the processing functions employed.

The selection of problems is a very important step and should not be taken lightly. The approach utilized in this study was briefly the following: \*

1. Identify a class of problems within the Air Force

2. Identify the processing functions within that class and select the most common.

3. Based on a set of criteria; i.e., priority, availability of data base, etc. a final set of processing functions were selected. The criteria used in this analysis is as follows:

<sup>\*</sup>This work was performed in-the-house at RADC. The details of this work are contained in a report located at RADC.

- a. Does the product satisfy an operational requirement?

- (1) Has a machine program been written to produce it?

- (2) How many producers use it?

- (3) Has the data base been built?

b. Are the program steps (operations, algorithm, etc.) common to other  $\operatorname{programs}$ ?

- c. is the program and data base description accessable?

- (1) Is it releasable to contractor (Security)?

- (2) How soon can it be delivered to contractor (where do we get it and must it be sanitized)?

d. Has program been written for 1604B class machine, i.e., is it one of these: 7090, 1410, 1218?

Measures

D. Evaluation Criteria and Measures

The following criteria and measures were developed by RADC, Auerbach Corporation and Goodyear Aerospace Corporation for use in their respective investigations:

#### Criteria

- A. Complexity of Programming Required

- B. Accuracy of Programming

- C. Complexity of Hardware Required (AM)

- 1. No. of Instructions in program.

- 2. Total time and cost of program.

- 3. Time and cost of producing general flow charts (problem analysis & definition).

語がうちょうませんない

10 **X**

1

- 4. Time and cost of detailed flow charts (required for time analysis).

- 1. No. of errors listed in (A3) and (A4) above.

- 2. Type of errors located in (A3) and (A4) above.

- 1. Type and number of components used in AM e.g.; 100 transistors.

- 2. Cost of AM and necessary interface.

- 3. Time and cost for each AM macroinstruction.

- 4. Time and cost for each basic AM instruction.

- 5. No. of AM searches required to complete each AM macro & basic instruction.

xiii

#### Criteria (Cont.)

- D. Reliability of Hardware

- E. System Efficiency

#### Measures (Cont.)

- 1. Reliability of each component multiplied by some factors, e.g., no. of components.

- 1. Time to execute program (machine run time).

- 2. Total cost of programming, hardware, and machine running time.

- 3. No. of AM & 1604B instructions used (and not used) and frequency of each.

- 4. Amount of data that is read into and out of AM and frequency of transfers.

- 5. Time AM is idle.

- 6. Time required for 1604B to set up AM processing (data transfers etc.).

- 7. Ratio of storage requirements vs availabilities.

- 8. Time 1604B is idle.

- 9. Time disc is idle. N/A

- 10. % of relative running & idle times for the 1604B, Disc, & AM.

Key

N/A - Not Applicable to Goodyear

III. Use of Study Results:

The results of this study provide a good reference point when determining the usefulness of proposed associative memories. It is believed that this type of investigation, i.e., within a system context is a most important and necessary step. It is our hope that workers in the associative memory field can use this and future studies as a yardstick in designing associative memory - general purpose computer configurations. RADC encourages a close examination of criterie and measures to be used in evaluation of associative memories. We also encourage those interested to examine this effort critically and would make welcome suggestions.

### SECTION I. INTRODUCTION

派室書

During the past few years a great deal of speculation has arisen concerning the effectiveness of associative memories, both large and small, within a computing system. The concept of an associative memory in which data is accessed by content rather than by its physical address has had considerable intuitive appeal for those interested in data manipulation rather than computational problems. 「「「「「「「「「」」」」」」

and have and have

のないないで

The technology associated with implementing such devices has made some progress. Several small associative memories have been implemented which contain approximately 2,048 words of memory and, depending upon the device, each word has 48 bits. Such memories have been constructed from so-called BILOC, BICORE, or similar devices. This technology is rather limited with respect to the core sizes that can be achieved at a reasonable cost. The technology associated with large memories is, on the other hand, being developed on the research level. Superconductive devices are being utilized in this technology.

Although considerable attention has been paid to the hardware aspects for both large and small associative memories (AM), several other aspects of importance have not received adequate attention. Thus, if one reviews the extensive literature as noted in the bibliography contained in Volume I of this report, very little may be found which describes the manner in which an AM can be integrated within a computer system, the programming tools that are required to take effective advantage of the memory, or the advantage or disadvantage of such memories in specific applications. Considering the early state of this growing technology, this is not surprising.

Rome Air Development Center (RADC) has developed a comprehensive plan to determine the advantages and disadvantages of both large and small associative memories. The work reported by the AUERBACH Corporation in these volumes is part of this comprehensive plan. Specifically, the study has focused attention upon small associative memories as typified by the Goodyear Associative Memory (a d scription of the Goodyear Associative Processor (GAP) is contained in Appendix A).

RADC has requested that the AUERBACH Corporation investigate a total data storage and retrieval system to determine the effectiveness of a s--called

hybrid associative computer system for such a problem, and to answer some of the following questions:

- (1) What is the most effective hybrid system?

- (2) How can an associative memory be integrated best into the computer system?

- (3) What are the costs associated with developing such devices?

- (4) What possible variants should be considered of the GAP technology which might enhance the AM or decrease the cost with little effect on the processing?

- (5) How effective are the variant systems?

- (6) Will any of the AMs affect the overall processing in the various systems enough to warrant its use.

- (7) Is a small associative memory effective?

- (8) What is the influence of an AM on flowcharting conventions and on programming?

Answers to most of these questions are found throughout this volume. Volume I, the management report, provides the answers and limitations upon the answers as well as references to Volume II in which the detailed support is provided for the general statements.

#### 1, 1 OVERALL SCOPE OF RADC ASSOCIATIVE MEMORY PROGRAM

The larger goal of the investigation is to aid RADC in the evaluation of the applicability and usefulness of a class of small associative memories available in the present state of the technology. This study is only one part of a larger and more comprehensive effort being directed by RADC, and while this investigation has a clearly defined and self-contained goal, the larger context must be considered. Insights and specific results and conclusions of this study are reported to RADC whether they are of primary importance to the fulfillment of the contract or a secondary result of the study.

Within the framework of the larger RADC effort, the overall goal of this investigation may be stated: Evaluate the applicability, effectiveness, and efficiency

of hybrid associative processors. The evaluation is to be performed by comparing associatively oriented systems against the best conventional systems employing otherwise comparable equipment. A sufficient range of hybrid organizations and depth of analysis is to be included to ensure a concrete and positive evaluation. The investigation is to consider both programming and equipment factors. \*

いるのであるとうです。

一方

Within this context, decisions have been made affecting the specific scope methodology, and its relationship to other research projects sponsored by RADC.

### 1,2 STUDY CONSIDERATIONS

State State

### 1.2.1 Approach Considerations

Several approaches can be taken in investigating the effectiveness of small associative memories. Each approach has certain advantages and disadvantages.

One approach widely used to evaluate alternative conventional equipment is to select several complicated problems and to code these problems in detail for the alternative configurations. Advantages to such an approach are:

- (1) A large number of manageable problems can be defined, detailed, and analyzed.

- (2) Alternative situations can be considered; e.g., alternative data structures, and record and file organizations may be considered.

- (3) Alternative problems Learing upon several subject areas could be considered, e.g., compiler developments, language developments, and data retrieval.

Disadvantages attendant with such an approach are:

- (1) The importance that one should attach to each individual problem is difficult to define since its frequency of use in a particular system may be difficult to assess.

- (2) Problems of importance to specific areas of interest on a particular problem may not have been covered.

A second approach is to select a single comprehensive problem, potentially rich in associative memory operations for study. This approach has several advantages:

- (1) A comprehensive <u>system</u> is viewed for all data processing functions so that the frequency of operations is known and no processes are overlooked.

- (2) Areas which may not have been selected for associative memory operations may be uncovered by being forced to review all processes.

- (3) Assumptions as to the location of data which may tend to bias a solution towards the associative memory is avoided since one must take cognizance of the precise location of data as developed in previous processing steps.

- (4) The associative memory can be utilized to store more than one class of data as required by dynamic system processing.

As with the previous approach, there are certain inherent disadvantages. Some of these are:

- (1) The solution reached for a particular problem may be specific and may preclude generalization to other problems.

- (2) The specific problem may be such that the full extent of the AM is not utilized.

- (3) Alternative solutions might not be evaluated sufficiently since sufficient time for each alternative might not be possible.

- (4) Excessive time might be spent in systems design of the problem taking time away from study of the details of associative memory processing.

Realizing the advantages and disadvantages attendant with each approach, RADC selected the latter for the AUERBACH Corporation and the former for other contractors. The study realized all of the advantages in this approach. By being forced to think at both a systems and a detailed level, many observations concerning associative memory processing were developed. At the same time, several of the above disadvantages are pertinent. The solution reached is believed to be sufficiently general and applicable to problems of the same class. However, the queries and maintenance operations

specified as "typical" in the sea surveillance problem did not sufficiently exercise the AMs studied. That is, the queries were very simple and did not require much processing while the data resided in the associative memory. More complex questions could have shown the AM to greater advantage. Alternative solutions (e.g., different file structures) could not be studied. Thus, perhaps a more clever file structure than that utilized in this study could have been devised which would have shown the AMs to greater advantage. The authors cannot assess this since sufficient time did not exist for exploring this possibility. They can verify that some time was spent in systems design which could have been spent more profitably on the details of AM programming. In spite of this, much was learned about the organization of a system around an AM, the effect of an AM upon system organization, and flowcharting. Ř

and a water

20

10.00

The study team believes that, in the main, the advantages of the approach outweighed the disadvantages. A large amount of information of considerable interest and importance to associative memory technology has been developed and is reported in these volumes.

1.2.1.1 <u>Hardware Approach</u>. As representative of the current technology of small associative memories, the Goodyear Associative Processor was selected for study.

In addition to studying the Goodyear Associative Processor in detail, both from the hardware and software viewpoints, several variant AMs based upon the Goodyear technology were to be studied. There were several AM variations that were of particular interest to the study.

- (1) Logical Organization of the AM: The range of variation desired was to investigate a minimal control unit requiring detailed control by instruction from the 1604-B and one which was independent of the 1604-B.

- (2) Interface with the 1604-B. The variations to be considered ranged from one which required no modificato the 1604-B to one which would have a special channel and special register to one fully integrated with the 1604-B.

- (3) Instruction Set. The variations would be from a minimal set which would decrease costs of the AM to one in which extensive search capabilities generalizing the GAP would be developed.

The selection of the specific memories studied were developed after extensive meetings between the programmers and the hardware designers. The details concerning the specific memories chosen are presented in Section II of this report.

1.2.1.2 <u>Cost Analysis</u>. Costing played a major role in the selection of the specific variants that were to be exercised in the study. To determine the costs involved, the approach utilized was to study GAP thoroughly, develop logic diagrams, and estimate the amount of equipment that would be required. AUERBACH's knowledge of the state of the art of integrated circuit technology and BILOC devices was utilized. The approach was to develop cost factors to permit other hardware variations to be costed. Wherever the cost analysis was to show a minor increase in cost to implement a particular capability desired by a programmer, the feature was added. Cost analysis information is provided in Section II.

1.2.1.3 <u>Programming</u>. The problem to be programmed was to be effected in a general manner. The nature of intelligence problems is such that if a system were based upon the specific requirements, other requirements would arise requiring further programming. The approach was, therefore, to permit arbitrary logical conditions to be specified to the resulting system. This approach avoids biasing programs to handle very specific tasks, which potentially have little utility thereafter.

In addition to considering the Goodycar Associative Processor and the variant associative memories, a non-associative memory configuration consisting of the system without an AM was to be evaluated.

To develop a unified approach for the sea surveillance problem for all configurations was a challenge. It is believed that the approach taken achieved a unified approach. The file structure developed is appropriate for all systems, although it is biased for associated memory processing. To show the variation in AM and non-AM, maching code was developed for the GAP and the non-AM solution. Coding for the variant AMs was not performed explicitly. In one instance the instruction complement of the AM was such that GAP coding was a subset of the AM and its effect could be estimated; in a second instance, the GAP was simulated and the variation in time noted.

#### 1.3 PROBLEM SELECTION

The specific problem utilized in the study was selected by RADC. It was recognized that the study results would depend upon the potential that such memories

have to aid the problem selected. The general area of the problem was to be data storage and retrieval of formatted files relevant to the intelligence community. The selection criteria utilized to choose the data base and problem were: