# UNCLASSIFIED AD 431205

# DEFENSE DOCUMENTATION CENTER

**FOR**

SCIENTIFIC AND TECHNICAL INFORMATION

CAMERON STATION, ALEXANDRIA, VIRGINIA

UNCLASSIFIED

NOTICE: When government or other drawings, specifications or other data are used for any purpose other than in connection with a definitely related government procurement operation, the U. S. Government thereby incurs no responsibility, nor any obligation whatsoever; and the fact that the Government may have formulated, furnished, or in any way supplied the said drawings, specifications, or other data is not to be regarded by implication or otherwise as in any manner licensing the holder or any other person or corporation, or conveying any rights or permission to manufacture, use or sell any patented invention that may in any way be related thereto.

X

AMRL-TDR-63-133

# CATALOGED BY DUC. AS AD NO.

# THE UDOFT FLIGHT SIMULATION SYSTEM

TECHNICAL DOCUMENTARY REPORT No. AMRL-TDR-63-133

DECEMBER 1963

BEHAVIORAL SCIENCES LABORATORY

6570th AEROSPACE MEDICAL RESEARCH LABORATORIES

AEROSPACE MEDICAL DIVISION

AIR FORCE SYSTEMS COMMAND

WRIGHT-PATTERSON AIR FORCE BASE, OHIO

Contract Monitor: William B. Goeckler Project No. 6114, Task No. 611413

(Prepared under Contract No. AF 33(657)-7065 by Sylvania Electric Products, Inc., Needham, Massachusetts)

### NOTICES

When US Government drawings, specifications, or other data are used for any purpose other than a definitely related government procurement operation, the government thereby incurs no responsibility nor any obligation whatsoever; and the fact that the government may have formulated, furnished, or in any way supplied the said drawings, specifications, or other data is not to be regarded by implication or otherwise, as in any manner licensing the holder or any other person or corporation, or conveying any rights or permission to manufacture, use, or sell any patented invention that may in any way be related thereto.

Qualified requesters may obtain copies from the Defense Documentation Center (DDC), Cameron Station, Alexandria, Virginia. Orders will be expedited if placed through the librarian or other person designated to request documents from DDC formerly ASTIA).

Do not return this copy. Retain or destroy.

Stock quantities available at Office of Technical Services, Department of Commerce, Washington 25, D. C. Price per copy is \$4.00.

### Change of Address

Organizations receiving reports via the 6570th Aerospace Medical Research Laboratories automatic mailing lists should submit the addressograph plate stamp on the report envelope or refer to the code number when corresponding about change of address.

700 - February 1964 - 162-27-515

### **FOREWORD**

This report contains a review of the UDOFT program from June 1956 to December 1962. This period of approximately six and one-half years comprises system development (June 1956 to April 1960), installation (April 1960 to September 1960) and operation (September 1960 to December 1962). The work was sponsored jointly by the U.S. Air Force and the U.S. Navy under Contracts N61339-40, N61339-853 and N61339-1150. This summary report has been prepared for the Behavioral Sciences Laboratory of the Aerospace Medical Division, Wright-Patterson Air Force Base, by the Electronics Systems Division of Sylvania Electric Products, Inc., Needham, Massachusetts, under Air Force Contract No. AF33(657)-7605 and is in support of Project 6114, "Simulator Techniques for Aerospace Crew Training" and Task No. 611413, "Digital Computers." Mr. William B. Goeckler, Simulation Techniques Branch, Training Research Division, Behavioral Sciences Laboratory, 6570th Aerospace Medical Research Laboratories, served as contract monitor.

Mr. Julian Wargo, Manager of Sylvania's Digital Simulation Systems Department, was principal investigator and directed the preparation of this report. Other key Sylvania personnel who contributed include F. Kearney, K. Rago, and H. Wychorski of the Computer Laboratory; Mrs. F. MacNair and J. Prutsalis of the Programming and Analysis Laboratory, and D. Rush of the Product Support Organization.

### ABSTRACT

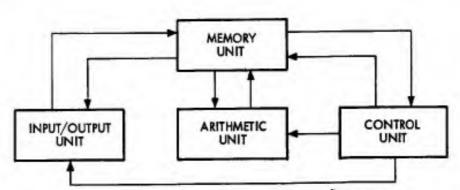

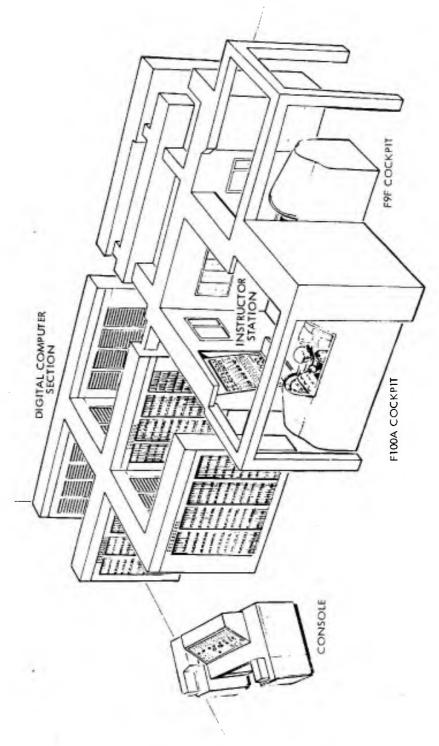

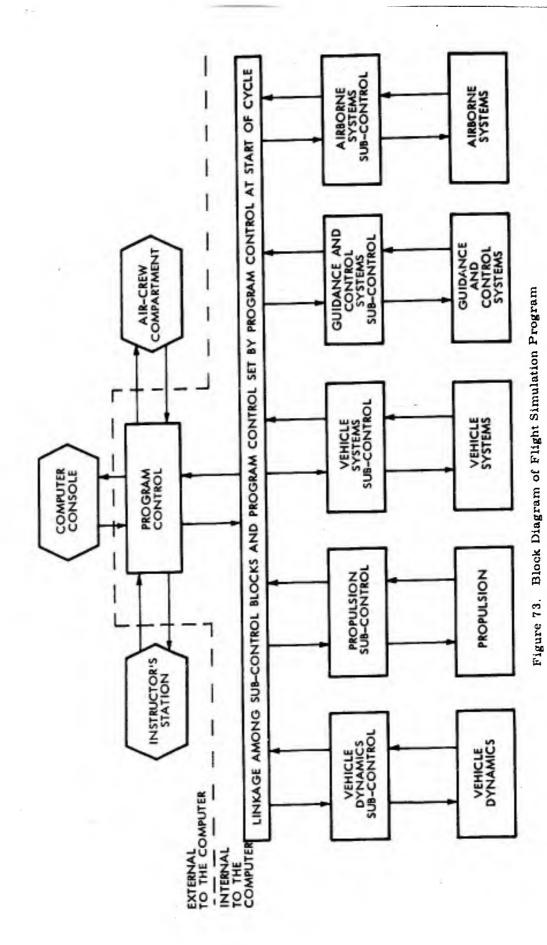

UDOFT (Universal Digital Operational Flight Trainer) represents the first full-scale application of a high-speed, general-purpose digital computer to the real-time flight simulation problem. Through the use of the stored program digital computer, simulation of different aircraft is accomplished by changing the computer program. This flexibility is the key to the realization of the full advantages of the digital control system, as compared to the conventional analog control system, in this application. Basically a high-speed, general-purpose digital computer, the UDOFT computer represents an advancement in the design of real-time control computers. With the use of dual, 4096-word, random-access, magnetic core memories, the basic instruction time for the UDOFT computer is five microseconds. To interface with the analog environment of a flight compartment, the UDOFT computer is equipped with a special-purpose, real-time input-output capability.

Use of the computer in a simulation system demanded the preparation of programs for applying the computer to the solution of the mathematical model of the real-world system under consideration. Such programs were written for the F-100A and the F9F-2. Extensive qualification testing was performed to ensure proper and complete simulation of these aircraft.

### PUBLICATION REVIEW

This technical documentary report is approved.

Walter F. Krether Walter F. GRETHER

Technical Director

Behavioral Sciences Laboratory

### TABLE OF CONTENTS

|           |                                                     | Page     |

|-----------|-----------------------------------------------------|----------|

| SECTION I | I: INTRODUCTION                                     | . 1      |

| 1. 1      | Purpose                                             |          |

| 1. 2      | Background Information                              | . 1      |

| 1. 3      | Program History                                     |          |

| 1.4       | General Program Requirements                        | . 3      |

| 1.5       | Organization of this Report                         | . 4      |

| SECTION I | T. GIAGORIA DEGGORIOGIA                             |          |

| SECTION I |                                                     |          |

| 2. 1      | Introduction to Basic Digital Computers             |          |

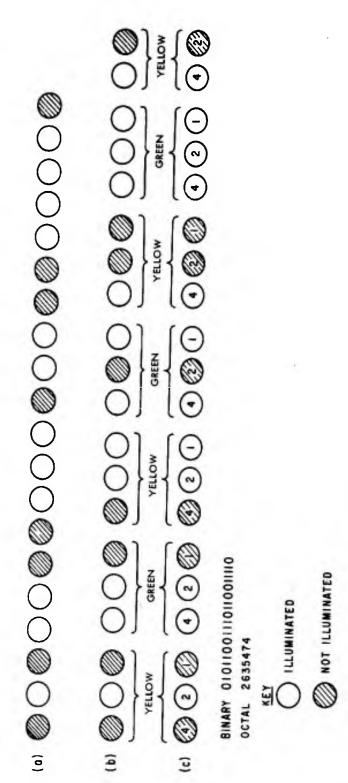

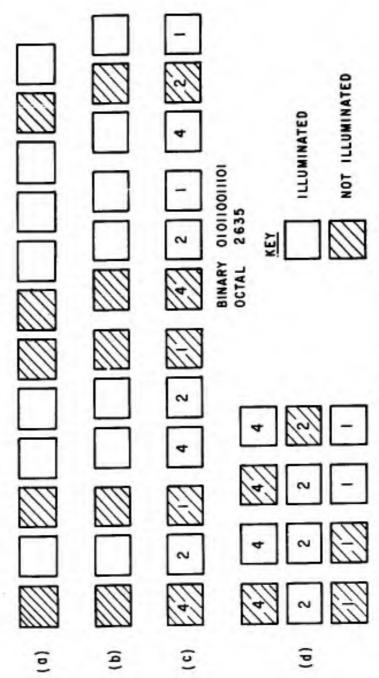

|           | 2.1.1 Numbering System                              | . 5      |

|           |                                                     |          |

|           |                                                     |          |

| 2, 2      |                                                     | . 8      |

| 4. 2      | Introduction to UDOFT                               | . 8      |

|           | 2. 2. 1 UDOFT Computer Operation—Simplified         | 12       |

|           | ·                                                   |          |

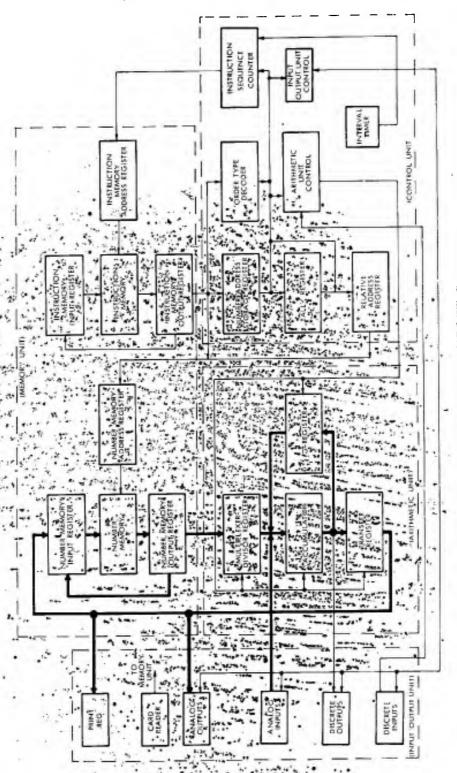

| SECTION I | III: UDOFT COMPUTER DESCRIPTION                     | . 16     |

| 3. 1      | Introduction                                        | . 16     |

| 3. 2      | Word Format                                         |          |

| 3. 3      | Instruction Repertoire                              | . 18     |

|           | 3. 3. 1 Arithmetic Instructions                     | . 18     |

|           | 3.3.2 Clerical Instructions                         | . 18     |

|           | 3. 3. 3 Control Instructions                        | . 19     |

|           | 3. 3. 4 Input-Output Instructions                   | . 21     |

|           | 3. 3. 5 Special Purpose Instructions                | . 23     |

|           | 3. 3. 6 UDOFT Registers and Symbolic Description of |          |

|           | UDOFT Instructions                                  | 23       |

|           | 3. 3. 7 Address Modification (Relative Addressing)  |          |

| 3, 4      | Main Frame                                          |          |

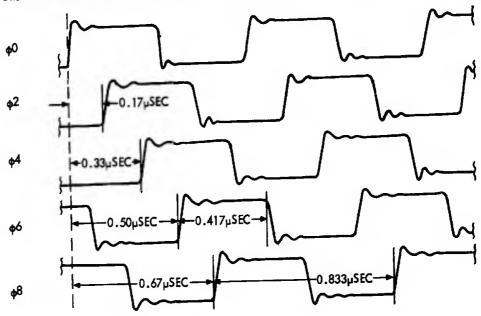

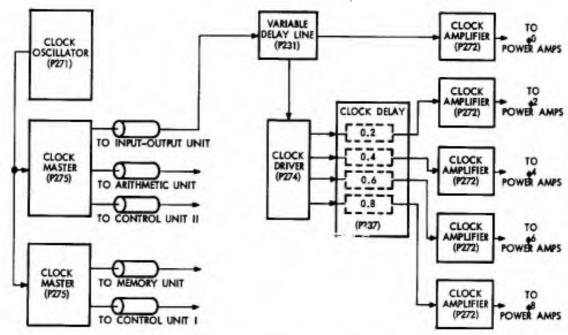

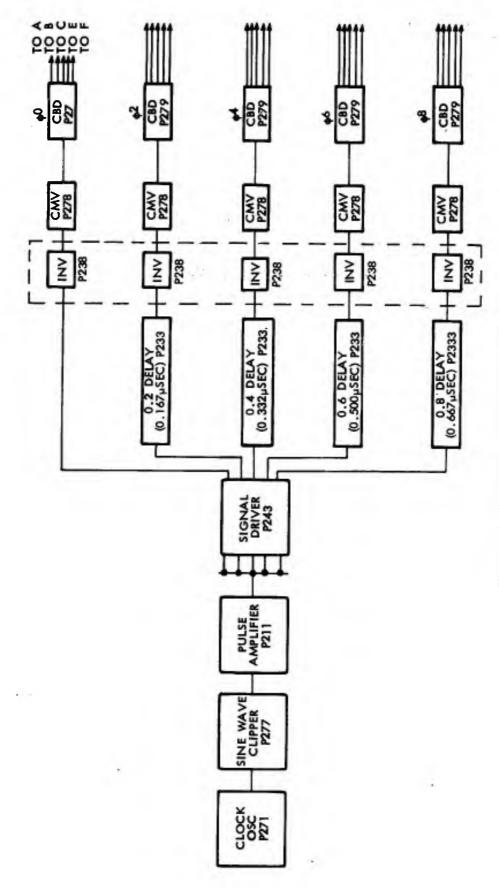

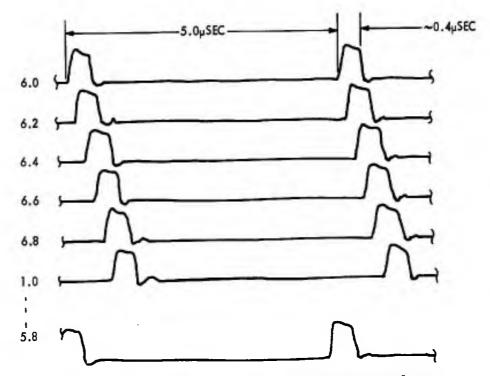

|           | 3. 4. 1 Master Timing System                        |          |

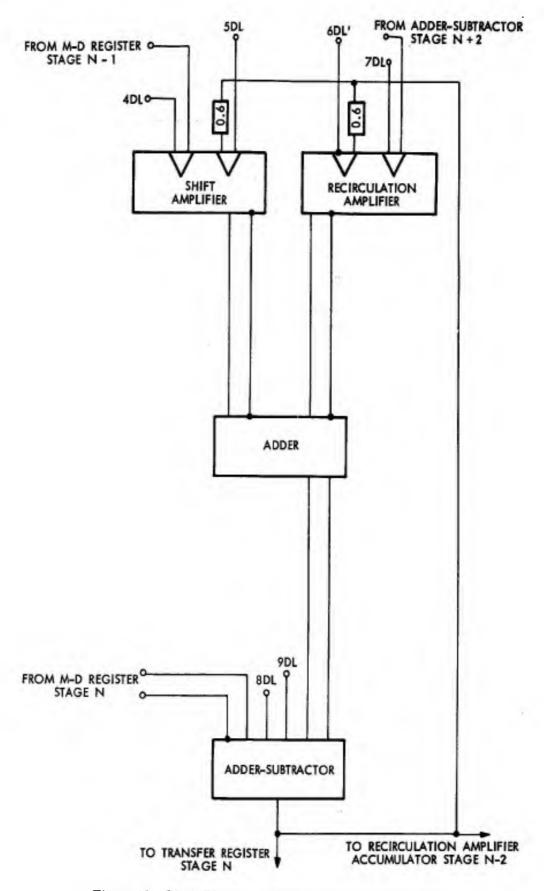

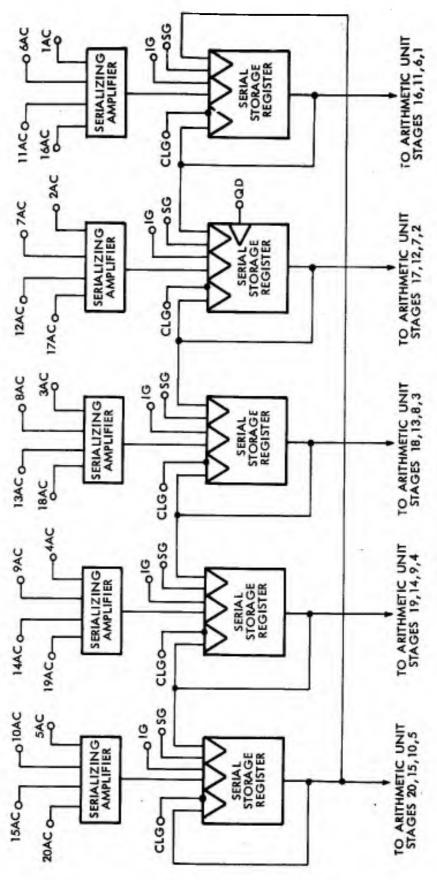

|           | 3. 4. 2 Arithmetic Unit                             |          |

|           | 3. 4. 3 Control Unit I                              |          |

|           | 3. 4. 4 Control Unit II                             | 43       |

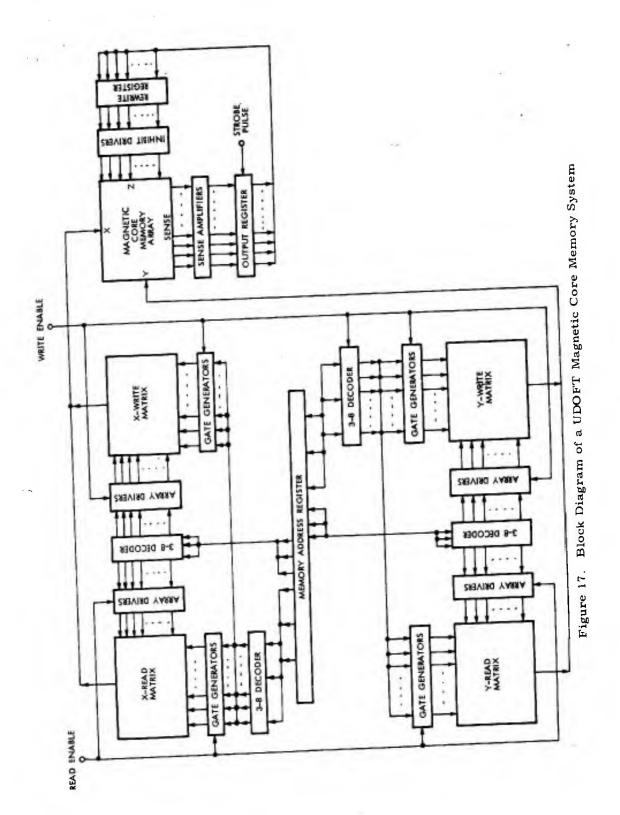

| 3, 5      | Memory Unit                                         | 45       |

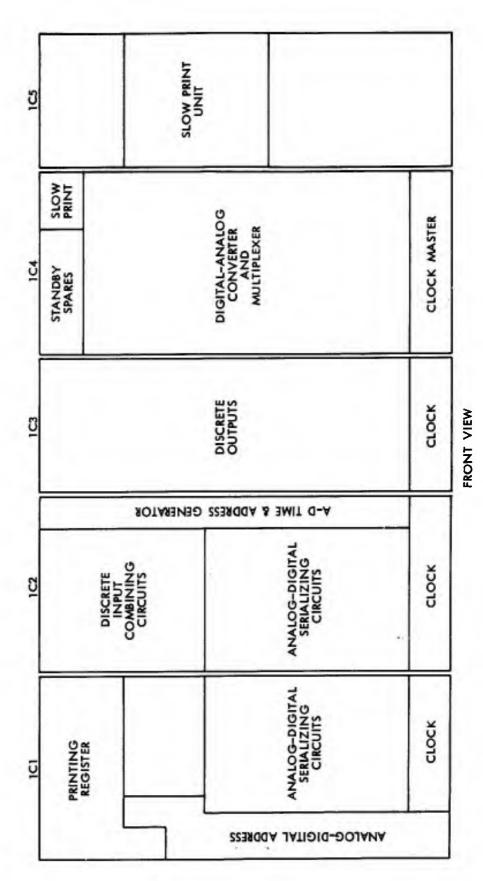

| 3.6       | Input-Output Unit                                   | 47       |

|           | 3.6.1 Discrete Inputs                               |          |

|           | 3. 6. 2 Discrete Outputs                            |          |

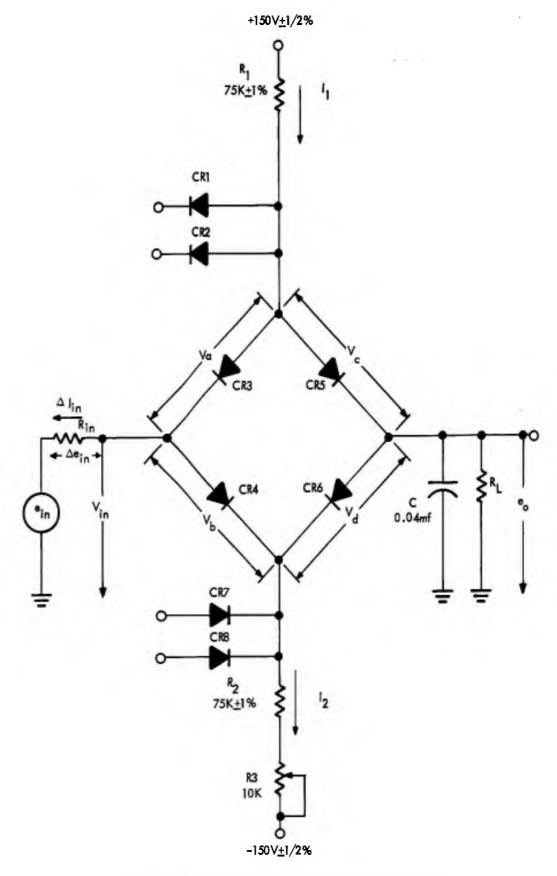

|           | 3. 6. 3 Analog Inputs                               |          |

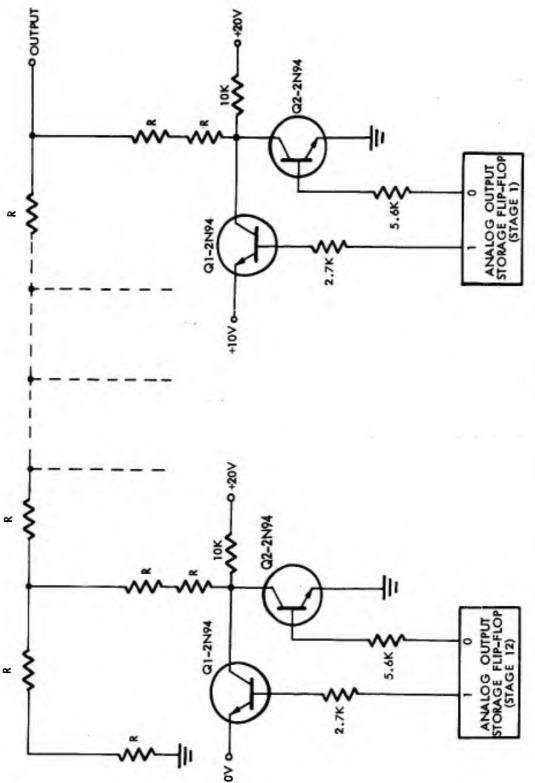

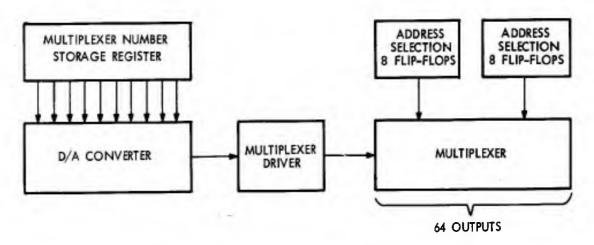

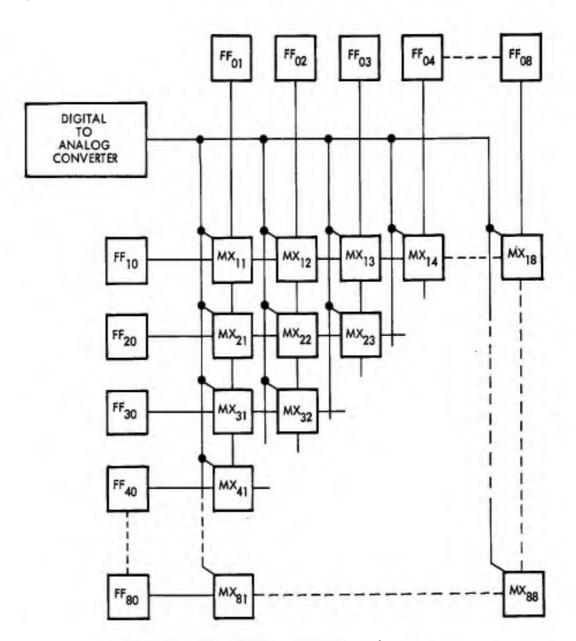

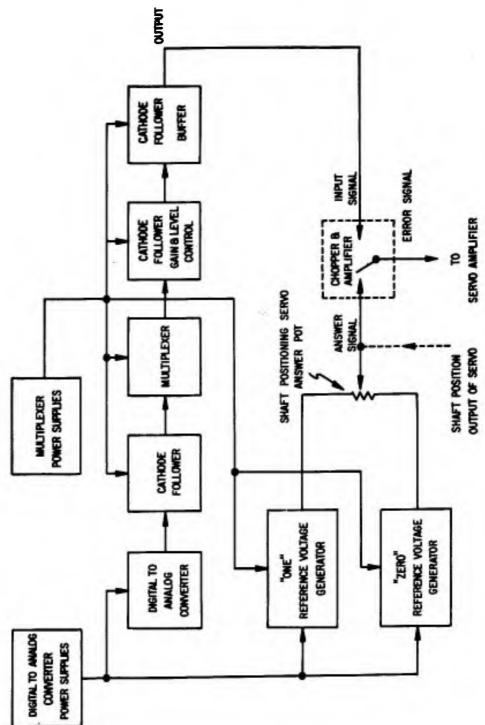

|           | 3. 6. 4 Analog Outputs                              |          |

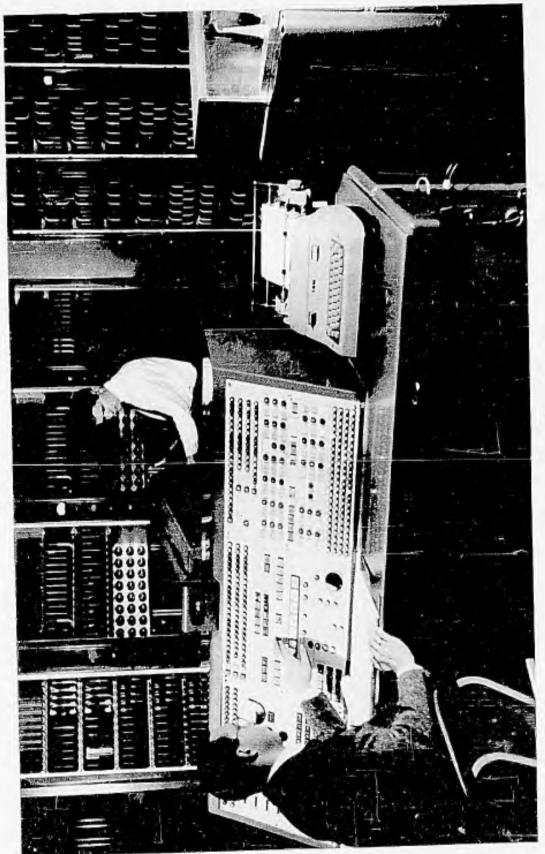

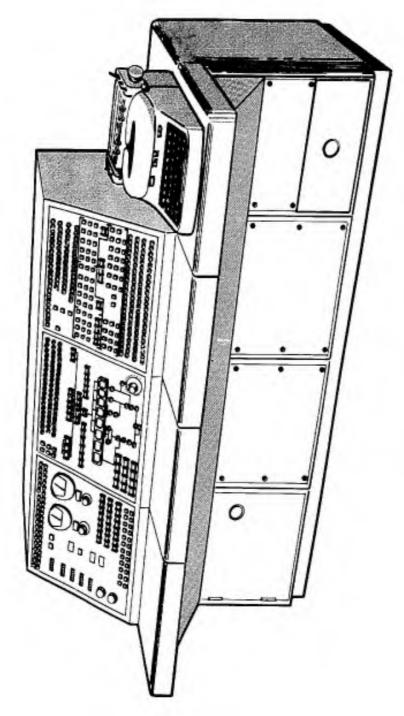

| 3, 7      | Computer Console Unit                               | 52       |

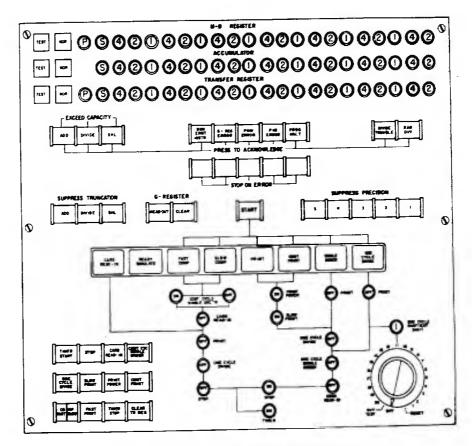

|           | 3. 7. 1 Console Panel A                             | 52       |

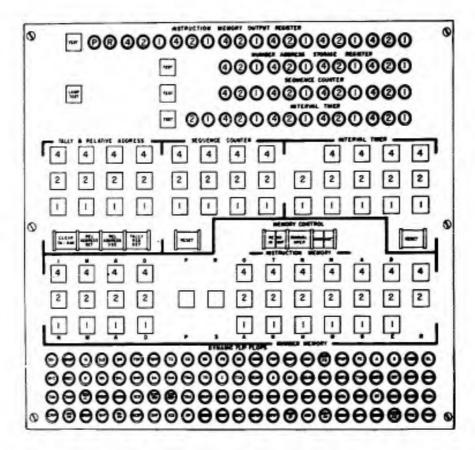

|           | 3. 7. 2 Console Panel B                             | 58       |

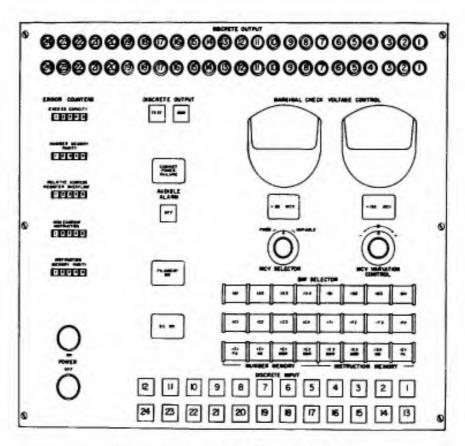

|           | 3.7.3 Console Panel C                               |          |

|           | 3.7.4 Input Card Reader                             | 63       |

|           | 3.7.5 Output Printer                                | 63       |

| SECTION I | V: COMPUTER HARDWARE DEVELOPMENT HISTORY            | 65       |

| 4. 1      | Introduction                                        |          |

| 4. 2      | Logic Design Problems                               | 65       |

| 7. 4      | 4. 2. 1 Number Memory                               | 05       |

|           | 4. 2. 2 Parity Formation—Card Reader Input          | 65       |

|           |                                                     |          |

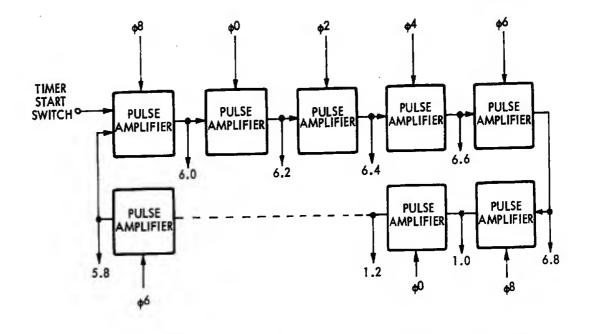

|           | 4. 2. 3 Interval Timer                              | 66       |

|           |                                                     |          |

|           |                                                     | 67       |

|           |                                                     | 67       |

| 4 9       | 4. 2. 7 Non-Existent Instruction                    |          |

| 4. 3      |                                                     |          |

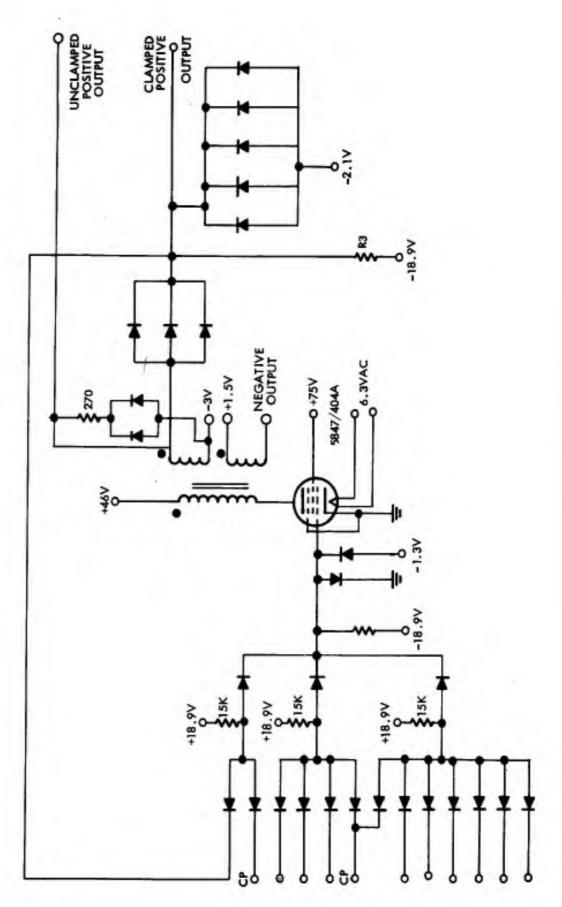

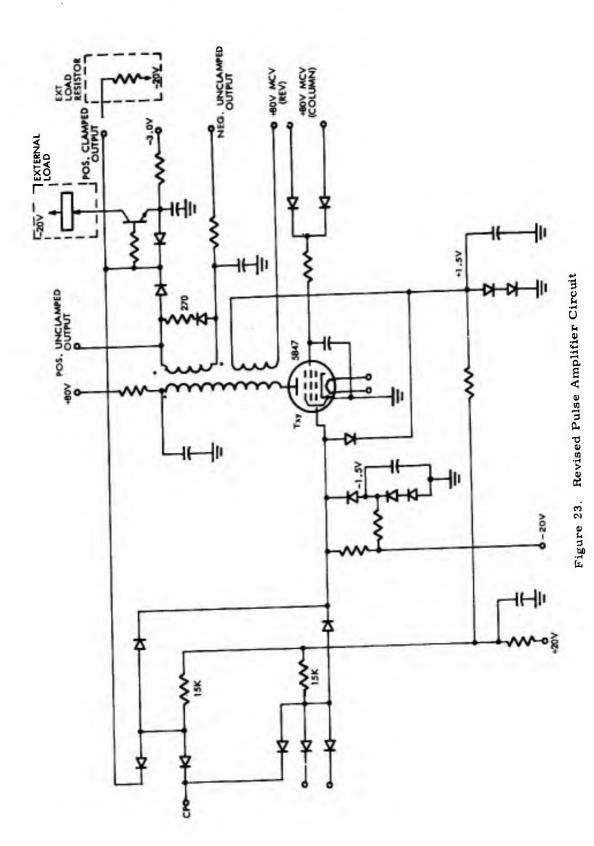

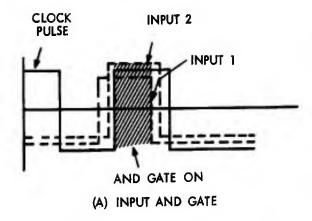

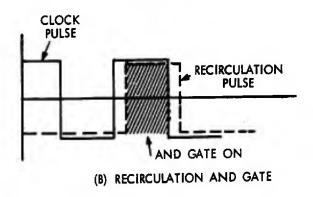

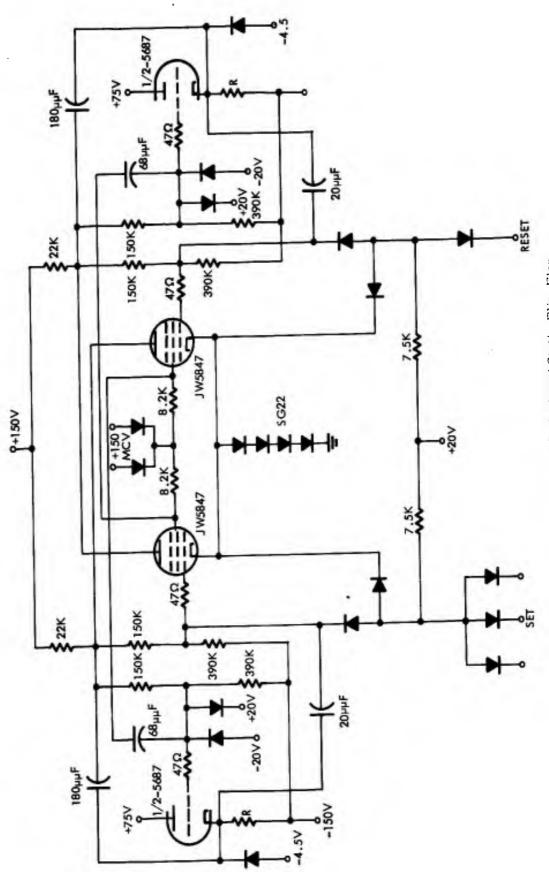

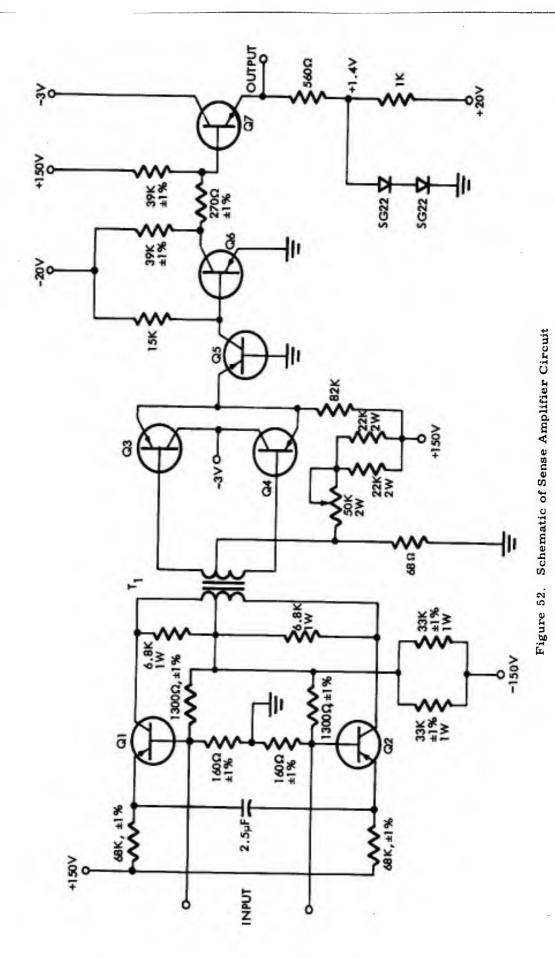

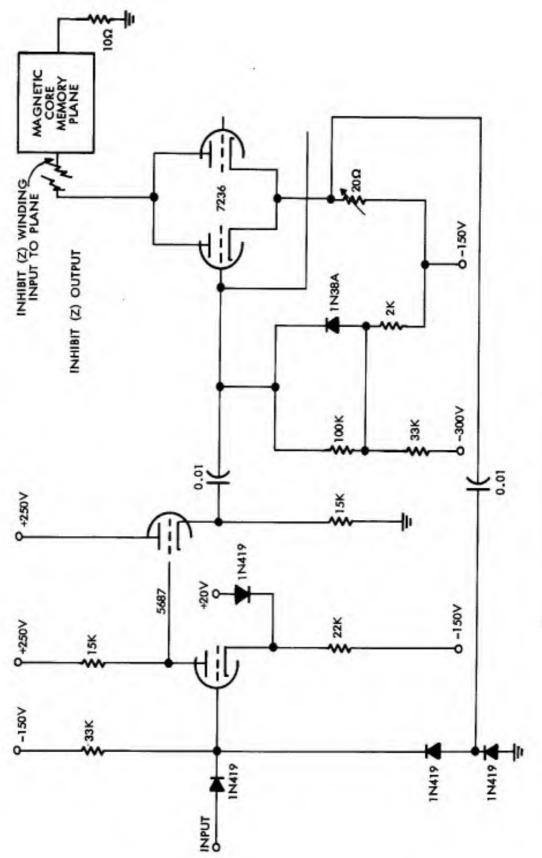

|           | 4.3.1 Main Frame Circuitry                          | 68<br>75 |

### TABLE OF CONTENTS (Cont.)

|              |                                                                                                      | Page |

|--------------|------------------------------------------------------------------------------------------------------|------|

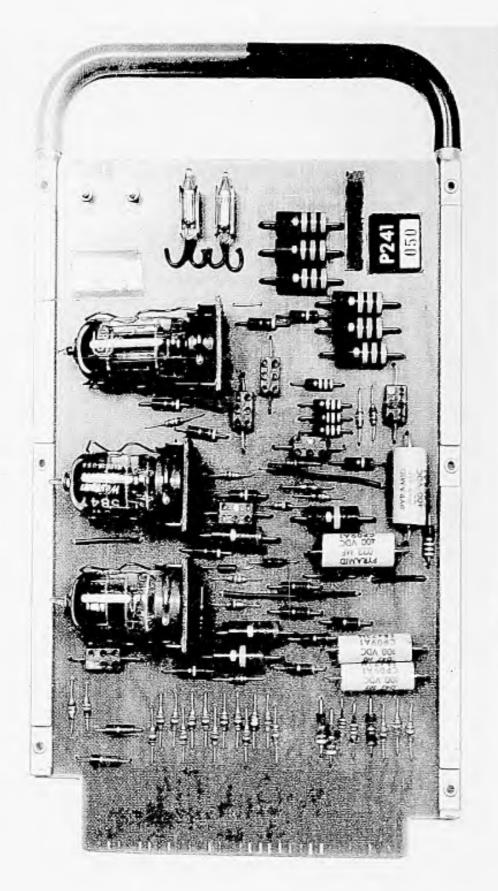

| 4, 4         | Logic Circuit Packaging                                                                              | 90   |

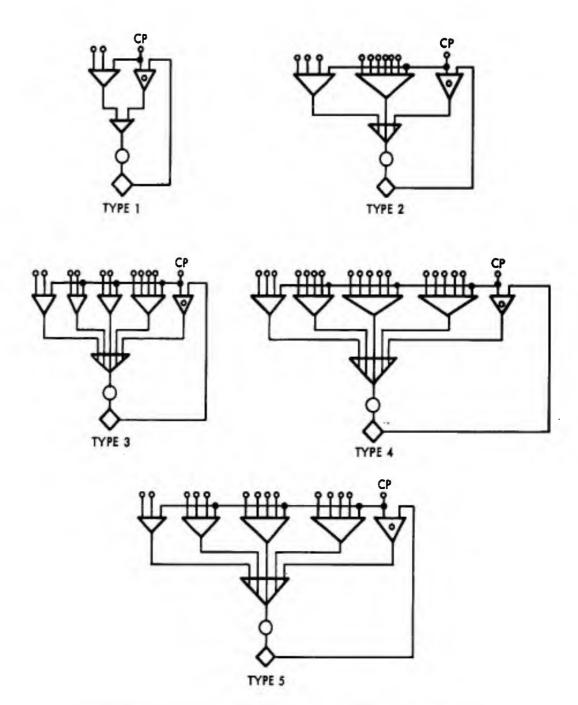

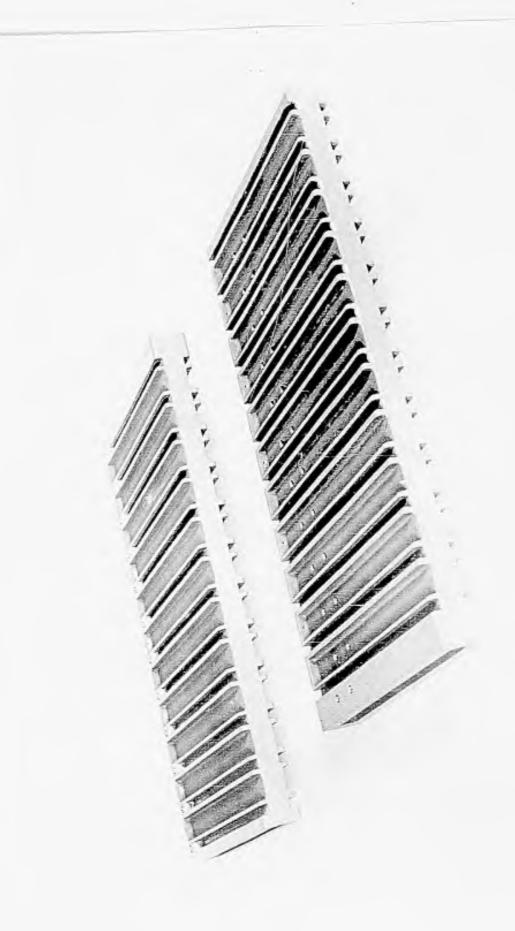

|              | 4. 4. 1 Pulse Amplifier Plug-in Package Assemblies                                                   |      |

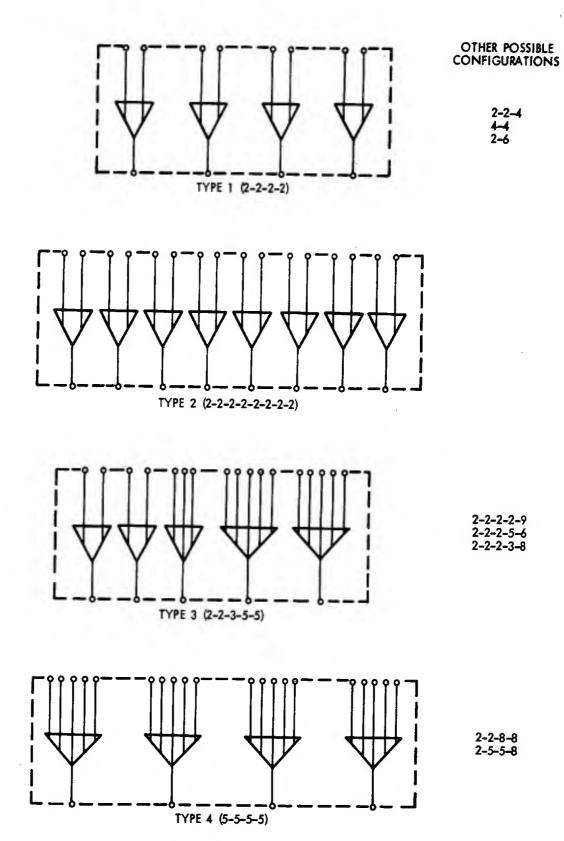

|              | 4. 4. 2 OR Gate Plug-in Package Assemblies                                                           |      |

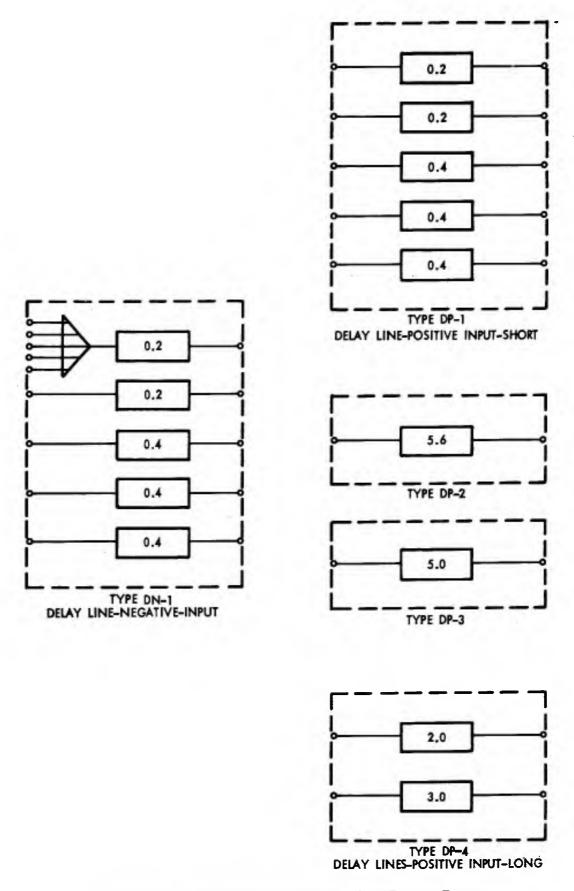

|              | 4. 4. 3 Delay Line Plug-in Package Assemblies                                                        |      |

|              | 4. 4. 4 Plug-in Package Fabrication Problems                                                         | 95   |

|              | 4. 4. 5 Classification of Printed Circuit Plug-in                                                    | 95   |

|              | Package Assemblies                                                                                   | -    |

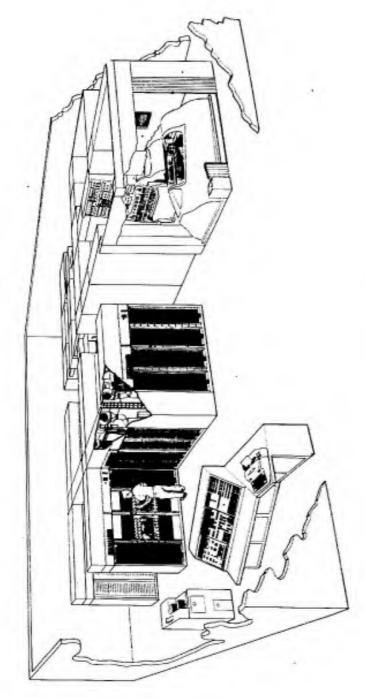

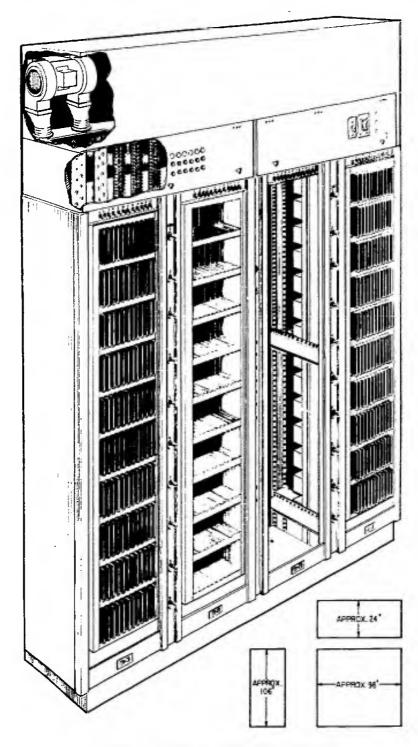

| 4. 5         | Main Frame Development                                                                               | 95   |

|              | 4.5.1 Main Frame Cabinets                                                                            |      |

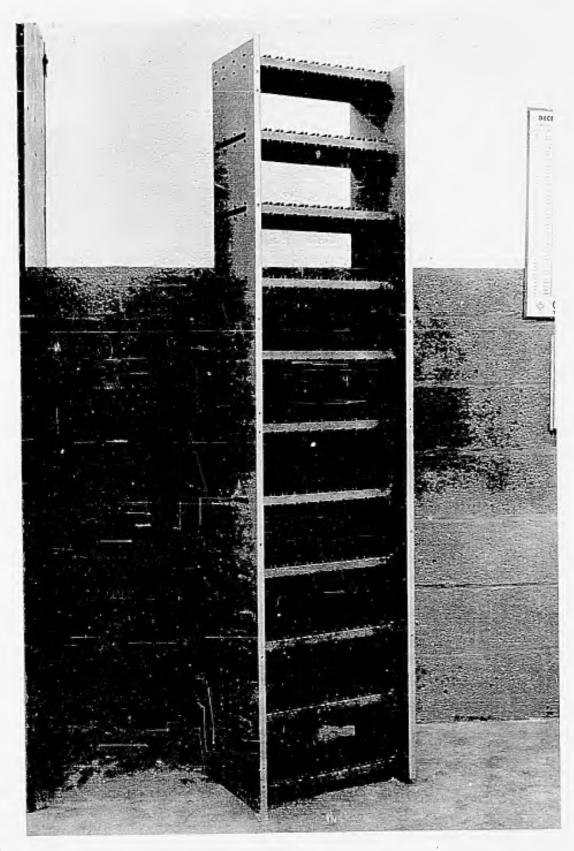

|              | 4.5.2 Package Racks                                                                                  |      |

|              | 4. 5. 3 Rack Layout.                                                                                 |      |

|              | 4. 5. 4 Test System                                                                                  |      |

| 4. 6         | Memory Development                                                                                   |      |

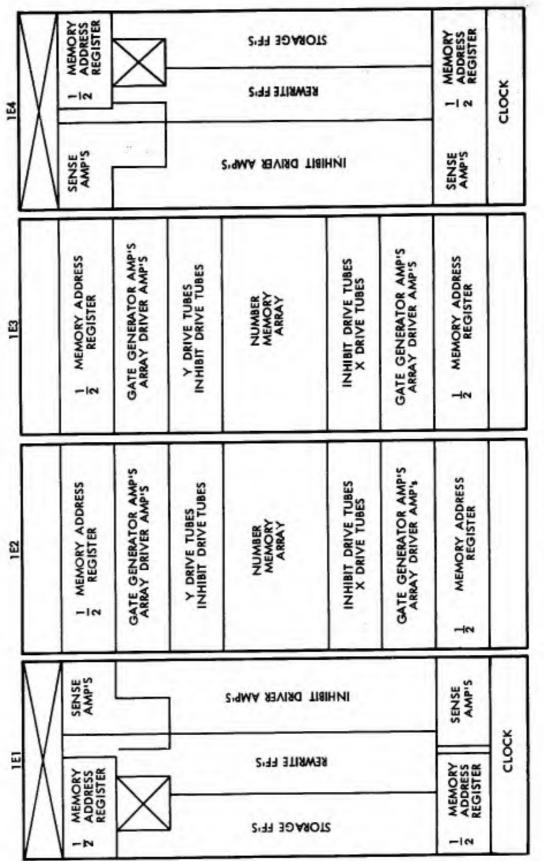

|              | 4.6.1 Memory Design and Development                                                                  |      |

|              | 4.6.2 Memory Planes                                                                                  |      |

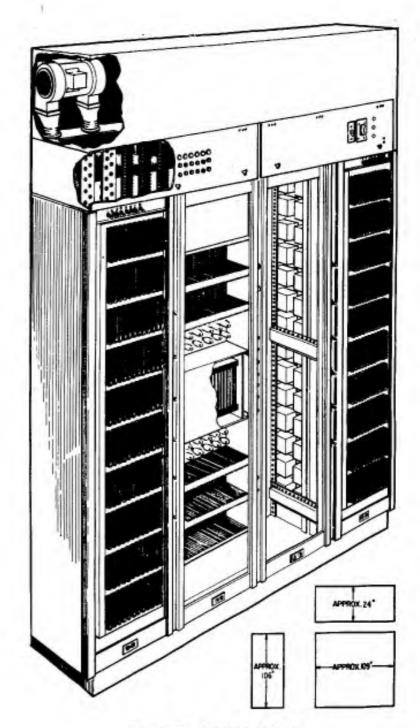

|              | 4.6.3 Memory Unit Cabinet                                                                            | 120  |

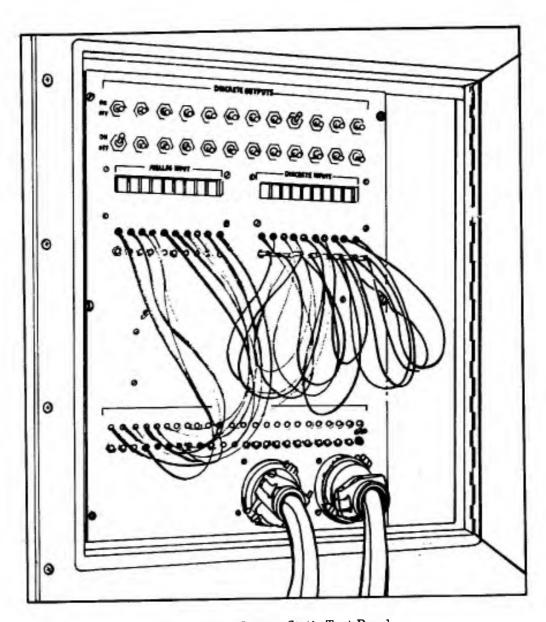

| 4.7          | Input-Output Development                                                                             |      |

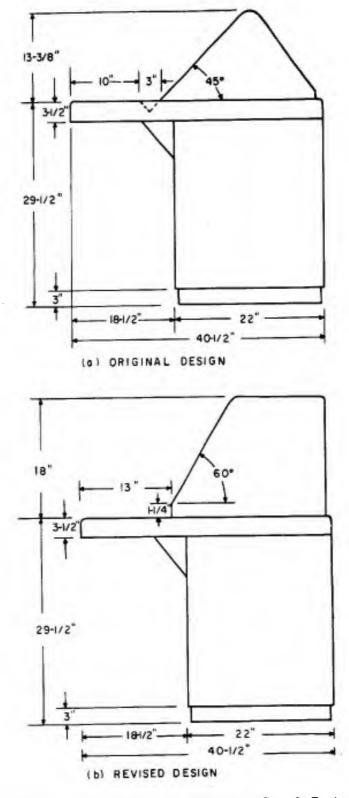

| '            | 4.7.1 Input-Output Unit Cabinet                                                                      | 123  |

|              | 4.7.2 Computer Console                                                                               | 123  |

| 4.8          | Power Supplies and Power Control                                                                     | 1 28 |

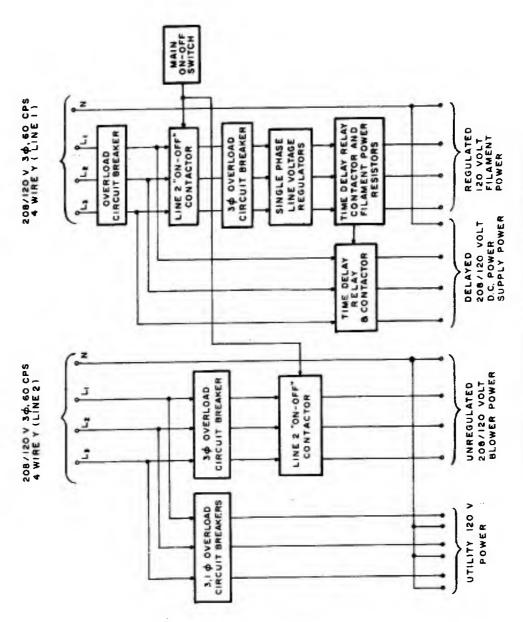

|              | 4. 8. 1 A-C Power                                                                                    | 128  |

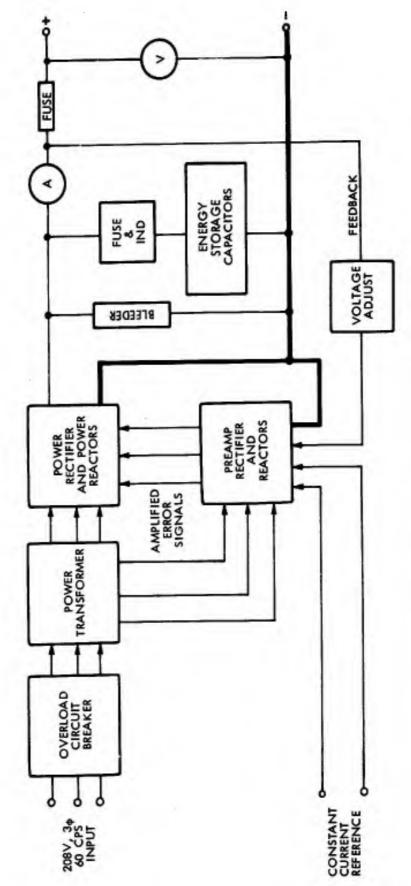

|              | 4.8.2 D-C Power.                                                                                     |      |

|              | 4.8.3 D-C Power Supplies                                                                             |      |

| 4.9          | Computer Unit Testing                                                                                |      |

| 2. 0         | 4.9.1 Arithmetic Unit                                                                                |      |

|              | 4.9.2 Control Unit II                                                                                |      |

|              | 4.9.3 Control Unit I                                                                                 |      |

|              | 4.9.4 Main Frame Test                                                                                |      |

|              | 4.9.5 Memory Unit Test                                                                               |      |

|              | 4.9.6 Input-Output Unit                                                                              |      |

|              | 4.9.7 Computer Console Unit                                                                          |      |

| 4. 10        | Computer System Testing                                                                              |      |

| 4, 11        | Trainer Modification and Static Test                                                                 | 137  |

| 4. 12        | Review                                                                                               |      |

| an conton to |                                                                                                      |      |

| SECTION V    |                                                                                                      |      |

| 5. 1         | Simulation of the UDOFT Computer                                                                     | 140  |

| 5. 2         | Use of Automatic Programming Techniques                                                              | 141  |

| 5. 3         | Checkout and Test                                                                                    |      |

|              | 5.3.1 Trace Facility                                                                                 |      |

|              | 5. 3. 2 Dump Facility                                                                                |      |

| 5 4          |                                                                                                      |      |

| 5.4          | Operational Program Considerations                                                                   |      |

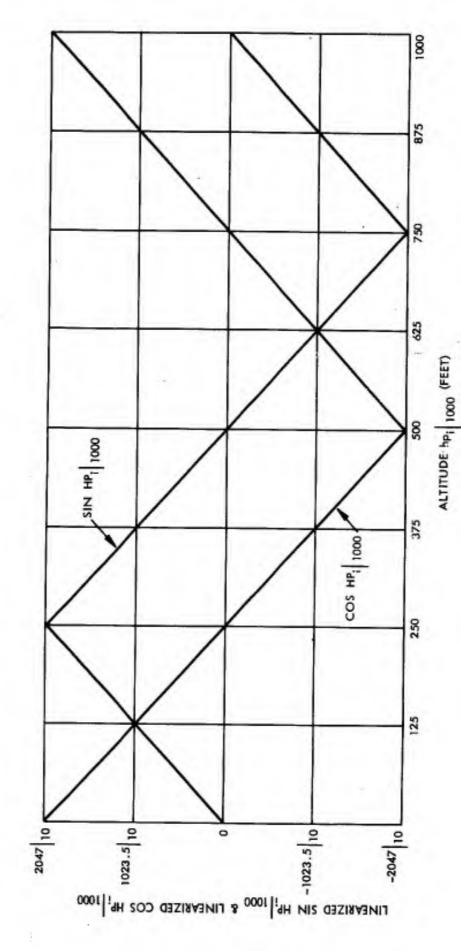

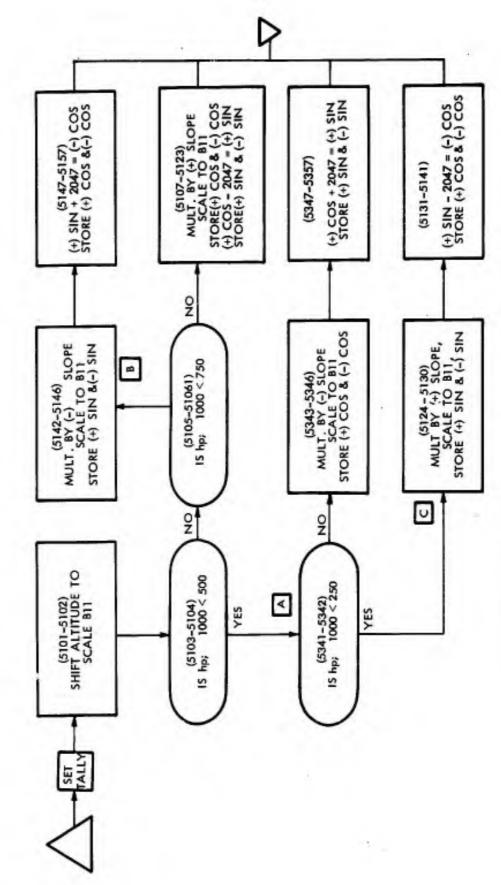

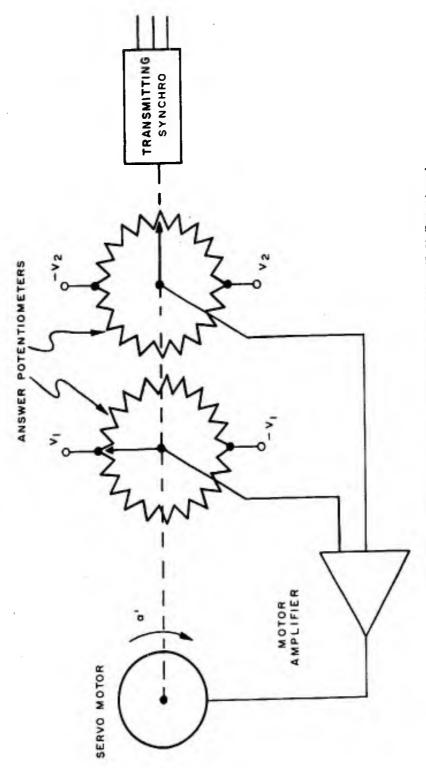

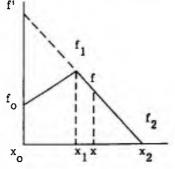

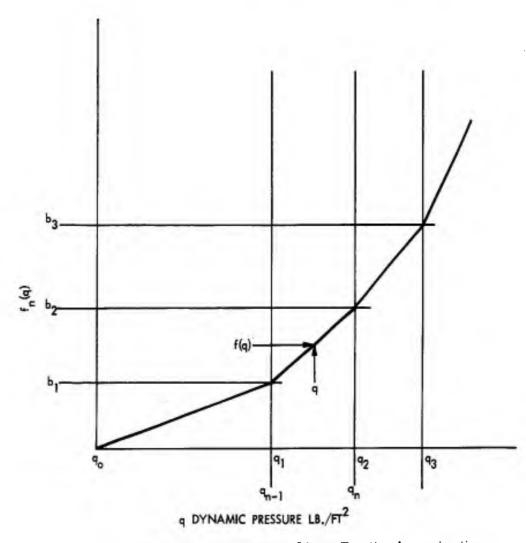

|              | 5. 4. 1 Data Reduction and Function Generation 5. 4. 2 Method of Describing Position and Orientation |      |

|              | 5. 4. 3 Solution Rate                                                                                | 102  |

|              | 5. 4. 3 Solution Rate                                                                                | 167  |

|              | 5. 4. 5 Use of Time in the Operational Program                                                       |      |

|              | 5. 4. 6 Control of Precision in the Operational Program                                              |      |

| 5, 5         | Simulation Program Organization                                                                      |      |

| 0.0          | 5. 5. 1 General Simulation Program Formulation                                                       | 171  |

|              | 5.5.2 Programming Procedures                                                                         |      |

|              |                                                                                                      |      |

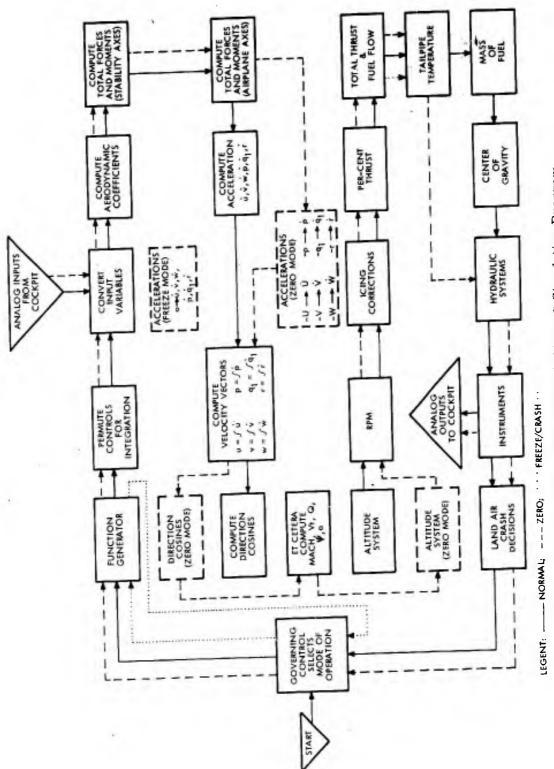

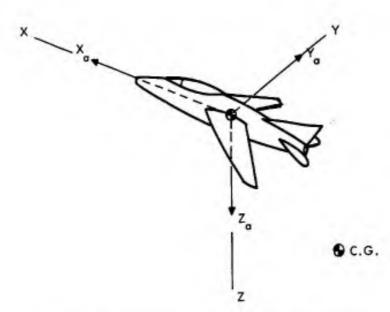

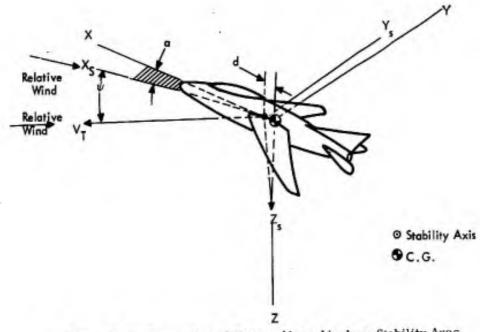

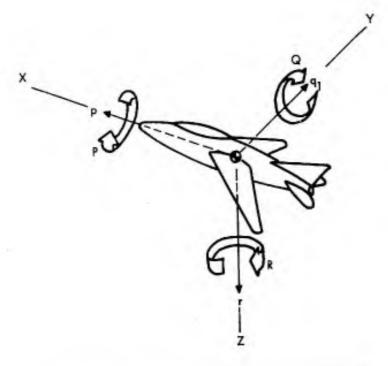

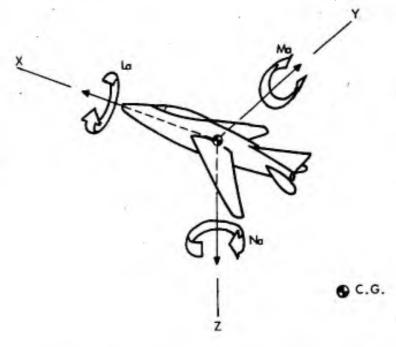

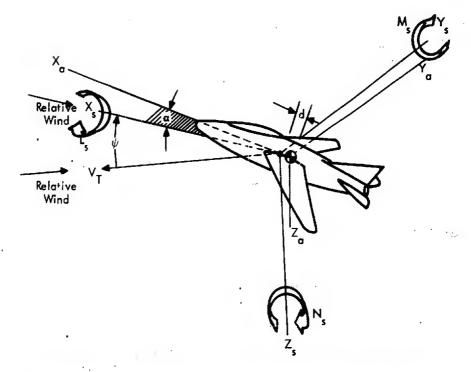

| SECTION V    | I: SIMPLIFIED DESCRIPTION OF THE F-100A SIMULATION                                                   | 175  |

|              | PROGRAM According to Fountiary of Mation (Longitudina) Plane)                                        | 175  |

| 6. 1         | Aerodynamic Equations of Motion (Longitudinal Plane)                                                 |      |

|              | 6.6.1 Longitudinal Acceleration (u)                                                                  | 176  |

|              | 6.1.2 Normal Acceleration (w)                                                                        |      |

| e o          | 6.1.3 Pitching Acceleration (q 1)                                                                    | 191  |

| 6.2          | Program Control                                                                                      | 191  |

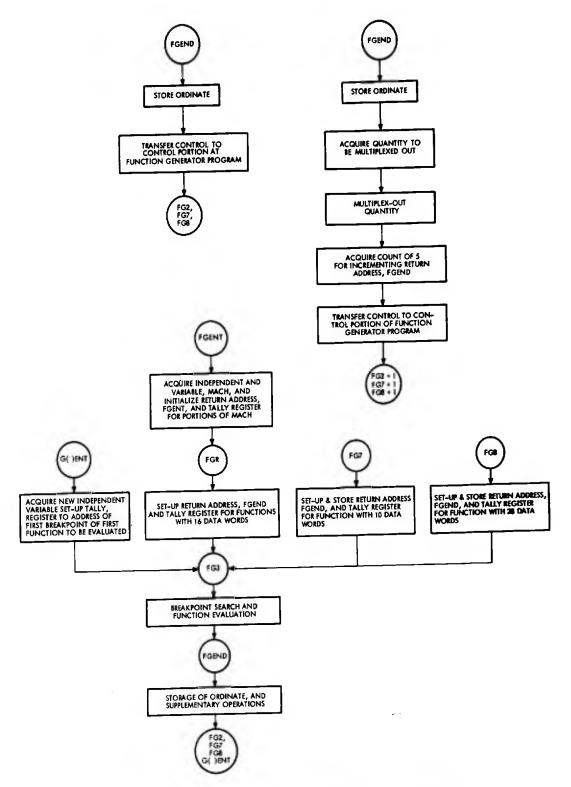

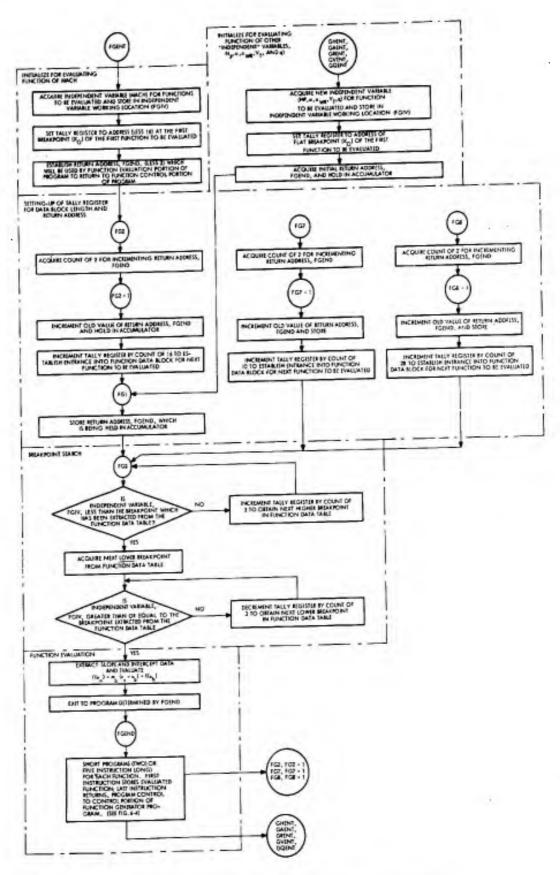

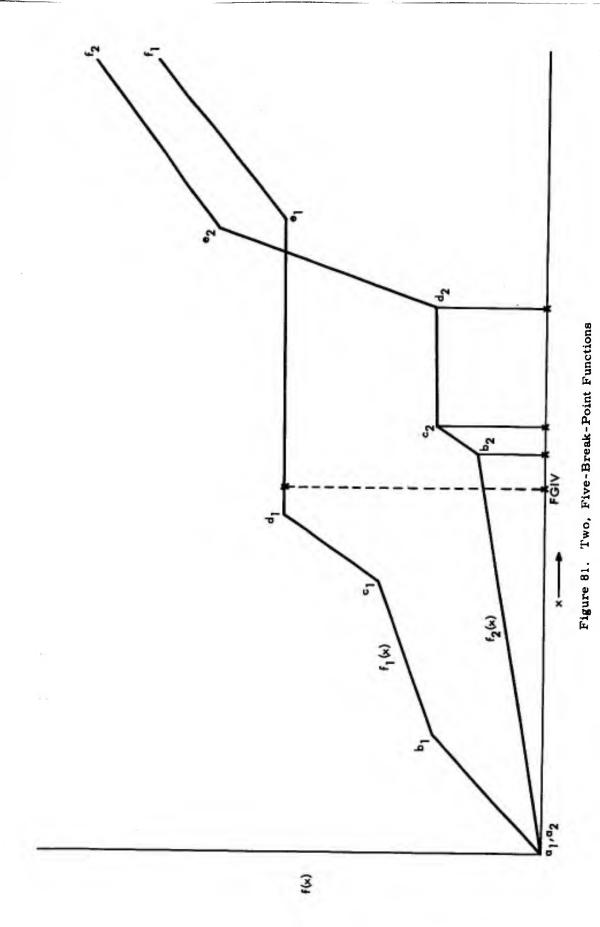

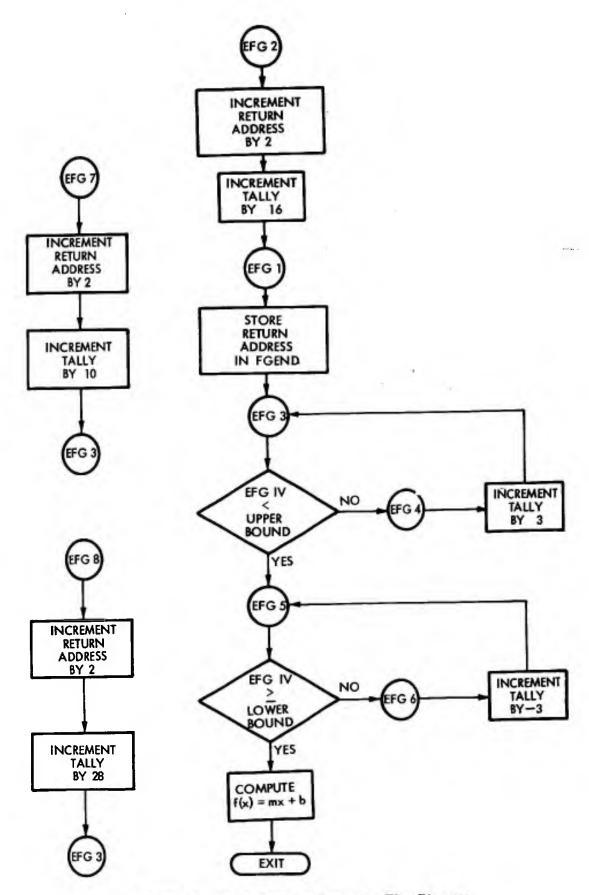

| 6.3          | runction denerator suproutine                                                                        | 101  |

### TABLE OF CONTENTS (Cont.)

| Section    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Page              |

|------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Dection    |                    | Extra Function Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 194               |

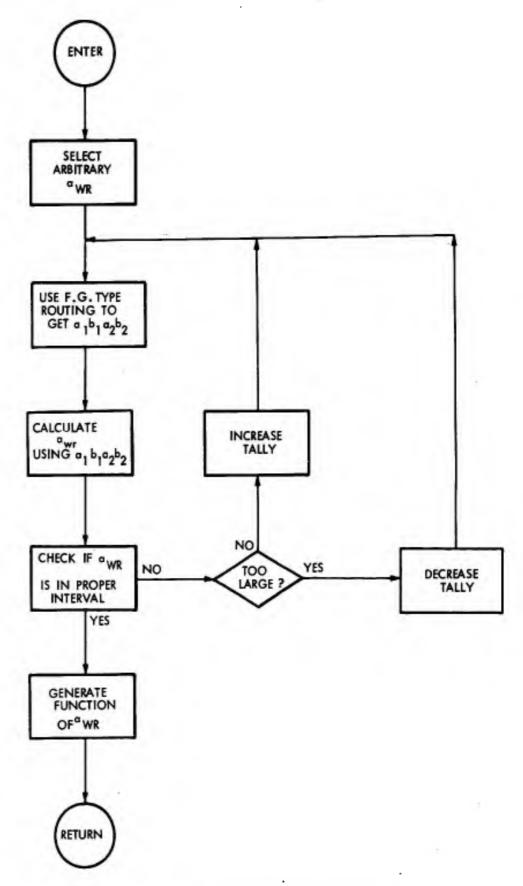

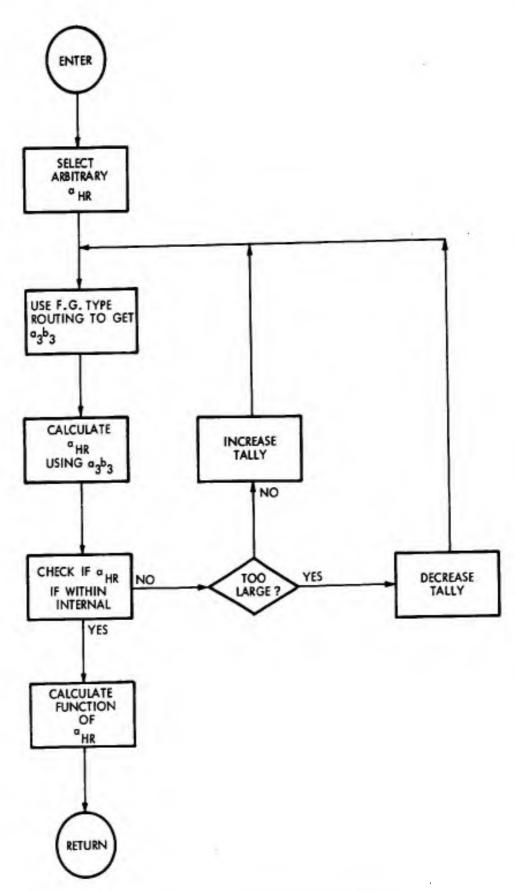

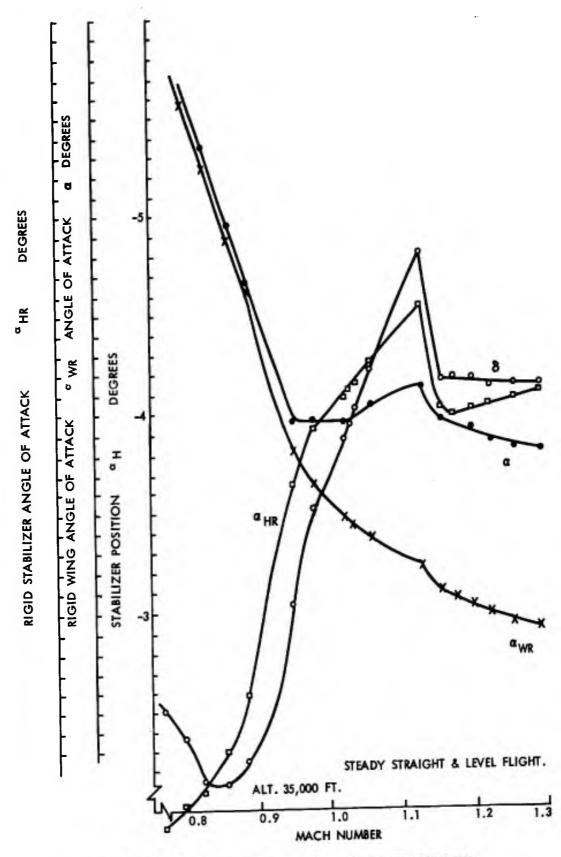

|            | 6.3.1 $6.3.2$      | Calculation of and aHR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 197               |

|            | 6.3.3              | A coursey of Function Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 197<br>197        |

| 6.4        | Conver             | trans Verichles Suprouline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 200               |

| 6.5        | CT 4 - 1 TO        | namic Coefficients Subroutine 'orces and Moments-Stability Axes-Subroutine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 200               |

| 6.6        | makal T            | langer and Moments - Airplane Axes - Duor Outling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 202               |

| 6.7<br>6.8 | A 1                | and and Cubecuting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 202               |

| 6.9        | Velocit            | w Wastong Subroutine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 202<br>202        |

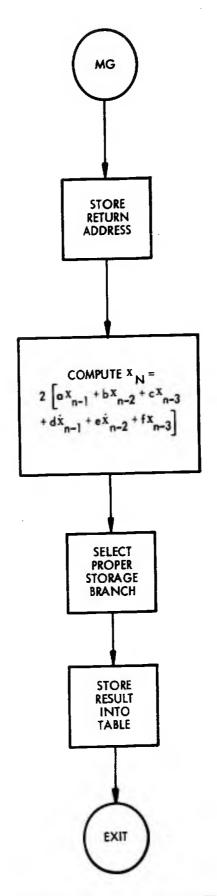

| 0.0        | 6.9.1              | Intographion Subroutine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 202               |

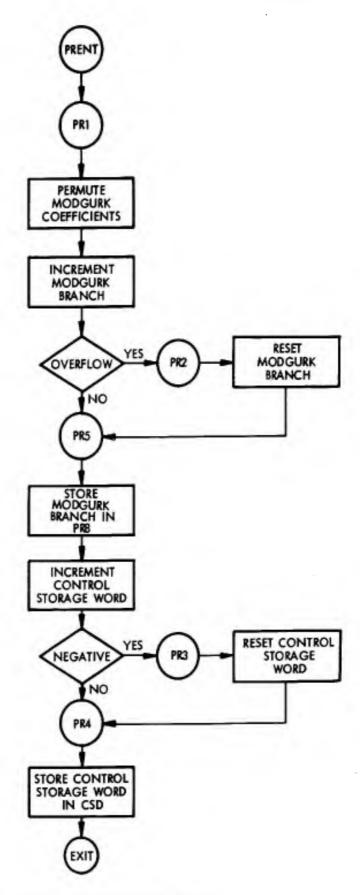

|            | 6.9.2              | Parmute Subroutine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 206               |

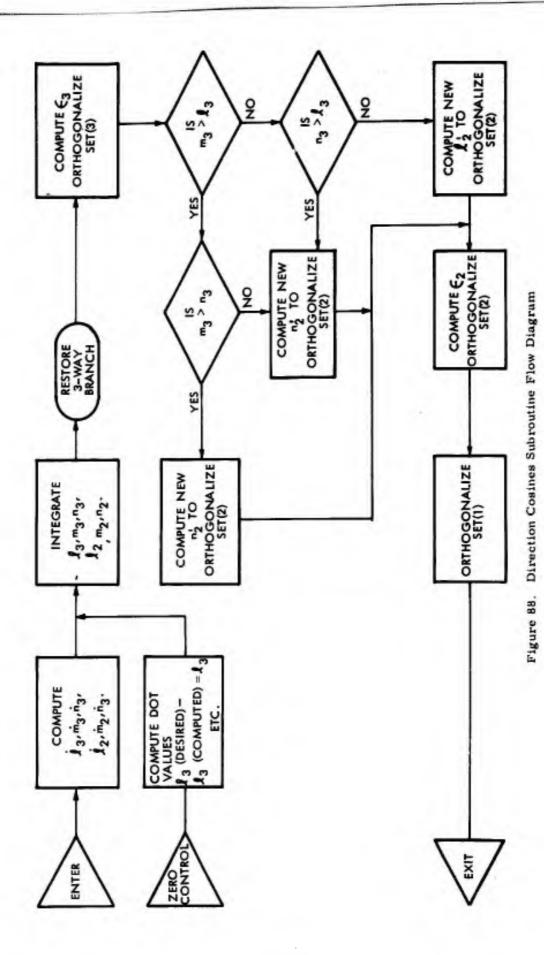

| 6. 10      | Directi            | on Cosines Subroutine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 209               |

| 6.11       |                    | Ptoeters Subrouting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 210               |

|            | 6.11.1<br>6.11.2   | Instruments Subroutine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 210               |

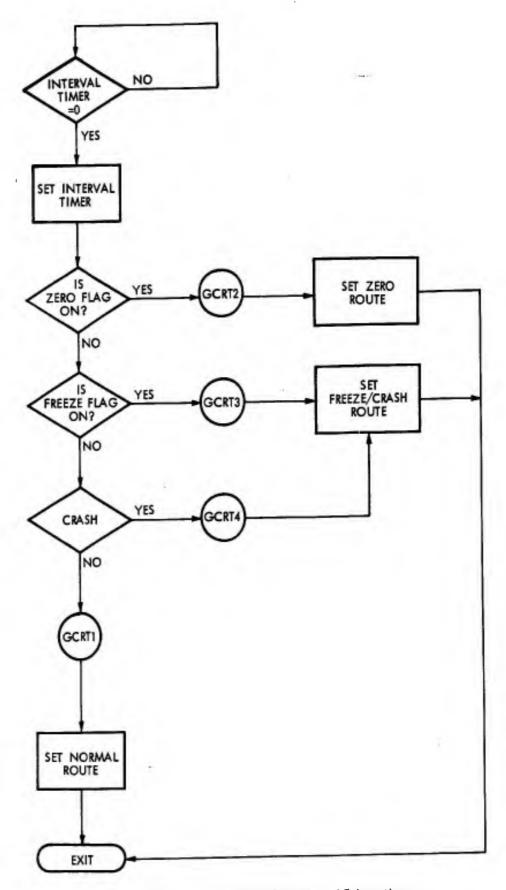

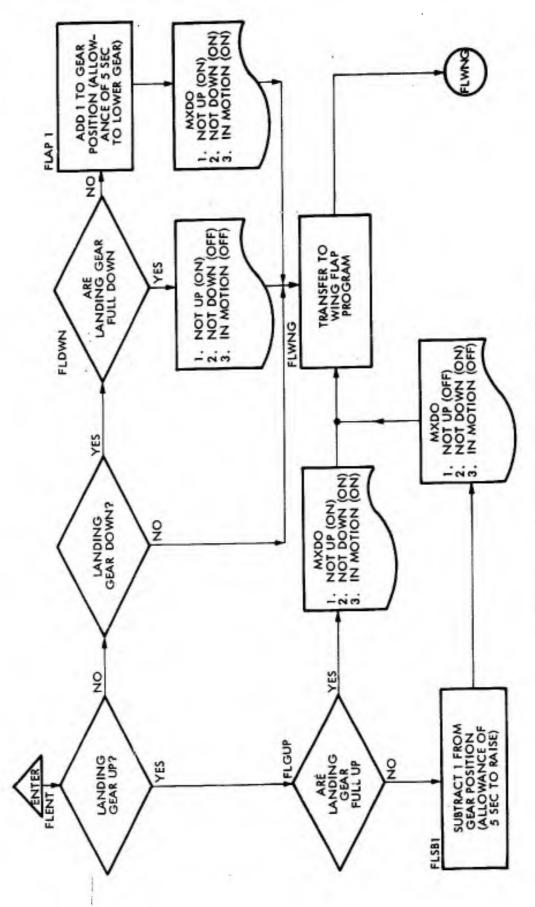

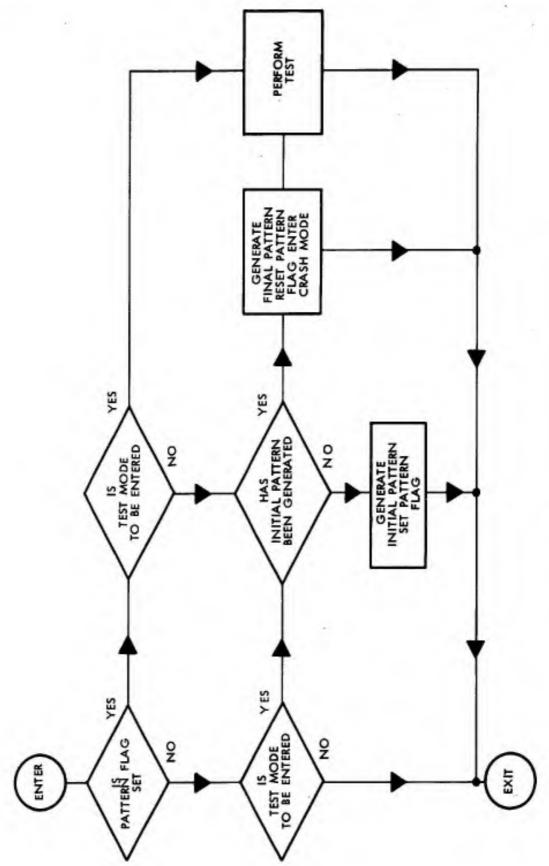

| 6.12       | Decisio            | ons Subroutine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 212               |

|            |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |

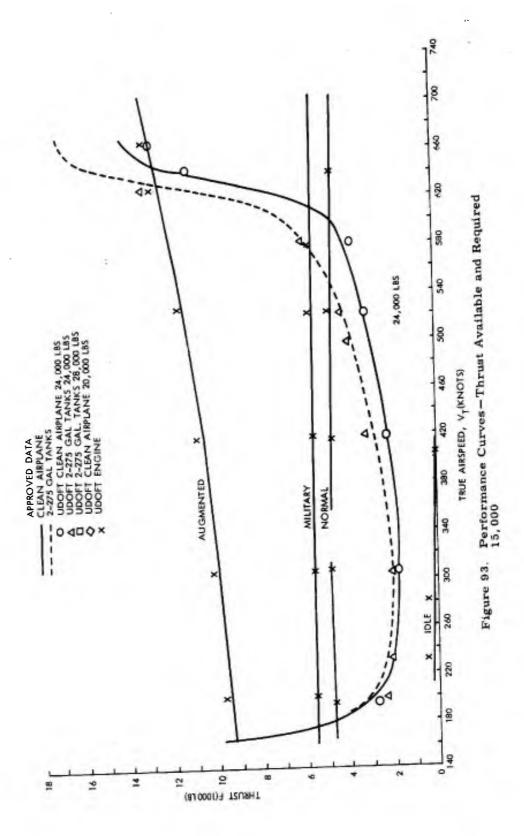

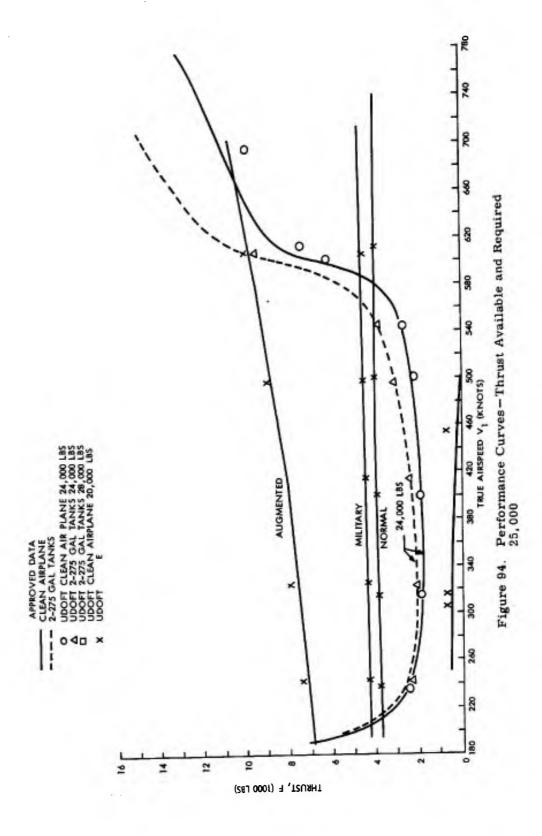

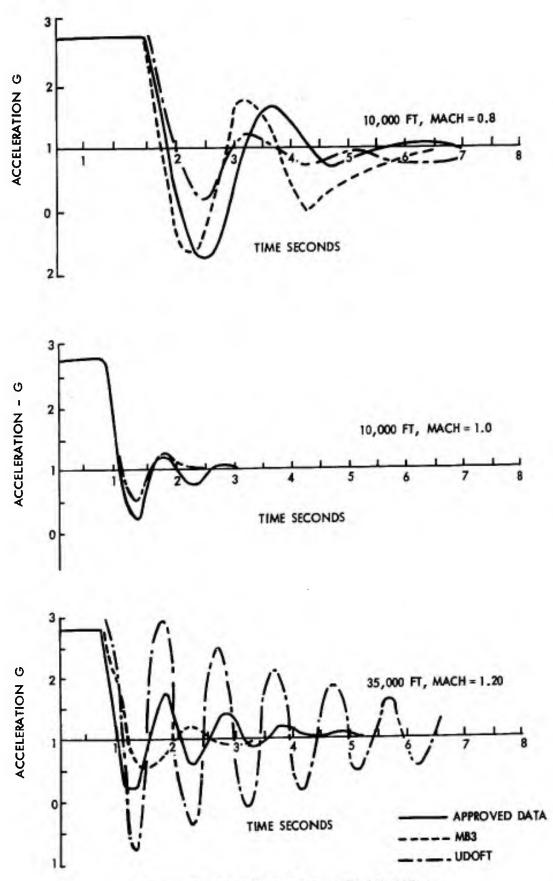

| SECTION    | VII: TE            | CHNIQUES FOR ESTABLISHING THE PERFORMANCE THE SIMULATED F-100A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 216               |

| F/ 1       | OF<br>Cresis!      | Togt Controls                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 216               |

| 7.1        | 7. 1. 1            | 7 and 091 W/T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 216               |

|            | 7. 1. 2            | Thusand 201 H/T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $\frac{217}{217}$ |

|            | 7. 1. 3            | Altitude Increase/Decrease: 421,WI/43LWI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                   |

|            | 7.1.4              | A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |

|            | 7. 1. 5            | Altitude Lock; 47LWT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 219               |

|            | 7.1.6              | ar The 1 Demission: 731 WT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 210               |

|            | 7. 1. 7<br>7. 1. 8 | Thus Ainched Lock 76LWT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 200               |

|            | 7 1 0              | Contag of Gravity Lock: [[LWI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                   |

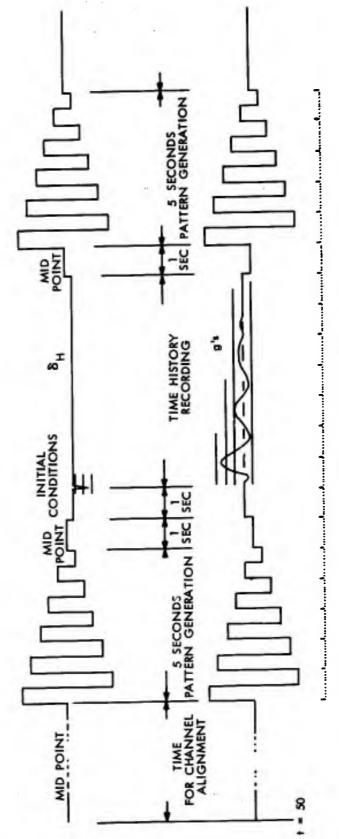

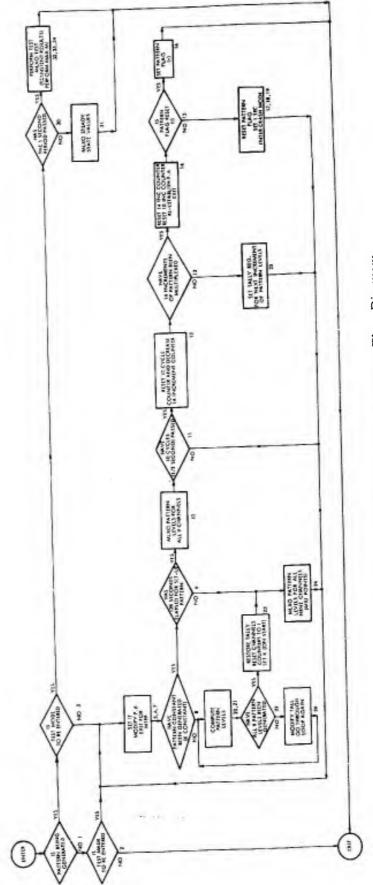

| 7.2        | Accum              | unlastion and Extraction of Test Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                   |